一种12位500 MS/s电流舵DAC的设计

戴澜 闫强强

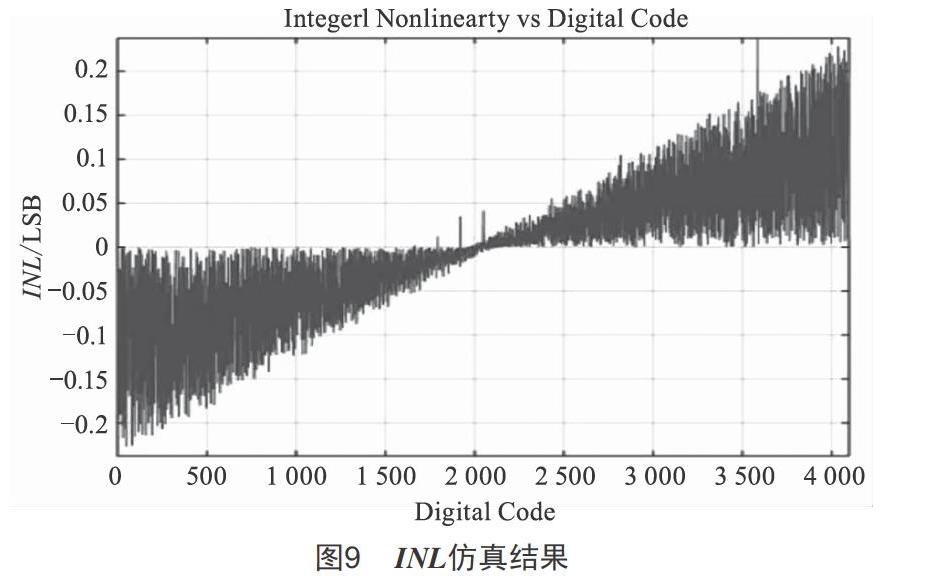

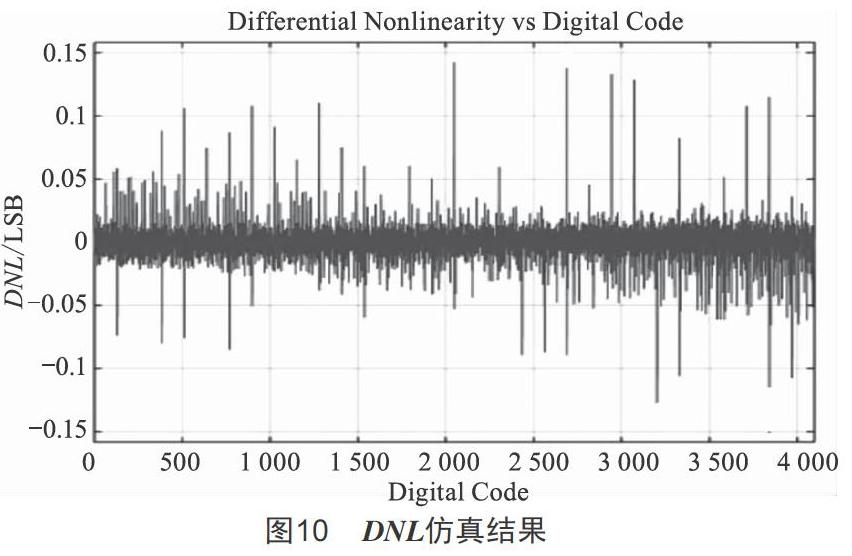

摘 要:基于中芯国际SMIC0.18 μm标准CMOS 1P6M工艺,在Cadence EDA平台下设计完成了一款12位、采样率500 MHz的电流舵DAC。电路主体结构采用5+3+4的分段方式,其中模拟部分采用3.3 V电源供电,数字部分采用1.8 V供电,满量程电流20 mA,单端负载为25 Ω,在时钟信号500 MHz、输入信号1.586 914 MHz的条件下,测得SFDR为91 dB,电路的INL为±0.25 LSB、DNL为±0.15 LSB,整体功耗为75.6 mW。

关键词:电流舵DAC;带隙基准;电流源;SFDR

0 引言

数模转换器,简称DAC,顾名思义,它是一种将数字信号转换为模拟信号的芯片,承担着数字域与模拟域桥梁的作用,其重要性不言而喻。近几年,随着5G通信的兴起、4k超清视屏、超高速实时监控、高速雷达,物联网等领域快速发展,对数模转换器的要求越来越高,集中体现在两个方面:一是高速,二是高精度。例如,在5G基站的建设之中,就需要高速高精度的DAC负责将基带数字信号转化为模拟信号,接着由载波信号调制成高频信号,最后由功率放大器发射出去。在基站的设计中,DAC的性能至关重要,正是有了高速、高精度、宽范围的DAC,才能形成各种复杂的波形。

在众多DAC类型中,电流舵DAC有着与生俱来的高速高精度特点,正是在这种应用背景与需求下,设计一款优秀的电流舵DAC就显得很有必要。

1 电流舵DAC的整体架构

本文设计的12 bit/500 MHz电流舵DAC的整体架构如图1所示,主体采用了5+3+4的分段结构,即高5位和中间3位采用温度计编码,低4位采用二进制编码,满量程输出电流为20 mA,单端负载为25 Ω,单端输出摆幅为0.5 V,差分输出摆幅为1 V,主要电路模块有带隙基准、V-I转换电路、电流源阵列、输入寄存器、二进制码转温度计码电路、锁存低交叉点开关电流源驱动电路等。

图1的工作过程如下:时钟CLK频率为500 MHz,输入的12位数字码先经过输入寄存器同步,同步后的12位数字信号被分成3路作相应处理,高5位和中间3位二进制信号经过译码电路被译成31路和7路温度计码信号,低4位二进制信号经过buffer延时即可,处理后的42路信号经过低交叉点开关电流源驱动电路后转换为84路开关驱动信号,最后去控制相应权重差分开关的开通与关断,于是,不同权重的电流源将根据输入数字码的不同,流过相应的权重差分开关,最后流经负载产生电压输出。

2 关键电路设计与仿真

2.1 带隙基准的设计与仿真

带隙基准是电流舵DAC中的关键电路,本文设计的基准电路及仿真结果如图2、图3所示。从图中可以看出,温度从-40 ℃增加到125 ℃时,带隙电压变化约为2 mV,由此可以计算出基准电压的温度系数为10.4×10-6。

2.2 电流源阵列偏置电路的设计

图4是电流源阵列的偏置电路,R0、R1为外接精密电阻,M3、M5构成低压共源共栅电流源,共栅管M3的偏置由M2、M4组成的电流源提供,通过调节R0、R1的大小,可以将VCS和VCAS偏置在合适的电压。图4所设计的偏置电路具有高输出阻抗、高电源抑制比、宽摆幅的特点。

2.3 单位开关电流源的设计

开关电流源阵列是电流舵DAC中最重要的电路,本文设计的单位开关电流源电路如图5所示。设计单位开关电流源主要考虑失配和有限的输出阻抗。式(1)和(2)反映了单位电流源失配的相对方差与电流源面积的关系[1]。

σ2

=2

2=Aβ2+

(1)

≤ (2)

式中,Aβ、A是与工艺有关的常数;C与芯片的良率有关[2],通常选取C=2.8。

低频下,电流舵DAC的INL对单位电流源的输出阻抗有如下要求[3]:

INL= (3)

式中,Iunit、Runit为单位电流源的电流和输出阻抗;RL为负载;N为单位电流源的个数。

高频下,电流舵DAC的SFDR与单位电流源的输出阻抗有如下关系[3]:

SFDR=40lg Rratio-12(N-2) (4)

式中,Rratio=Runit/RL;N为分辨率。

本设计中,选取电流源的过驱动电压为500 mV,通常要求INL<0.5 LSB,SFDR>70 dB,结合式(1)~(4),可以确定图5中各MOS管的尺寸。图6为单位开关电流源的输出阻抗仿真,可以看出,低频下输出阻抗约为13.5 GΩ,高频下输出阻抗下降到了1.49 MΩ。

2.4 带锁存功能的开关电流源驱动电路设计

为了防止图5中的M3和M4同时关断[4],本文设计了一种带锁存功能的低交叉点开关驱动电路,如图7所示,通过调整传输门TG1和反相器INV1的PMOS管和NMOS管的尺寸,就可以调整信号对反相器INV2和INV3栅极的充放电时间,从而达到降低信号交叉点位置的效果。

3 仿真结果

本设计基于SMIC0.18 μm标准CMOS 1P6M工艺实现,电路整体版图如图8所示,输入全码斜波信号,输出对应每一个输入采样4 096个点,利用MATLAB仿真电流舵DAC的静态性能,得到图9、图10所示结果,从图中可以看出,INL在±0.25 LSB内,DNL在±0.15 LSB内。在时钟信号500 MHz、输入信号1.586 914 MHz的条件下,对输出信号采样4 096个点作频谱分析,得到图11所示结果,从图中可以看出SFDR为91 dB。表1是本设计的整体仿真结果,可以看出本设计在静态性能和动态性能方面都达到了预期的结果。

4 结语

电流舵DAC广泛应用在各种电子设备及高速接口电路中,本文基于SMIC0.18 μm标准CMOS 1P6M工艺设计实现了一款12 bit/500 MHz的电流舵DAC,通过仿真发现,INL在±0.25 LSB内,DNL在±0.15 LSB内,在采样率500 MHz、输入信号1.586 914 MHz的条件下,SFDR达到了91 dB,功耗为75.6 mW,电路整体性能良好。

[参考文献]

[1] PELGROM M J M,DUINMAIJER A C J,WELBERS A P G.Match-

ing properties ofMOS transistors[J].IEEE Journal of Solid-State Circuits,1989,24(5):1433-1439.

[2] VAN DEN BOSCH A,STEYAERT M,SANSEN W.An accurate stati-

stical yield model for CMOS current-steering D/A converters[C]// 2000 IEEE International Symposium on Circuits and Systems (ISCAS),2000:105-108.

[3] 湯华莲.高速高精度电流舵型数模转换器关键技术研究[D].西安:西安电子科技大学,2013.

[4] 朱樟明,杨银堂,刘莉,等.基于高速电流舵数/模转换器动态性能的电流开关驱动器[J].西安电子科技大学学报(自然科学版),2004,31(5):701-704.

收稿日期:2020-04-01

作者简介:戴澜(1975—),男,湖南邵阳人,博士,教授,研究方向:大规模集成电路设计。

闫强强(1992—),男,甘肃天水人,在读硕士,研究方向:大规模集成电路设计。