基于ARM Cortex-A9 MPCore嵌入式多核操作系统内核研究与实现

吴利生

摘要:随着芯片技术的飞速发展,与过去几年相比,多核处理器的售价目前已非常便宜,在linux等平台的支持之下,多核芯片在人们日常的生产和生活之中应用已经非常普遍。但是多核处理器操作系统原理的研究相比单核处理器就显得复杂,本文分析了嵌入式操作系统的理论和硬件,提出了基于Zynq-7000的嵌入式多核操作系统设计与实现办法,以供参考。

关键词:ARM Cortex-A9 MPCore;嵌入式;性能研究

中图分类号:TP316 文献标识码:A 文章编号:1007-9416(2020)03-0134-02

1 嵌入式操作系统的理论和硬件分析

ARM Cortex-A9 MPCore嵌入式多核操作系统的实现必须要通过理论和硬件进行分析,本小节的理论方面包括对称多处理器架构的介绍,在硬件方面则详细分析了ARM Cortex-A9 MPCore架构芯片的主要的组成结构[1]。

1.1 架构理论介绍

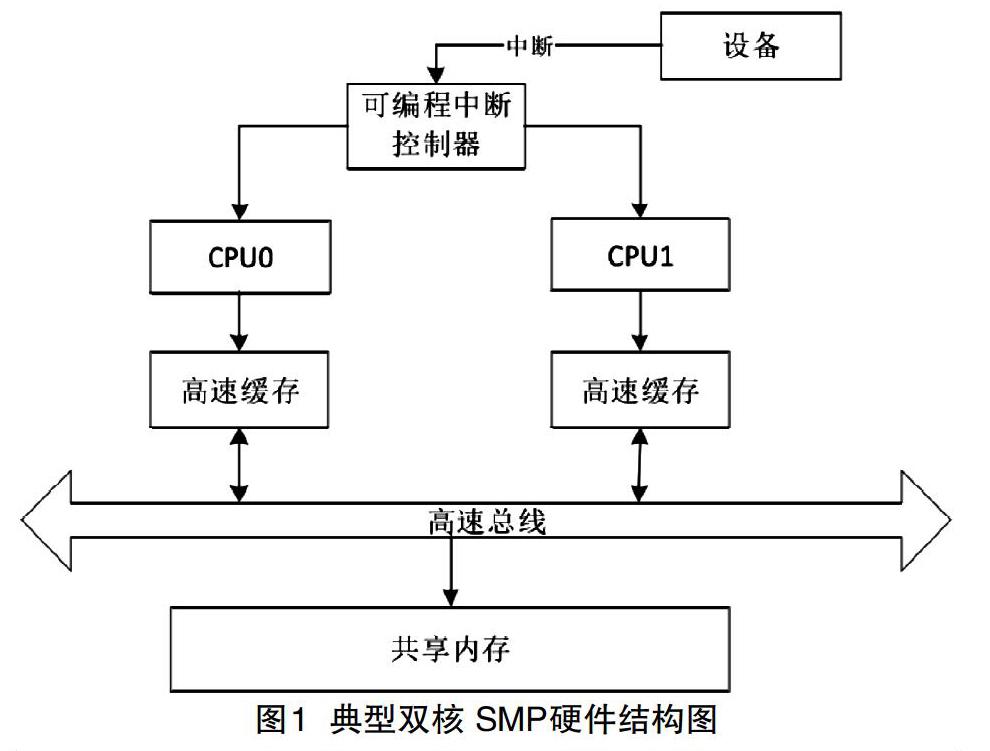

本次研究的芯片属于典型的对称性多核架构,也就是一个芯片之内集成了许多个相同的中央处理器(CPU),且各个CPU之间有着相等的优先级,都具备同样的内存,且对外设资源的访问权限都相等。多核处理器中的CPU与集中的存储器以及I/O总线相互连接,这样的连接可以使多核处理器可以同时访问一个相同的物理存储器,这样的内存结构被称之为一致内存访问结构(UMA)。图1就展示了一个典型的双核对称性架构(SMP),通过该图我们可以看到两个CPU通过与同一个I/O总线相连实现对共享物理内存的范文相连来访问相同的物理内存,从硬件结构图中还可以看出可以通过中控制器实现设备的中断[2]。

本研究中发现由于内存的限制,在SMP系统中CPU的数量为2~4时,利用率最佳。在本研究中应用的还有:(1)控制主、次级CPU休眠、检查以及初始化的多核系统启动技术;(2)实现多数支持SMP选择每个CPU维护私有的就绪任务队列的任务调度技术;(3)控制多核处理器实现核间中断的中断处理技术;(4)保证完整总线交易之中完成CPU对内存中某一数据的读取、修改以及回写而不被其他CPU打扰的互斥同步技术。

1.2 硬件分析

为了能够在保证足够的多核文档数量的情况下对本实验所选取芯片实施开放硬件调试,所以选取Zynq-7000平台作为硬件研究对象。本研究所选取的每一个A9处理器都能够在相同时间或者某段时间处理两条指令,实验中的ARM Cortex A9处理器实现了ARM v7-A结构,这样可以确保整个架构获得完整的虚拟存储支持,可设置执行16位以及32位的Thumb代码指令,除此之外还有两种解决办法,即:(1)执行32位的ARM代码指令;(2)在Jazelle的状态之下使用8位Java代码指令。在本文设计的硬件系统中还包括了通用中断控制器、scu以及定时器等部件,具体的结构图如图2所示。

2 基于Zynq-7000的嵌入式多核操作系统设计与实现

2.1 多核启动模块

本设计中操作系统之中启动的绝大部分工作都是通过主核串行来进行的,在合适的时机会发出指令,将次级核激活,达到主核和次核同时工作的目的。具体步骤如下:第一步是完成主核CPU、板级以及操作系统内核三者的初始化,初始化完成之后主核就会发出指令并准备启动次级核,在一系列的初始化工作的最终目的就是实现次级核启动地址玩出完成装载;第二部就是进行上锁,主要的目的就是为了实现主核、次核在同一应用场景下实现任务的调度,主要是实现方法就是设计主核初始化全局自旋锁smp_lock进行上锁,这个模块中的核心代码如下:

SECONDARY_CORES_START_FUNC_REG = (unsigned long) OS_secondary_cpu_start;

os_spin_init_lock(&smp_lock);

第三步就是实现次级核的初始化,当主核执行完激活的指令之后,次级核接收到主核激活指令,就会立刻退出休眠状态,并读取和验证相关的验证地址,验证合法之后,就会执行次级核的启动函数的代码。由于在次级核进行初始化的过程中要牵扯到C语言的读取和调入,因此再次之前还需要汇编函数,使目前状态的处理器处于一个SVC模式并设置临时堆栈[3]。

2.2 核间通信模块

核间通信属于多核系统之中特有且又十分重要的一个模块,借助此模块就能够实现不同处理器之间任务和信息的交互。核间通信在实现上可以划分为两部,分别是发送与接收处理。同样的这些信息由不同处理器发送也可以分为两个部分,也即是通信信息写入内存以及中断发送两部分。在发送中断前必须要向目标CPU的通信命令变量存储通信信息,这一部分实现的具体的数据代码在下面给出:

typedef struct{

os_spinlock lock;

CPU_INT32U ipi_cmd;

OS_TCB *tcb;

void *data;

}os_ipi_cmd;

因為此次研究使用了中断对应所有核间通信的命令,所以在接收到核间通信中断之后,此核核间中断处理函数就要进一步读取相关函数,并依照这些来执行相应命令的函数[4]。

2.3 任务管理模块

在多核的系统之中,因为任务能够在主核以及次核之上分别运行,因此任务准备、准备完成以及运行状态上就拥有了所属CPU的属性。本研究中的Per-CPU能够达到每个核均衡负荷的效果,队列模型因为分配了CPU私有队列在每以个模型之中,所以能够实现并行调度的目的,而且在一个任务时间里,更倾向在单独的CPU上运行,这样可以使CPU上的cache热度得到充分的利用。本研究中可以通过两种方式实现一个CPU上任务对另一个CPU上的任务的一些操作,比如准备完成、挂起、优先级上调或下调等。这里有两种方法可以实现,第一种解决策略就是允许直接进行操作。由于多核共享主存储器,所以该策略是可行的是可以实现的。第二种解决策略就是该CPU不对本CPU之外的所属任务进行调度和管理,而是通过发送信息的方式由任务所属COU去进行处理和操作,采取该办法处理时则要借助核间通信机制[5]。

3 結语

文章首先介绍了对称多处理器架构,并对所选取的Zynq-7000开发平台进行额硬件分析。然后份多核启动模块、核间通信模块以及任务管理模块三个部分阐述了基于Zynq-7000的嵌入式多核操作系统设计与实现的具体办法,通过一些列模块的整合实现了多核操作系统设计与实现。

参考文献

[1] 张洋,虞志益.引领多核处理器创新之路[J].中国发明与专利,2018(01):117-118.

[2] 羽路.多核处理器悄然崛起[J].集成电路应用,2019(05):22-24.

[3] 多核处理器强调多任务并行处理[J].每周电脑报,2018(35):86.

[4] 冯磊.多核处理器的数量裸奔[J].信息系统工程,2016(11):82-85.

[5] 张浩,兰峰.多核处理器基本原理及其在汽车领域中应用的展望[J].汽车科技,2017(03):37-41.

Abstract:With the rapid development of chip technology, compared with the past few years, the price of multi-core processor has been very cheap. Under the support of Linux and other platforms, multi-core chip has been widely used in people's daily production and life. However, the principle of multi-core processor operating system is more complex than that of single-core processor. Firstly, this paper introduces the theory of embedded operating system and the hardware used in this experiment, and analyzes the specific methods of multi-core operation in three modules for reference.

Key words:ARM Cortex-A9 MPCore; embedded; performance research