一种基于SoC技术的小型化复合检测方法研究

曹建锋,殷 翔,张 帅,杨 幸,黄 磊

(上海机电工程研究所,上海 201109)

0 引言

在嵌入式控制领域,常用的检测一般分为数字量(开关量)检测、模拟量检查以及通信检测,目前市场上通用的检测方法大多是通过单一功能的板卡实现的,常见的是基于PCI 总线的外扩板卡实现的检测。这种通过板卡集成的检测方法,导致体积不可避免地增大,制约了检测技术小型化、高集成发展趋势[1]。因此,对检测方法提出了更高的要求。

本文提出基于片上系统(System on Chip,SoC)技术的小型化复合检测方法,该方法具有系统集成度高、体积小、功耗低等优点。它是在一个芯片上实现多种检测功能,通常包括了:检测逻辑模块、微处理器/微控制器CPU 内核模块、数字信号处理器DSP 模块、用户定义逻辑等模块,而这些模块可以根据用户的需求进行IP 核定制来实现。

1 系统介绍

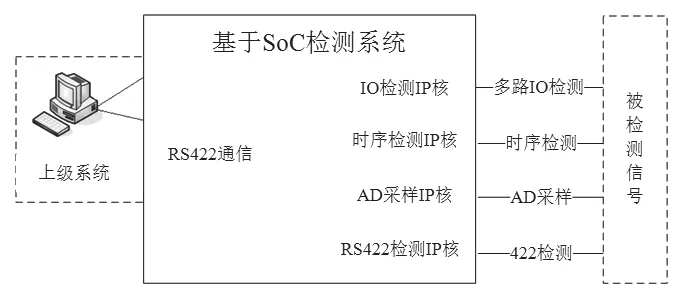

本文从典型的几种检测需求出发,研究基于SOC 技术的复合检测方法。通过设计多种IP(Intellectual Property)[2]核,实现小型化检测系统,如图1 所示。通用IP 核实现多种检测方法在平台芯片内集成,不仅大幅减少检测体积开销,全面提升检测集成化能力,同时该检测方法可增强系统抗电磁干扰能力,通过IP 核实现的检测方法可以快速进行移植,提升开发效率。

图1 系统功能组成框图Fig.1 Block diagram of system functions

图2 串口收发IP核端口定义框图Fig.2 Definition block diagram of serial port transceiver IP core port

2 接口设计

本文选取了常见的串口、IO、AD 3 种典型检测需求,可实现3 种检测和通过串口进行远距离传输,研究分为IP核设计、仿真验证、实物验证3 部分。

2.1 串口IP核

串口是使用率较高的一种通信方式,使用简单、差分信号传输,具有抗干扰、可靠性高的特点,广泛应用在工业控制领域中,可实现数据的高速可靠传输,同时满足实时性要求[4],在进行串口IP 核可分为接收IP 和发送IP 两种,设计时,首先进行端口规划和定义,框图如图2 所示。

端口定义见表1、表2。

2.2 IO采样IP核

该IP 核不仅可以对多路IO 数字信号量检测,同时可以进行相对时序检测,采样速率高、采样路数多,可支持并行采样串行输出结果,如图3 所示,设计了8 组八位带宽的独立IO 检测接口,并设计有通信接口,支持通信应急采集回告。

表1 串口接收IP核端口输入输出表Table 1 Serial port receiving IP core port input and output table

表2 串口发送IP核端口输入输出表Table 2 Serial port sending IP core port input and output table

2.3 AD采样IP核设计

在模拟量采集过程中常用的是AD 检测方法,AD 采样IP 核设计易于仿真验证,节约开发成本和周期[5],端口定义见表3。

3 仿真验证

通过EDA(Mentor)工具设计基于SoC 技术检测模块原理,并通过Modelsim 软件进行仿真分析。

图3 IO检测IP核端口定义框图Fig.3 IO Detection IP and port definition block diagram

表3 AD采样IP核输入输出端口表Table 3 AD Sampling IP core input and output port table

3.1 串口通信时序仿真

串口IP 核又可细分为发送IP 和接收IP 两种。

3.1.1 串口发送IP

利用时序仿真工具对串口发送IP 进行时序仿真验证,如图4、图5 所示。

系统时钟50M,Rst_n 为系统复位信号,低有效,系统复位完成后开始TX 准备发送数据。TX_Enable1 为发送使能信号,TX_Data1 为发送数据缓冲,初始数据位十六进制0x55,如图4 所示。系统复位完成后,发送使能上升沿有效,TX 开始发送数据,发送时序满足串口协议,起始位0,8 位数据位,停止位1。串行数据TX 依次发送0101010101,即0x55。图4 所示发送多个字节时序,分别向外发送0x55,0xaa,波特率仿真的时序图,如图5 所示。

3.1.2 串口接收IP

利用时序仿真工具对串口接收IP 进行时序仿真验证,如图6、图7 所示。

图4 单个字节发送的时序图Fig.4 Timing diagram of single byte transmission

图5 多个字节发送的时序图Fig.5 Timing diagram of sending multiple bytes

图6 单个字节接收的时序图Fig.6 Timing diagram of single byte reception

图7 多个字节接收的时序图Fig.7 Timing diagram of receiving multiple bytes

系统时钟50M,Rst_n 为系统上电复位信号,低有效,RX 为串口数据接收端,Data_1 为数据接收寄存器1。上电后复位结束后,RX 端开始接收数据,Data_1 复位值为0,经过一字节数据接收后,数据变为01111110,即0x7f,多个字节接收的时序图如图7 所示。

图8 AD采样驱动时序图Fig.8 AD sampling drive timing diagram

图9 AD采样初始化设置时序图Fig.9 AD sampling initialization timing diagram

图10 AD采样读写验证时序图Fig.10 AD sampling read and write verification timing diagram

图11 检测方法采样验证界面Fig.11 Detection method sampling verification interface

3.2 多路IO采样仿真

IO 检测、多路时序检测可以归一化为一系列随时间变化的高低电平,在检测模块中设置定时器,以设备开机为时间零点,软件实时采样各个点火通路的IO 端口电平信号变化情况,并将IO 端口电平变化时刻的时间记录下来,形成时序采样数据,具有8 组,每组可检8 路独立IO 的能力。

3.3 多路AD采样仿真

以12 路AD 采样为例,可以对模拟量进行高精度检测,过程分为AD 采样驱动时序、初始化时序以及读写时序验证,如图8 ~图10 所示。

图9 为系统复位后对AD 进行配置,CS 为片选,DIN为输入端,SCLK 为串行时钟,在使片选有效后,在时钟的上升沿一次推送数据,进行对器件初始化。

推 送16 位 初 始 化 码,Ini_Code 为 初 始 化 码,1111100011000001。初始化完成后就可以对器件进行读写,读写时序和初始化操作时序一致,片选CS 有效,在时钟的SCLK 的驱动下读写。

读数据,DOUT 为器件数据输出端,CH_L、CH_H为数据存储寄存器,如图9 所示,所读出的数据为全0,DOUT 与CH_L、CH_H 的内容相符。

4 试验结果分析

基于Labview 环境,搭建了上位机显示软件验证环境,并通过RS422 与检测模块通信。检查模块可将IO 端口检测、RS422 通信、AD 采样结果通过RS422 发送给上位机进行界面显示和人机交互,如图11 所示。

选取IO 输入、AD 输入进行结果验证,如图12 所示,在IO 输入值为0.1V ~5V 信号源激励下,设置阈值大于1V 为高电平1,反之为低电平,实现了IO 检查;在AD 模拟值为4.99V ~5.01V 信号源激励下,AD 采样精度满足使用要求,实现了AD 采样。

该复合检测方法已应用在某型号产品中,用来检测供电电压和电流的时序数据,检测精度满足使用要求,并设计了通信接口,将检测结果通过RS422 通信向上级系统发送,实现了检测小型化、集成化,经验证,该检测方法原理可行。

5 结束语

本文在检测技术小型化、集成化指导下,基于SoC 平台通过IP 核技术研究了一种小型化复合检测方法,该检测方法可满足多种检测需求、通过IP 核可以快速移植,提升了二次开发效率,实现了采集系统的小型化、集成化、智能化。该方法满足符合检测要求,同时该系统定义了电气接口和数字接口协议,可快速嵌入到型号产品中,极大缩短了产品开发、调试时间,同时提高了产品可靠性、电磁兼容性,为后续小型化智能采集设备设计提供了一定的参考价值。