硅基芯片TRL校准件的设计与制作

甄建宇 陈娜

摘 要:为了满足在K/Ka频带下设计硅基芯片电路时对器件模型精确测试的要求,文章分析了实现精确校准的硅基芯片TRL校准技术。根据TRL校准原理设计并制作了相应的校准件,用去嵌入的方式提取了片上电感、电容模型。在20 GHz~ 30 GHz高频应用中,验证了模型的准确性。实际测试结果表明该校准件达到了预期效果,仿真值与实测值拟合一致性好。

关键词:硅基芯片;TRL校准技术;去嵌入

中图分类号:TN386 文献标识码:A 文章编号:2096-4706(2020)20-0023-04

The Design and Manufacture of TRL Calibration Part for Silicon-based Chip

ZHEN Jianyu1,CHEN Na2

(1.The 13th Research Institute of China Electronics Technology Group Corporation,Shijiazhuang 050051,China;

2.China Electronics Import and Export Co.,Ltd.,Beijing 100036,China)

Abstract:In order to meet the requirements for precise testing of device models when designing silicon-based chip circuits in the K/Ka band,the article analyzes the TRL calibration technology of silicon-based chips that can achieve precise calibration. According to the TRL calibration principle,the corresponding calibration part was designed and manufactured,the inductance and capacitance models on chip were extracted by means of de-embedding. In 20 GHz~30 GHz high frequency applications,the accuracy of the models was verified. Measurement results show that the calibration part achieved the desired results,the simulated value and the measured value are in good agreement.

Keywords:silicon-based chip;TRL calibration technology;de-embedding

0 引 言

硅基芯片電路具有低成本、高集成度的特点。这些年随着硅基芯片在微波射频领域的应用越来越广泛,其设计的准确性越来越受到关注。对微波集成电路的设计者来说,器件的模型是否准确,直接决定了芯片电路的设计效率。为了减少流片次数并降低成本,需要对片上晶体管、电容、电感等器件模型进行准确地提取。

微波在片测试系统在使用前,需要用相应的校准方法做矢量校准。目前商用的校准方法主要有两种:一种是采用集总参数元件作为标准,如LRRM标准、SOLT标准等;一种是基于共面波导传输线的TEM模进行校准,如TRL标准[1]。本文采用的TRL校准方法相比于采用集总参数元件,易于加工制作,且精度不依赖于元件的精度。其校准参考面为共面传输线直通校准件的中间,校准的精度主要由传输线的特征阻抗与系统参考阻抗的偏离造成。另外,由于在片校准不同校准件切换时,探针与校准芯片PAD接触时所产生的随机误差也是不可忽视的[2]。在实际工程应用中,TRL校准方法使用时要求校准件与被测件为同一衬底材料,而且被测件上的过渡传输线部分与校准件也要完全一致。美国国家标准与技术研究院对TRL校准技术问题进行了系统性研究,并在21世纪前后提出Multi-TRL校准技术,开发了相应的校准算法并研制了Multi-TRL校准标准。Multi-TRL校准算法可以对传输线特征阻抗作精确定义,并且可以减少在片测试过程的随机误差,因此被国际上公认为在片矢量网络分析仪校准技术中准确度最高的校准方法[3]。国内在片TRL校准技术目前应用较少,而芯片设计及探针测试精度要求越来越高,在这种背景下,本文对TRL在片校准技术进行研究。

基于多年工作经历,作者采用了55 nm RF CMOS硅基芯片工艺,并对该工艺进行了专用的片上TRL校准件的设计与制作,同时设计了不同频段的滤波器电路对提取出来的模型进行验证。最终实现对器件的仿真模型进行准确提取,从而提高在该工艺上电路的设计准确度和一次流片成功率。

1 TRL校准原理

校准是测试工作第一步,其作用是去除各种误差项对测试带来的影响,也是一个去嵌入的过程。先建立相应的误差模型,确定误差项,通过校准测试得到误差项的参数,然后经过计算去除误差。误差模型根据误差项的阶数分为高阶误差模型和低阶误差模型,图1中给出了一种8项误差模型的信号流图。为了消除图中的误差项,需要使用一定的校准方法。TRL校准的准确度较多依赖于传输线的特性阻抗,与其他因素无关。所以本文采用了该校准方法。

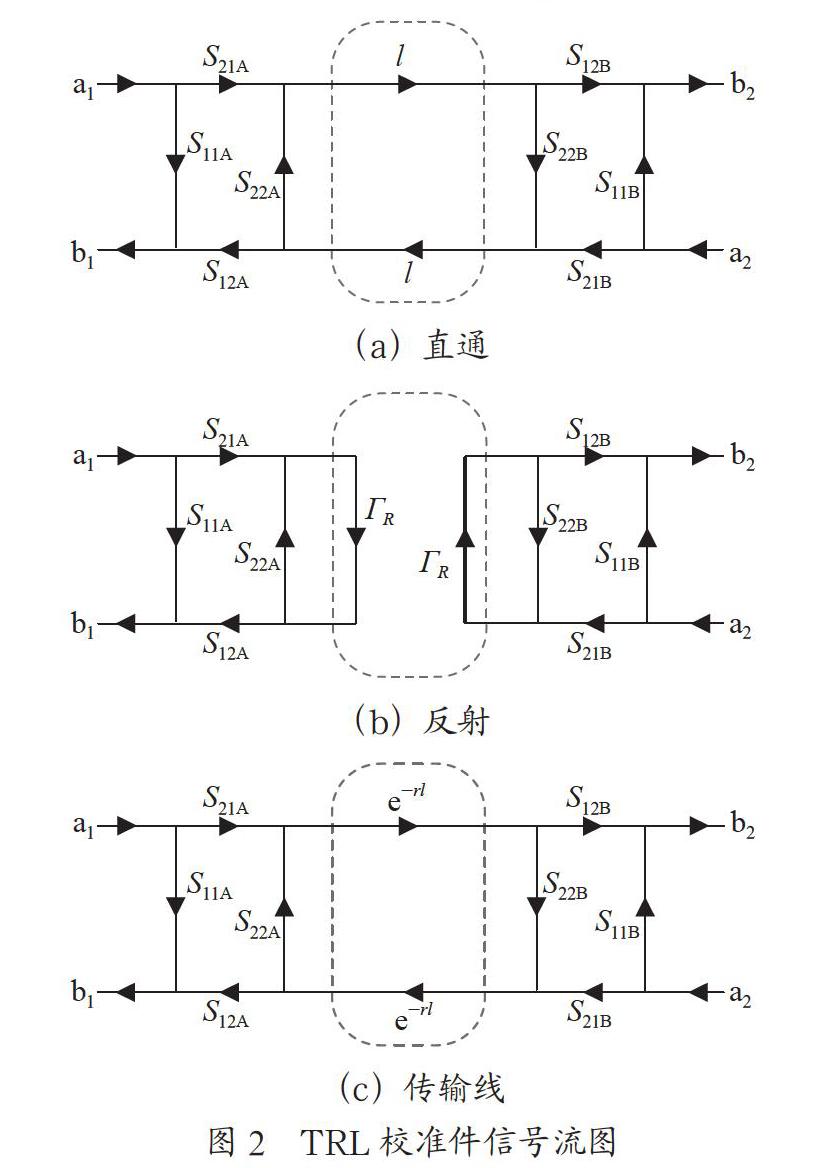

TRL校准方法是基于一定的误差项模型,利用三个已知S参数的校准件分别替代图1中的被测件DUT,可以得到三种特殊情况下的信号流图[4],分别是直通、反射、传输线,如图2所示。其中ΓR为反射系数,r为传输常数,l为电长度。

根据图2中的TRL信号流图,可以得到3组特定情况的方程式。通过解方程最终可以得出过渡部分的S参数,这样校准后的测试系统就可以测得任意模型的S参数。实际上,硅基芯片在片测试时,这个计算过程是由矢量网络分析仪完成的。但是,校准后的测试精度是由三个校准件本身所决定。因此如何设计专用硅基芯片的TRL校准件是非常重要的。

2 硅基芯片TRL校准件的设计与制作

本文所用硅基工艺为55 nm RF CMOS工艺。该工艺共10层金属,上面两层金属较厚,适合低损耗的射频走线,为了使得校准件传输线的特性阻抗尽量接近系统阻抗50 Ω,设计中采用最上层金属作为信号走线,其余层互联加厚均作为地层,这样最大限度地降低了较准件自身的插入损耗。版图EM仿真设计采用EMX软件进行,对直通校准件、短路反射校准件、开路反射校准件、特定长度的传输线校准件分别进行了优化。加工后的芯片TRL校准件实物照片如图3所示。

设计中对各个不同的校准件有以下要求:

(1)直通标准件:直通标准件可以分为零长度和非零长度两种[5]。本文采用零长度定义该标准件。校准参考面定义在直通标准件的中间且无损耗;校准参考面处需满足公式S12=S21=1∠0°;在校准参考面上,两个端口的反射系数均为零。

(2)反射标准件:反射标准件分为短路反射标准件和开路反射标准件,要求符合反射系数越接近1越好,但不需要精确得到,另外两个端口的反射系数必须相等[6]。由于芯片结构中开路反射比短路反射更接近反射系数为1的要求,本文中最终采用开路反射标准件。

(3)传输线标准件:传输线标准件是在直通标准件的基础上,插入一段特定电长度的传输线。该传输线的特性阻抗是测量时的参考阻抗;该标准件与直通标准件相位的相应差值为20°~160°之间,相位差90°对应频率下的校准精确度最高;单一传输线的带宽一般只能达到起始频率的8倍,必要时需要做多段传输线[7]。

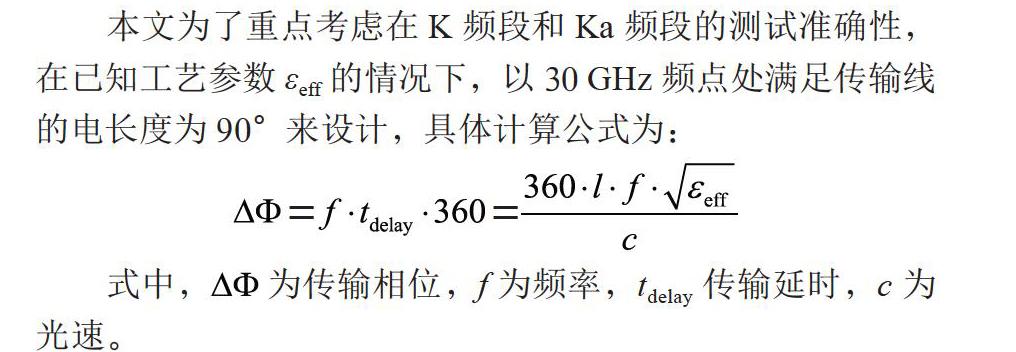

本文为了重点考虑在K频段和Ka频段的测试准确性,在已知工艺参数εeff的情况下,以30 GHz频点处满足传输线的电长度为90°来设计,具体计算公式为:

式中, 为传输相位,f为频率,tdelay传输延时,c为光速。

校准件加工完成后,对矢网在片测试系统进行探针校准。使用前,先用测试软件定义频率范围为18 GHz~40 GHz,然后分别对各个标准件进行压片、测试、提取网络方程等步骤。严格的说,探针压放的位置和压放的力度都具有一定的随机性,为了保证探针每次压完的实测值接近标准件的定义值,可以用程序预先设置自动移针和压放力度,尽量减小压针带来的随机性测试误差。

3 校準效果验证

为了对校准精度进行验证,本文同时在该工艺上设计了两款K频段和Ka频段的硅基芯片带通滤波器,用来进行仿真与实测的对比验证。首先通过制作好的校准件对在片矢网测试系统进行校准,提取出相应的电容、电感S参数模型。如图4(a)、(b)所示,图中为电容、电感模型的实物照片。然后,在滤波器电路的设计中,均采用提取出来的器件S参数模型进行仿真,K频段带通滤波器在18 GHz~23 GHz,插损的仿真值为4.1 dB,回波损耗12 dB;Ka频段带通滤波器在25 GHz~32 GHz,插损的仿真值为4.6 dB,回波损耗13 dB。最后对设计完成的两个不同频段的滤波器进行制版、流片。如图4(c)所示,为K/Ka频段带通滤波器的实物照片。

从图4中可以看出,电容、电感模型采用的过渡传输线与TRL校准片的直通标准片一致,这样可以保证测试的S参数参考面与校准平面相对应,校准端面就是直通标准件的中间位置。两个带通滤波器电路则采用的是成熟的商用级SOLT校准方法校准到探针端面进行测试,保证对比的正确性。对比电路仿真与芯片实测结果,K频段滤波器对比曲线如图5所示。

Ka频段滤波器的电路仿真与芯片测试曲线对比如图6所示。

通过对比仿真结果和测试结果,可以看出:K频段带通滤波器在18 GHz~23 GHz,插入损耗的仿真值与实测值相差0.2 dB,回波损耗相差2 dB;Ka频段带通滤波器在25 GHz~32 GHz,插入损耗的仿真值与实测值相差0.4 dB,回波损耗相差3 dB。芯片测试曲线和电路仿真曲线吻合较好,可以满足硅基芯片模型在K/Ka频段的校准测试需求。

4 结 论

本文针对RF CMOS硅基工艺芯片的射频S参数模型的准确提取问题,设计并制作了专用的片上TRL校准件。将探针测试的校准平面定义到芯片内部模型的根部,有效地去除了片上过渡线引起的误差,实现了模型的去嵌入化测试。并通过K频段和Ka频段的两个滤波器电路进行仿真与实测对比,验证了模型提取的准确性。对该工艺下的硅基芯片设计提供了准确的设计模型,提高了设计效率,达到了校准件设计的预期效果。后续可以在宽带校准方面做进一步研究。另外,由于硅基射频芯片设计中需要结合片上晶体管共同实现某些多功能电路,下一步工作可以在本文研制的TRL片上校准件基础上对有源晶体管的S参数、I-V曲线、噪声模型、功率模型等实现精确提取,通过更多的电路对模型进行拟合,不断提高设计准确度。

参考文献:

[1] MARKSR B. A multiline method of network analyzer calibration [J]. IEEE Transactions on Microwave Theory and Techniques,1991,39(7):1205-1215.

[2] ENGEN G F,HOER C A. Thru-reflect-line:an improved technique for calibrating the dual six-port automatic network analyzer [J]. IEEE Transactions on Microwave Theory and Techniques,1979,27(12):987-993.

[3] 王尊峰,杨保国,马景芳.基于TRL校准的夹具测试技术浅析 [J].国外电子测量技术,2017,36(7):110-113.

[4] 杨小峰,史江义.C-band 6-bit phase shifter for a phase array antenna [J].Journal of Semiconductors,2013,34(4):112-115.

[5] 王一帮,栾鹏,吴爱华,等.基于Multi-TRL算法的传输线特征阻抗定标 [J].计量学报,2017,38(2):225-229.

[6] 赵伟.多端口矢量网络分析仪校准技术研究 [D].南京:南京航空航天大学,2011.

[7] 刘迪.怎样设计和验证TRL校准件及具体过程 [J].电子产品世界,2008(3):123-126.

作者简介:甄建宇(1987—),男,汉族,河北张家口人,工程师,硕士研究生,研究方向:微波毫米波集成电路设计。