全球首款多阵列忆阻器“存算一体”系统问世

2020-05-13 14:33

发明与创新·大科技 2020年3期

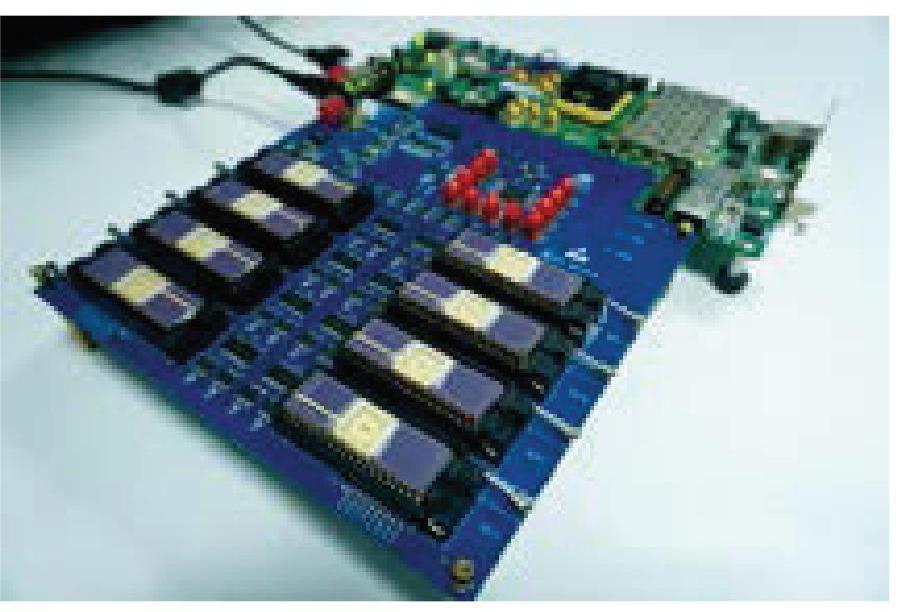

随着摩尔定律趋近极限,通过集成电路工艺微缩的方式获得算力提升越来越难;而计算与存储在不同电路单元中完成,会造成大量数据搬运功耗增加和额外延迟。如何提高算力,突破技术瓶颈?2月26日,清华大学称,该校微电子所、未来芯片技术高精尖创新中心的钱鹤、吴华强教授团队,与合作者共同研发出一款基于多个忆阻器阵列的存算一體系统,在处理卷积神经网络时的能效比图形处理器芯片高两个数量级,大幅提升计算设备的算力,且是传统芯片功耗的1/100。相关成果近日发表于《自然》杂志上。

猜你喜欢

环球时报(2021-06-03)2021-06-03

少儿科学周刊·儿童版(2021年24期)2021-03-24

奇闻怪事(2019年11期)2019-12-25

少年文艺·开心阅读作文(2019年2期)2019-03-04

看天下(2018年28期)2018-10-20

科技资讯(2018年2期)2018-06-05

时尚北京(2017年2期)2017-02-28

北京教育·高教版(2015年12期)2015-12-26