基于FPGA的UART的设计与实现

张晓 胡颖毅 黄子硕 魏鹏

摘要:UART接口在机载航空仪表中得到了广泛应用,本文介绍了一种基于FPGA设计实现的UART的双工通信协议,使用VHDL语言进行描述,其波特率可以根据设计需要进行调整,控制逻辑方便。通过相关仿真和试验,验证了UART收发功能均满足要求。

关键词:FPGA;UART;VHDL

中图分类号:TN915.04 文献标识码:A 文章编号:1007-9416(2020)02-0099-02

0 引言

UART是通用异步收发器(Universal Asynchronous Receiver/Transmitter),是一种异步收发传输器,是设备间进行异步通信的关键模块。UART包括RS232、RS449、RS423、RS422和RS485等接口标准规范和总线标准规范,即UART是异步串行通信口的总称。UART负责处理数据总线和串行口之间的串/并、并/串转换,并规定了帧格式;通信双方只要采用相同的帧格式和波特率,不需同时发送时钟,仅用两根信号线就可以完成信号通信,因此也成为异步串行通信[1]。UART字符格式为1个起始位,5~8个数据位,1个地址位或奇偶位(可选),1个停止位。

某型航空仪表主要通过RS422总线接口与机上其他设备进行数据交互,显示飞机的指示空速、马赫数、气压高度和升降速度等飞行数据。同时为了便于该航空仪表内部的检测和维护,设计了维护检测接口,将系统内部各部件的自检信息、传感器信息以及解算后得到的各个参数按照RS422总线要求输出。由于UART在某型仪表中的重要性,是其最主要的通信接口,本文主要讲述了此航空仪表中基于FPGA编写UART双工通信协议,实现对RS422接口芯片的控制,进行串口通讯。

1 UART双工通信的实现

1.1 UART协议的设计原理

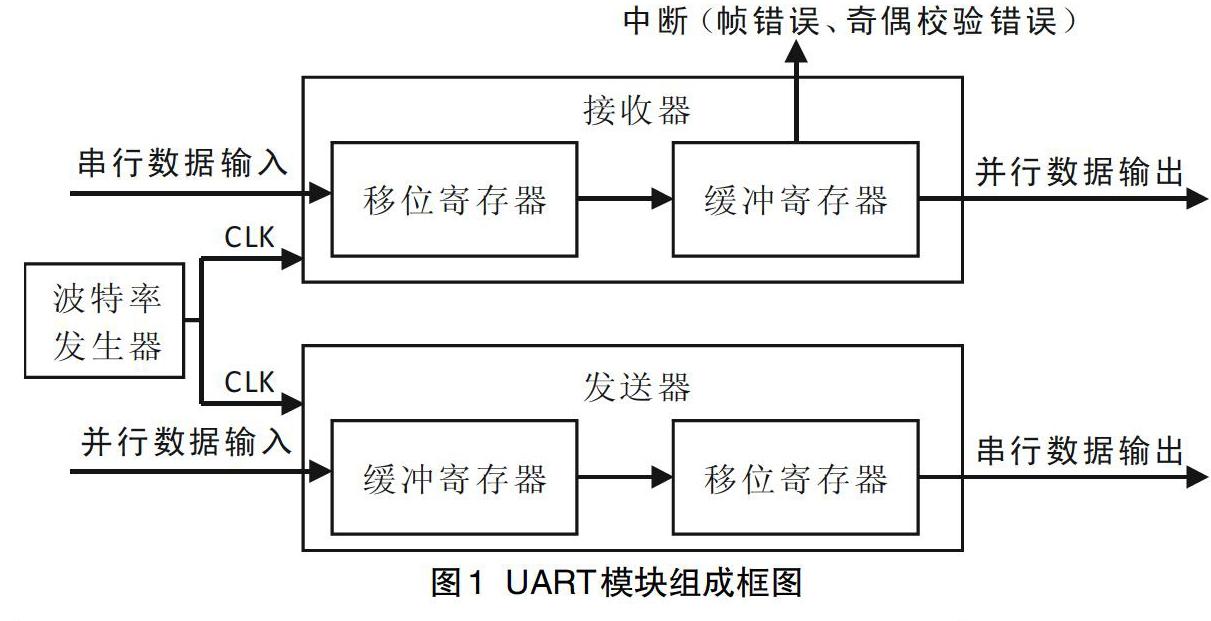

UART模块由波特率发生器、UART接收器模块和UART发送器模块三个部分构成,FPGA实现UART的模块框图如图1所示。

波特率发生器模块主要用于产生接收器和发送器的时钟频率信号。

接收器模块的作用是接收从串行数据输入异步数据,进行串/并转换。接收模块带奇偶校验错、帧出错信号,当接收完一帧数据或发送完一帧数据后提供指示信号[2]。接收器包含移位寄存器和接收缓冲寄存器,移位寄存器将数据按位采集到寄存器里,接收缓冲寄存器用来缓存接收数据,同时产生中断信号给其他模块等。

发送器模块的作用是接收机上其他设备送来的并行数据,进行并/串转换。同接收模块相同,该模块也包含移位寄存器和发送缓冲寄存器,发送缓冲寄存器用来缓存发送数据,移位寄存器将数据按位将串行数据输出到串口。

1.2 波特率发生器

波特率发生器实际上是一个分频器。波特率产生模块根据电路的晶振频率以及需要的接收时钟、发送时钟频率可计算出分频数[3]。精确的时钟是整个模块的基础,时钟有任何的偏移或者抖动,都将影响UART的功能。为了获得准确的时钟,调用了FPGA内部的PLL时钟管理模块,PLL能为FPGA内部各个模块提供精准的全局时钟或局部时钟。

当UART在发送数据时.只需要按照一定的速率将数据串行地移出就可以了,因此发送时钟和发送波特率一致。当UART在接收串行的数据时,在串行数据每一位的中间时刻,对串行数据进行采样才更准确。所以对于接收器模块的输入时钟来说,波特率发生器产生的时钟频率是波特率时钟频率的若干倍,通常工程应用中以16倍和25倍居多,目的是为在接收时进行精确地采样,以提出异步的串行数据[4]。

因为本设计中的主时钟频率是50MHz,为了能够方便合理的设置分频系数,得到更加精确的时钟频率,这里选用了倍频系数为25倍,也就是波特率发生器的输出频率blk=115200 *25=2880000Hz。具体实现过程是:用FPGA内部锁相环PLL将系统时钟50MHz倍频24再25分频得到48MHz,将48 MHz倍频12再5分频得到115.2MHz,最后将115.2MHz进行40分频得到2880000Hz。发送器模块的输入时钟按照波特率的要求设定成115200Hz,FPGA实现的过程是:在115.2MHz的基础上3次10分频得到115200Hz。

1.3 UART发送器模块

在发送器模块中,发送器的发送速率为115200 bps,每时钟周期发送一个有效比特,本文设置为奇校验。首先是起始位(发送端txd从逻辑1转化为逻辑0),其次是8个有效数据比特,低位在前,高位在后,依次发送字节的1-7位,进行校验位的计算,最后再发送字节的第8位,同样需要进行校验位的计算。当判断校验位是否为‘1,若为‘1,说明该字节发送正确有效,将校验位发出。若为‘0,说明该字节发送错误无效,需重新发送。

1.4 UART接收器模块

在接收系统中,由于串行数据和接收时钟是异步的,因此,检测起始状态非常重要[5]。由于受机上各种电磁环境和噪声的影响,为了避免接收端毛刺引起误判,得到正确的起始信号和有效数据,用最大似然判决方法对输入进行滤波处理,要求输入的数据在接收数据波特率的50%以上为低电平才确定为“真”起始位。其方法如下:

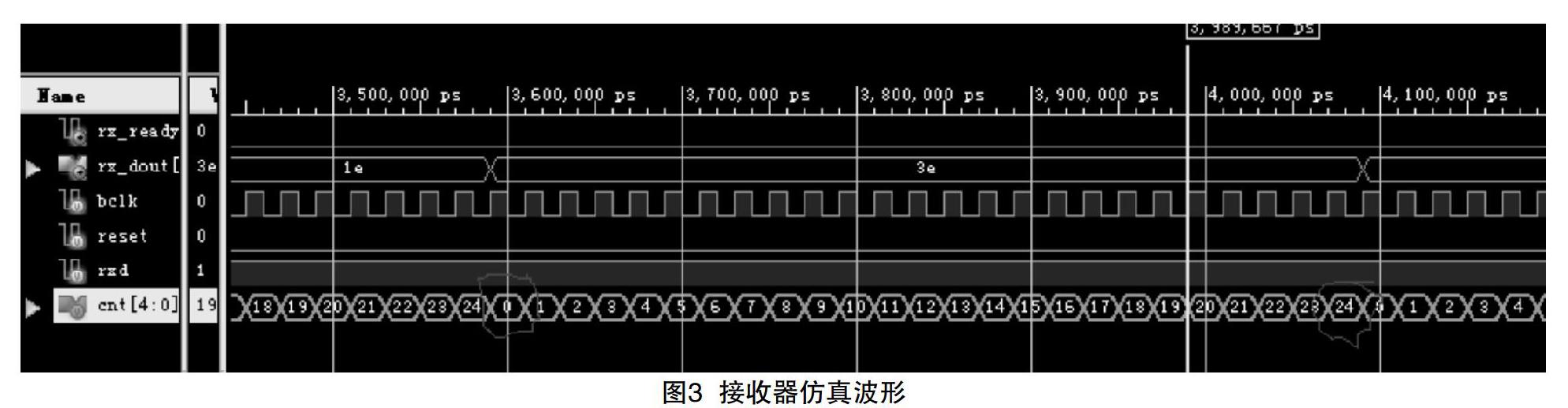

由于bclk信号的频率为波特率的25倍,则出现次数超过12次的电平逻辑值,认为是最终的采样比特值。整个接收模块的状态机包含3个状态:空闲s_idle、采样s_sample和停止s_stop。其状态机图如图2所示。

s_idle:起始位判断。若cnt未计数到24时,若此时接收到串口信号由高电平‘1变为低电平‘0时,说明可能检测到起始位,启动num的计数,当cnt为24时,判断num是否超过12,说明为 “真”起始位,则进入s _sample;

s_sample:数据采樣。若dcnt未计数到8,cnt未计数到24时,进行累加,若检测到输入变为高电平,启动num的计数;若cnt计数到24时,将 dcnt加1,同时,cnt计数清零。若num计数超过12,说明接收到一位低电平信号,否则接收到一位高电平信号,直至8位数据位全部采样完成;

s_stop:計数25周期,直至到采样到1位停止位,进入s_idle模式。

2 系统测试验证

FPGA选用Xilinx公司XC5VSX95T-1FFG1136I器件,首先在ISE中利用VHDL语言编写逻辑代码并用ISim对接收器/发送器模块进行了详细的功能仿真。

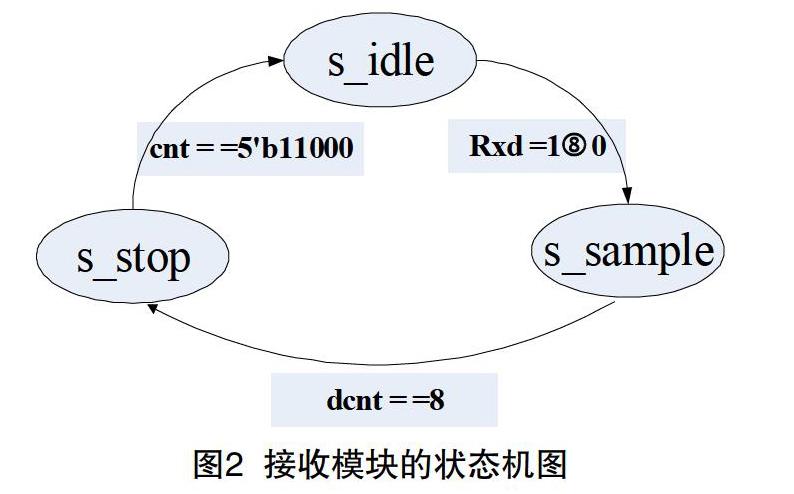

以接收器模块为例,编写testbench,输入二进制数据为“1011111001”,通过仿真图3发现,每计数25个blk时钟,采样接收一次数据,数据总线上的数据为0x3E,数据输出正确,且保证了波特率和接收数据的正确性。

通过在FPGA内部发送固定数据,计算机的串口精灵软件设置波特率115200的速率进行接收与发送的一致,验证了发送器模块的正确性。同时经计算机的串口精灵软件按照波特率为115200的速率发送数据给FPGA在某型仪表进行显示,数据一致,说明接收模块功能正确,因此FPGA正确实现了UART收发通信。

3 结语

本文详细介绍了UART通信接口的设计与实现方法,用FPGA设计实现了UART的全双工仿真和产品试验,结合串口调试助手和实际应用,验证了UART收发功能,各项通信指标均满足要求。UART是航空仪表中重要的数据传输方式,经过某型仪表产品反复的摸底测试,再次验证了UART通信接口设计实现的正确性和可靠性,所以此设计方法可定制移植使用,为以后产品的应用打下了基础。

参考文献

[1] 郭晓明,张德.基于FPGA的UART设计与实现[J].电声技术,2010,34(6):31-34.

[2] 蒋艳红.基于FPGA的UART设计与应用[J].计算机工程,2008,034(21):225-226+229.

[3] 史故臣,石旭刚,左绪勇.基于FPGA的UART设计与实现[J].中国新通信,2009(7):62-64.

[4] 杨夏,王平,张军.基于FPGA的简化UART电路设计[J].微计算机信息,2008,246(23):233-234+236.

[5] 聂涛,许世宏.基于FPGA的UART设计[J].现代电子技术,2006(2):127-129.

Designed and Realization of UART Based on FPGA

ZHANG Xiao,HU Ying-yi,HUANG Zi-shuo,WEI Peng

(Beijing Keeven Aviation Instrument Co., Ltd., Beijing 101300)

Abstract:UART interface is an important application in a certain type of aviation instrument. This paper introduces a duplex communication protocol of UART based on FPGA,described by VHDL language,baud rate can be adjusted according to the design needs,and the control logical is convenient.According to the related simulations and experiments shows that the UART transceiver functions meets the requirements.

Key words:FPGA;UART;VHDL