基于零中频信道化接收机的研究与实现

童旭升

【摘要】接收机一直以来都是通信系统的一个重要组成部分,而随着数字化集成电路的发展,高速数字电路的设计逐步代替大部分模拟电路的工作,而收发信道后零中频架构接收电路显得尤为重要,本文详细介绍了一种通用的零中频信道化接收机的实现方法,并且已经在L波段某型通信系统中应用。

【关键词】 零中频接收机;FPGA;DSP

零中频(Zero Intermediate Frequency)接收机一般也被称为直接下变频接收机,它意味着接收到的中频信号会被直接下变频为基带信号,或者说这种接收机不存在中频处理。当接收机的本振频率与接收信号的载波相位锁定时,我们称其为零外差。零中频接收架构之所以能吸引大量的关注是因为它具备超外差接收机所不具备的一些特点,首先就是接收架构中省去了中频处理单元,因而可以减少那些造价昂贵的中频无源滤波器(声表面波 SAW 滤波器),降低收发器件的成本和面积。零中频接收机采用有源低通滤波器来完成信道低通滤波,这种滤波器的带宽可以根据需要设计为可调,针对常见的模拟基带电路,接收机很容易被设计成多种模式,包括处理常见的射频前端信号。一方面,由于大部分的数字信号处理都发生在低频段,因而功率消耗可以降至最小化。另一方面,需要剩余的所有模拟器件都保持较低的噪声,因为,来自射频部分的增益并不是很高。需要注意的是,这种直接零中频接收机不需要频谱规划(需要耗费大量时间且有效性难以保证),适用性也更广。

1. 接收端整体框图

输入信号为瞬时带宽10MHz,范围900-1300MHz的跳频信号。射频信号经过4路下变频器与带通滤波器后经4路AD采样。4路AD采样后的数据送入FPGA进行处理。FPGA中有4路下变频器,其频率由跳频库控制4个DDS产生。4路AD数据经过选择器与4路下变频器相连,信号在FPGA中完成下变频抽取滤波后送入同步解调和译码模块。为叙述方便,从上往下分别称第1、2、3、4路AD。

2. 采样率选择

由带通采样定理可得(如图2):

信号载频在450MHz到550MHz之间滑动,随着载频频率的增大则fL与fH的值也在依次增大,由式(1-1)可得fs上下边界也在逐渐增大。fs的选择需要满足频率在450MHz到550MHz所有载频,故fs只能在[222M,222.5M]、[277.5M,296.6M]、[370M,445M]、[550M,890M]和[1100,+∞]之间选取。

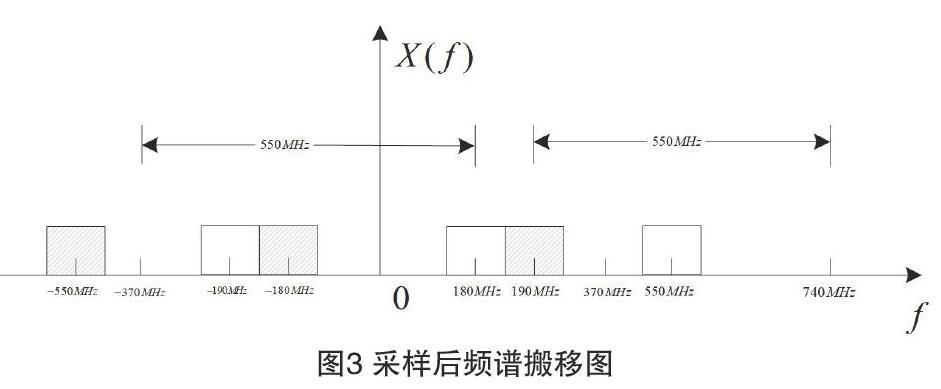

例如若fs=370M,载频频率为fc=550M时,采样后频谱图如图3所示,若采样率再减小一点,则会出现频谱混叠。

综上所述,若ω0、ω1、ω2和ω3依次等于450MHz、550MHz、650MHz和750MHz。信号带宽为10MHz,则AD采样率的选择区间为[222M,222.5M]、[277.5M,296.6M]、[370M,445M]、[550M,890M]和[1100,+∞]。

2.1 同步和解跳频

为降低信号功率对同步捕获中相关峰值的影响,并减少复相关运算和累加求和运算过程中的资源损耗,基于MSK调制信号利用2比特量化技术使得同步捕获资源损耗显著降低,并保证接收信号在大动态范围下,相关峰值无较大起伏,有效解决了捕获阈值难以设定的难题。

将上述两路信号与正交基带载波相乘得到Ilocal和 Qlocal,如图5(a)所示。

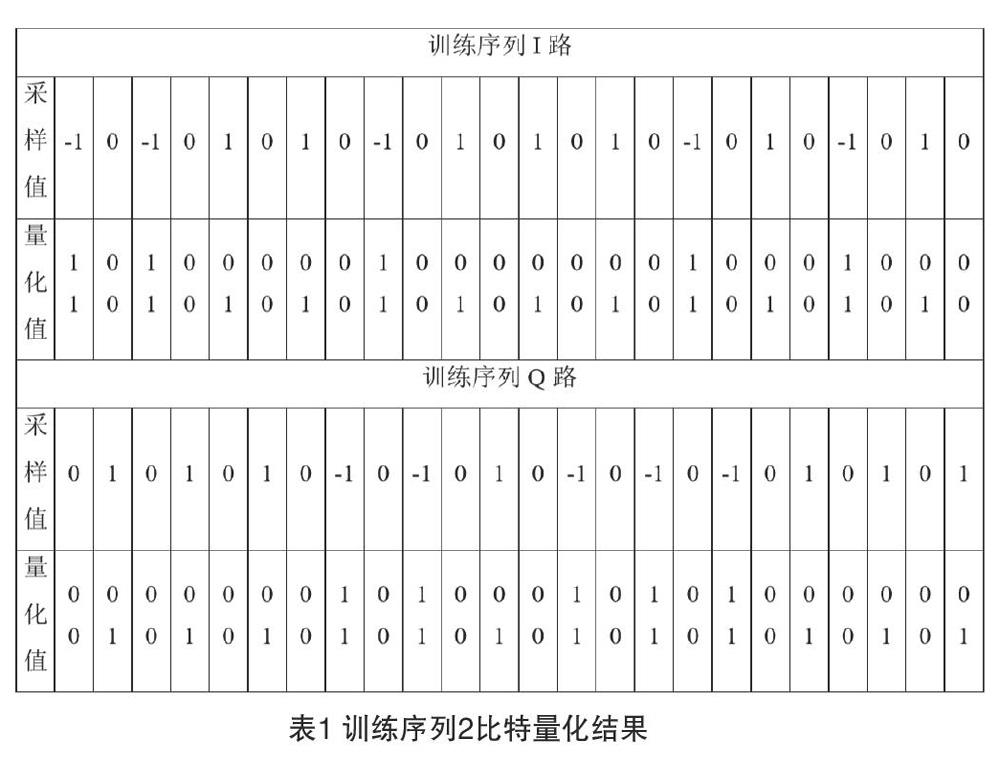

2.2 量化训练序列

训练序列的2比特量化,对调制信号Ilocal和Qlocal在碼元起始时刻进行采样,得到如图2(b)所示的采样波形,MSK为恒包络调制,采样后Ilocal路和Qlocal路幅值绝对值不能同时为1或同时为0。对训练序列进行2比特量化得到表1所示的结果。

接收信号的2比特量化,假设接收信号码元为:与本地训练序列相比存在4个码元不同,假设采样点仍然位于码元起始位置,得到接收SI、SQ两路信号,再根据公式2得到接收信号2比特量化值,具体结果如表2所示:

复相关运算,根据公式3和表1提供的复相关运算规则,将表1和表2中的2比特量化数据按照码元进行复相关运算,结果如表3所示:

累加求和,表3中所得结果与前面所述结论一致,即偶数标号0、2、4……的Ilocal·Iquan和Ilocal·Qquan的复相关结果为零,奇数标号1、3、5……的Qlocal·Qquan和Qlocal·Iquan的复相关结果为零,加法运算过程中不予考虑,相应的复相关及累加求和运算的电路结构如图3所示,利用公式4得到累加和ISum等于20,QSum等于0 。

2.3 捕获判决

相关峰值计算及捕获判决,利用公式直接计算得出相关峰值Pcorr等于20。该结果与理论结果一致,因为接受信号与训练序列存在4个码元不同,相关峰值的理论结果就是在最大峰值24的基础上减去4。实际工程中,捕获阈值一般设定为理论峰值的2/3,因此设定捕获阈值等于16,显然相关峰值大于捕获阈值,判断为捕获。

参考文献:

[1]Crols J, Steyaert M S J. A single-chip 900 MHz CMOS receiver front-end with a highperformance low-IF topology[J]. IEEE Journal of Circuits,1995,30(12):1483-1492.

[2]Andraka R. A survey of CORDIC algorithms for FPGA based computers[C]//Proceedings of the 1998 ACM/SIGDA sixth international symposium on Field programmable gate arrays. ACM, 1998: 191-200.

[3]李晓峰,周宁,周亮,等.通信原理(第2版)[M].北京:清华大学出版社,2014:337-350.