基于硬件演化的电路故障自修复实验系统设计与实现

张峻宾, 邹琼芬, 郭雷涛, 罗 莹, 杨人铣

(中国空气动力研究与发展中心超高速空气动力研究所, 绵阳 621000)

数字电路故障自修复亦称数字电路故障自愈,即通过一定的技术手段,使出现故障的数字电路恢复正常工作状态。目前,传统电路系统主要基于冗余容错技术提高系统的可靠性,虽然容错原理简单,但在受限于体积、重量等因素时,不能对所有的元器件级、芯片级等部件实现冗余备份,其适用范围受到了限制,致使电子系统的可靠性不能得到大幅度提高,并且这样的电子系统始终不具备电路重构能力。而新兴的硬件演化(evolvable hardware, EHW)技术使电子系统具备了电路自组织重构的能力,为故障自修复提供了技术途径[1-2]。

EHW技术是近年来新兴的技术,其主要以演化算法(evolutionary algorithm, EA)为组合优化和全局搜索工具,通过模拟进化来获得具备预期功能的电路和系统结构[1-3]。其公式定义为EAs+PLDs=EHW,即:演化算法+可编程逻辑器件=硬件演化[3-4]。EHW在自动控制、容错系统、模式识别与人工智能、机器人、太空和深海探索等方面有了一些应用,但是仍存在一些问题。

目前,在电子电路故障自修复领域,尚未有成熟商用的适用于EHW技术的硬件平台。美国Xilinx公司提供了API接口,可在Virtex—Ⅱ系列芯片上实现电路演化功能,但目前这些芯片较为落后,且使用技术门槛较高[5];被誉为“人工大脑之父”的美国著名研究者Hugo从1990年开始EHW技术的相关研究,其研制了一种大规模的EHW平台(CAM-brains machine, CBM),CBM平台包含72片FPGA芯片[6];Andy采用双模冗余技术在FPGA上实现细粒度、部分动态可重构电路,提出在现场可编程门阵列(field programmable gate array, FPGA)内部建立虚拟可重构电路(virtual reconfigurable circuit, VRC)平台用于电路演化[7];Lee等提出了在FPGA内部配置VRA(virtual reconfigurable architecture)平台,所设计的VRA结构和VRC一致,并采用Xilinx的Celoxica RC1000 PCI开发板演化了特征识别系统和图像滤波器[8-9]。此外,York大学等机构提出的POEtic、演化母版、DPR等。总的来说,这些演化平台的通用性和可扩展性均有限。因此,急需研制一种适用于EHW技术的演化平台。

在前期工作中,提出了基于EHW和补偿平衡技术(reparation balance technology, RBT)的数字电路故障自修复策略[1]。所提出的策略不需要进行故障定位,通过针对故障信息演化出的矫正电路(rectification circuit, RTC),实现对故障信号的补偿平衡修复。在此理论基础之上,设计了对应故障自修复实验电路系统。现主要对所设计实现的故障自修复实验系统进行详细的分析,并选取了典型电路进行验证实验。

1 基于EHW和RBT的故障自修复策略基本原理

图1 基于EHW和RBT的故障自修复通用模型Fig.1 Universal model of fault self-repair based on EHW and RBT

针对常规基于冗余设计的故障自修复技术和基于EHW的故障自修复技术存在的问题,紧扣自修复电路系统的可实现性,前期提出了基于EHW和RBT的电子电路故障自修复策略,基于EHW和RBT的故障自修复通用模型如图1所示。其主要包括上位机、下位机、被测单元(unit under test, UUT)、多路开关(multiplexer, MUX)、现场可编程门阵列(field programmable gate array, FPGA)、串口通信等6大模块。理论上能够通过设计的MUX,可将插件上所有的芯片连入设计的故障自修复电路系统,和传统的冗余容错技术相比,直接降低了硬件冗余备份所带来的巨大硬件开销。

2 硬件实验系统的整体设计思路

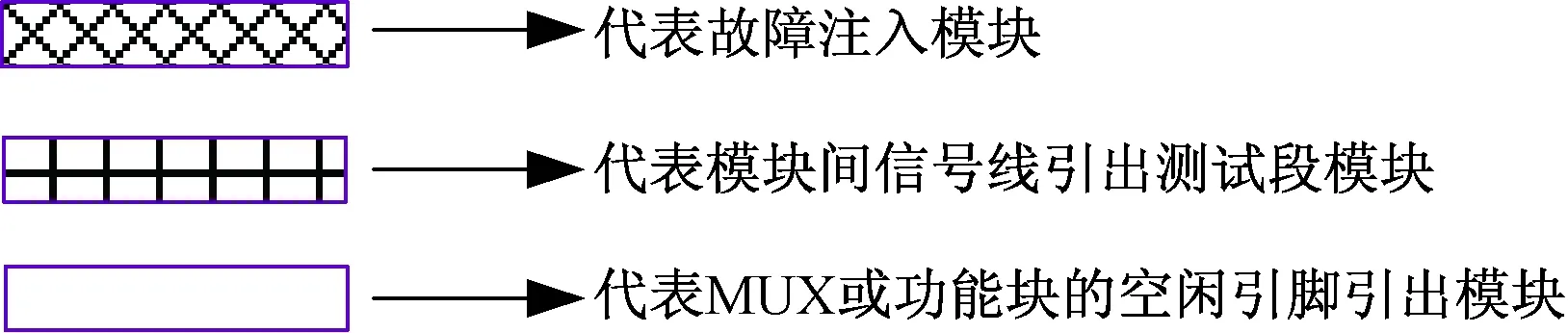

为了方便实现系统各模块之间信号的测试,在故障自修复电路系统中预置了各个模块间互通信号的测试点。将一些外部信号引入各个模块,在故障自修复电路系统中将各模块剩余引脚全部引出。为了对硬件进行更好的诠释,电路系统中图注如图2所示。

图2 实验系统图注Fig.2 Experiment system block diagram illustration

图3中的FPGA Core1、FPGA Core2和FPGA Core3是配置RTC的核心模块,均能单独配置RTC。MUX1~MUX8是8个独立的多路开关模块,A1~A6是6个独立的功能电路配置模块,在故障修复验证过程中,最主要用于配置UUT。每个模块均由一片FPGA组成的最小系统。

所有MUX模块的管脚在物理上均与FPGA Core2模块直接相连,而FPGA Core1只与MUX1、MUX2、MUX5和MUX6物理相连,FPGA Core3只与MUX3、MUX4、MUX7和MUX8物理相连。由于MUX实际上是多路开关,不具备其他功能。因此,与MUX物理相连的A1~A6功能电路模块实现了分别和FPGA Core1、FPGA Core2和FPGA Core3连接。在A1~A6模块内部,分别配置了VRC,每个VRC是由多个结构相同的可编程单元(programmable elements, PE)构成的阵列[10]。结合图1和图2,得到整个实验系统模块之间关系如图4所示。有关VRC和PE的基本原理见文献[8],此处不再赘述。

3 实验系统的最终实现

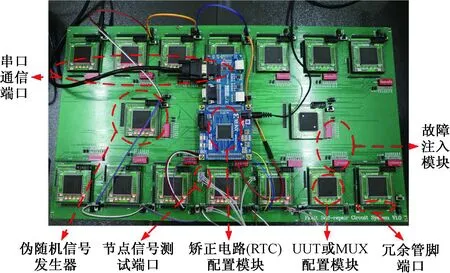

在故障自修复硬件系统设计的基础之上,对硬件电路系统进行实现,图5是最终构建的硬件系统。如图5所示的硬件电路,具有串口通信端口、伪随机信号发生器,节点信号测试端口、功能电路配置模块(包括RTC、UUT和MUX)、冗余管脚引出端口和故障注入端口。

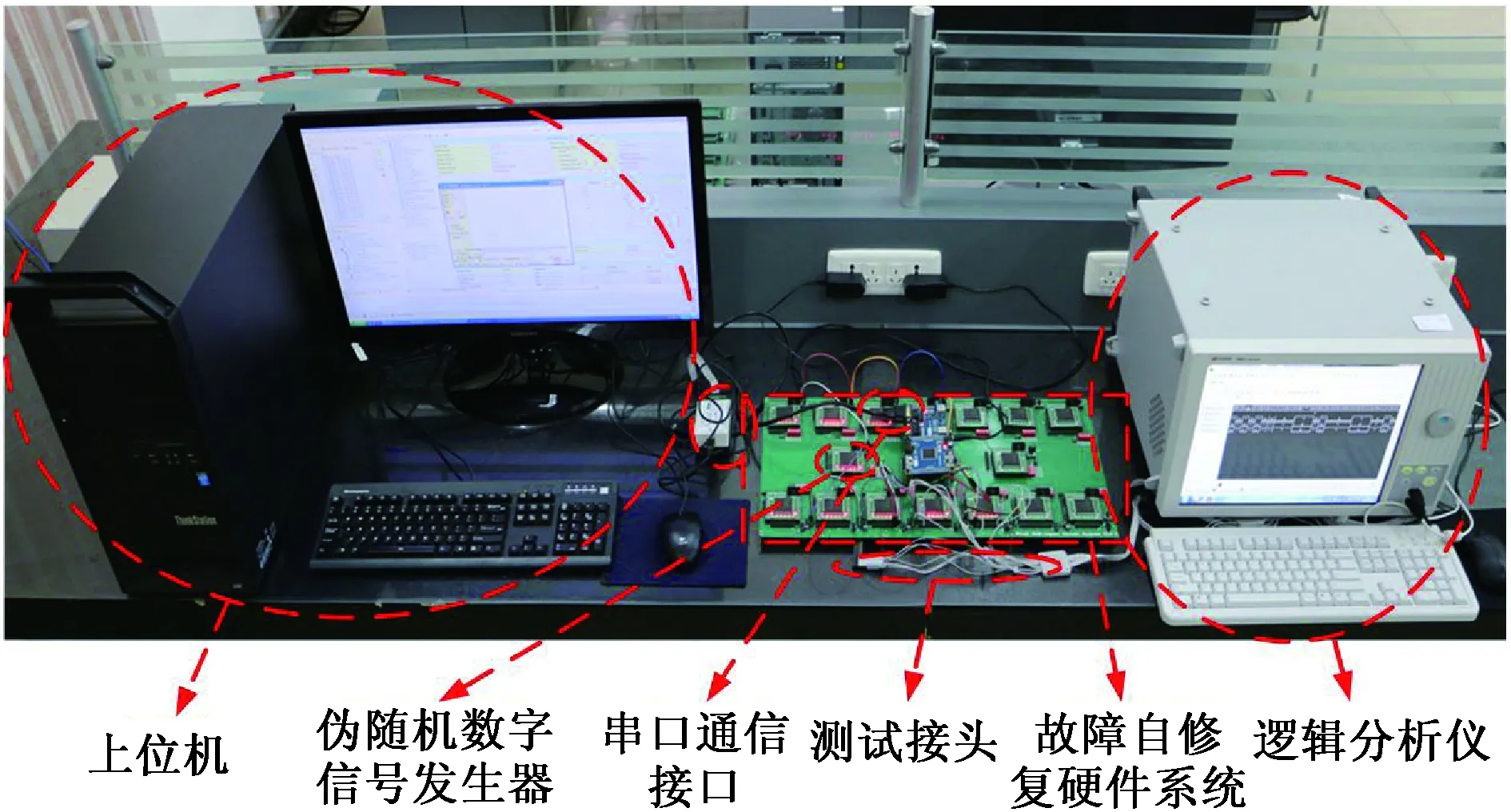

在硬件电路实现时选取的FPGA芯片型号为Xilinx Spartan XC3S500E和Xilinx Spartan XC3S250E。其中,MUX1~MUX8、A1~A6、FPGA Core1和FPGA Core3使用的是Xilinx Spartan XC3S500E,FPGA Core2使用的是Xilinx Spartan XC3S250E。FPGA Core2模块具有一个9针的串口通信端口,通过串口连接线,可与上位机实现通信。在硬件电路的基础上,搭建了故障自修复实验系统,如图6所示。

图5 故障自修复电路系统硬件实现Fig.5 Hardware system implementation of fault self-repair circuit system

图6 通用故障自修复实验系统实现Fig.6 Implementation of universal fault self-repair experiment system

图6中的故障自修复实验系统,包括了硬件电路系统、信号源、逻辑分析仪、上位机等部分。在实验验证时使用的是由FPGA上设计的伪随机信号发生器。

4 实验流程

在硬件实验中,多次出现故障时的故障修复流程同单次修复故障流程基本一致,相当于对单次故障修复流程的重复。单次修复故障的详细流程如下。

Step1首先检测正在工作的UUT是否出现故障,无论是采用自检测还是外部检测设备,只需将检测到的故障信息传给上位机,作为电路演化的约束条件。

Step2根据故障信息演化目标电路,如果电路演化成功,则进入Step 3,否则宣告故障修复失败。

佛像是佛、菩萨、罗汉、明王、诸天等像,不同的名对应不同的相。所谓如法,如为不变,引伸为恒定,也是依据法,尊重形象对于人心摄受的原理,让信众产生佛陀显前,教化众生的功效,如佛教教义之法,如佛像所传达信息之法,接引众生,见像起信。佛像要随时代而变,藏传佛像是藏族地区已经形成的对佛像的审美需求,是格式化的形态。汉传佛教是根据汉地人们的哲学观念、视觉习惯而形成的审美观念,形成的另一种格式化形态。

Step3根据成功演化的目标电路进行布局布线,如果布局布线成功,则进入Step 4,否则也将宣告故障修复失败。

Step4根据成功进行布局布线后的电路结构,转换成VRC的配置数据,其中包括VRC阵列中PE基因表达数据和PE端口互联数据。

Step5将翻译转换成的配置数据通过串口发送给VRC阵列,并根据故障信息控制MUX的连接,最终实现故障修复。

在上述过程中,Step 2和Step 3中存在故障修复失败的可能性。电路能否成功演化方面,主要受电路演化时间消耗、电路进化次数和电路复杂程度的影响。电路越复杂,电路演化时间消耗将更长,在对时效性要求较高的环境中,规定时间内成功演化出目标电路的概率将降低。演化出的电路是否能够成功布局布线方面,主要受到演化出目标电路的硬件资源消耗和VRC中PE单元数量的影响。当PE单元数量低于演化出目标电路硬件资源消耗时,布局布线失败,反之则能成功布局布线。

5 典型电路故障修复实验验证

在VRC上布局目标电路,需要控制/配置的数据包括两个方面:一是各个PE功能表达的数据;二是各个PE的端口互联配置的数据。实验中每个PE的功能表达数据只需要4位,由于VRC阵列共30个PE,因此需要120位基因表达配置数据。由于每个PE具有两个输入端,每个输入端需要6位实现端口互联的配置数据,30个PE共有60个端口,因此共需要360位数据对VRC阵列的端口互联进行控制。最终,针对VRC一次电路功能的实现,串口需要传送480位配置数据。每一次串口只能发送8位配置数据,因此串口至少需要发送60次数据(不包括校验位)。

VRC中的PE阵列如矩阵编码如图7所示。在图7中,每一个方框代表一个PE单元[5-6]。

图7 PE规模为5×6的VRC阵列坐标编码Fig.7 VRC coordinate codes when the PEs scales are 5×6

图8 演化出的电路各自布局布线图Fig.8 Independent layout of evolved circuit

针对图7串口发送的配置数据编码具有特定的顺序,具体如下:首先发送VRC中PE基因表达数据,再发送VRC端口互联数据。在图7所示的VRC阵列中,对PE基因表达进行编码时,从最后一列PE坐标的(5,6)开始,逐列逆向进行编码,直到第一列坐标为(1,1)PE为止。端口互联编码顺序从坐标为(5,6)开始,逐行逆向进行编码,直到第一行坐标为(1,1)PE截止。

采用Keysight 16852A逻辑分析仪,设置采样周期为1 ns,选取C17电路Y2输出端为高位,Y1输出端为低位。通过硬件实验系统A6模块的拨码开关输入00,此时Y2输出端将出现故障。

由于被测电路C17属于整个电路系统中的一个子模块,而C17模块输入信号的周期将受整个电路系统输入信号周期的影响。因此,C17电路输入信号周期大于32 μs,总共测试到输出信号output_test 有26处存在故障,除开输入信号为02和1D只出现1次外,其余均出现两次,统计后共计14种输入组合对应输出存在故障。对应的输入组合分别是:10、19、1F、1B、18、08、1D、1C、1E、1A、12、02、00、0A。通过观察发现,只有C17电路的Y2输出存在故障,Y1输出端输出正常。

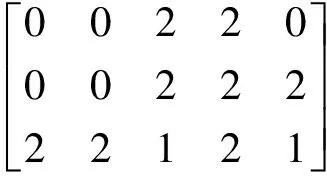

在FPGA内部设计有自测试电路,可将测试比较后确认的故障信息,通过串口发送给上位机。上位机根据测试到的故障信息,采用离散粒子群演化算法[11-13],采用三进制编码规则[14],设置最大电路演化次数为20 000次,成功演化出目标电路编码为

(1)

式(1)中,矩阵的列代表电路输入端的数量,一个矩阵代表只有一个输出端,0代表输入端被选中,1代表输入端被选中并取反,2代表输入端没有被选中。对应的布局布线如图8所示,图8中的每个方框代表一个PE单元。

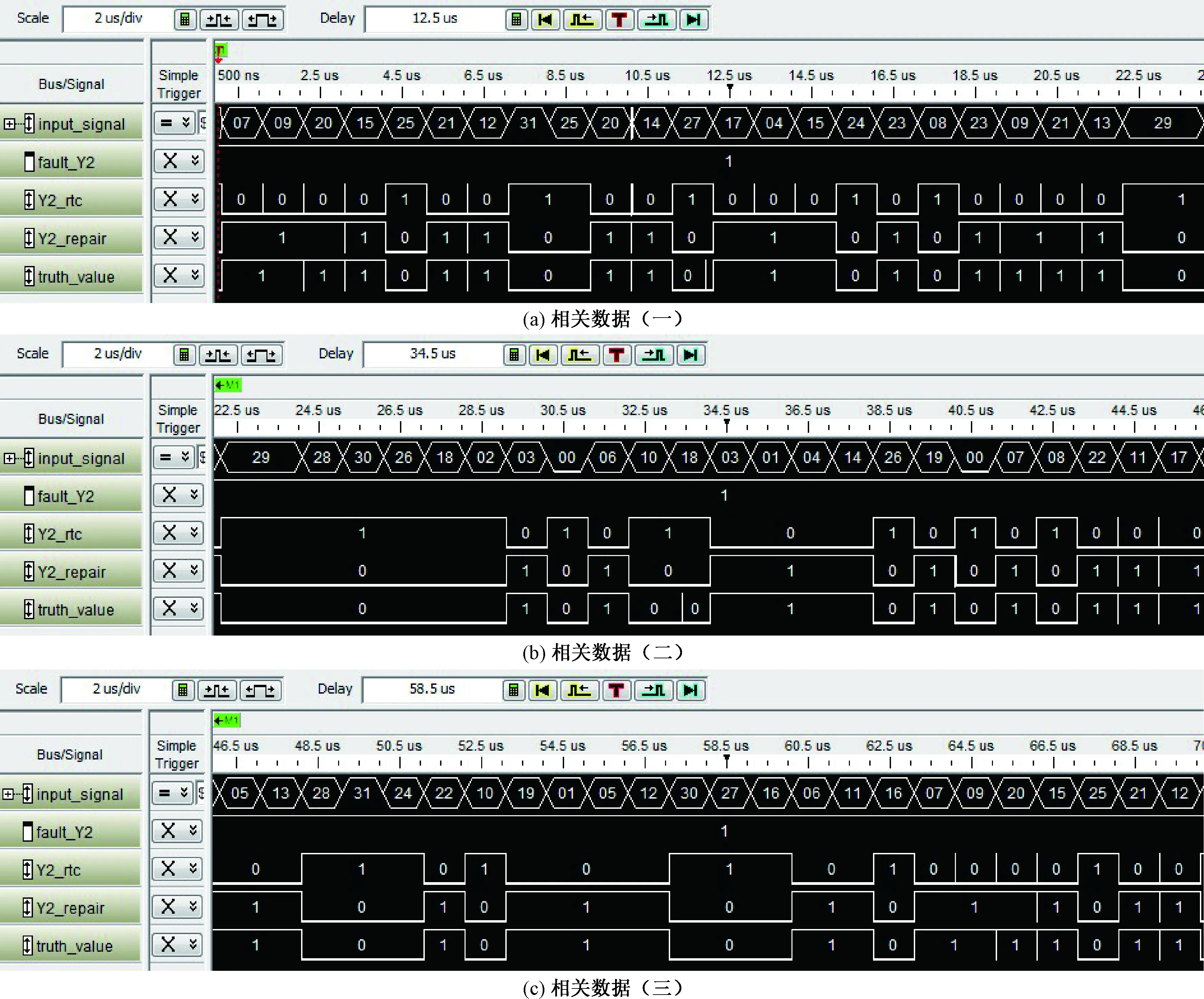

图9 补偿修复效果相关数据Fig.9 Fault self-repair result related data

将演化出的目标电路转换成16进制编码通过串口调试助手发送到FPGA,从而使演化出的目标电路成功布局到FPGA中的VRC平台上。使用Keysight 16852A逻辑分析仪,对补偿修复后的信号进行测试,测试波形如图9所示。

在图9中,input_signal是C17电路输入信号,fault_Y2是C17电路工作时Y2输出端实测信号,truth_vaule是Y2输出端理论输出信号,Y2_rtc是矫正电路信号,Y2_repair是最终修复信号。图9中可以清晰看出,Y2_repair和truth_vaule信号一致,代表故障信号Y2得到了修复。

由于设计的伪随机信号发生器还不够最优,导致存在一些毛刺,虽然这些毛刺在信号测试中出现,但不影响故障信号的修复效果。实现基于EHW和RBT的故障自修复策略实验的整个过程,在实验验证过程中虽然选取的典型电路规模较小,但不影响故障修复的效果和性能。通过实验证明:基于EHW和RBT的故障自修复策略具有一定的工程指导作用和应用价值。

6 结论

主要对基于EHW和RBT的故障自修复实验系统进行了构建和实现。详细阐述了实验系统的基本原理,硬件设计、自修复流程,最后选取典型电路进行了基于EHW和RBT的故障自修复实验验证。实验结果表明:基于EHW和RBT的故障自修复策略可行、有效,对提高电子系统的可靠性具有重要的工程应用价值。