一种电压编程型AMOLED像素电路设计

张立文, 曾涌韬, 关肖飞, 李月华, 王新林, 何红宇

(超快微纳技术与激光先进制造湖南省重点实验室(南华大学), 湖南 衡阳 421001)

0 引 言

有源矩阵有机发光二极管(AMOLED)已逐步取代传统的液晶显示(LCD),成为下一代显示的主流技术[1]。目前,AMOLED像素电路所使用的晶体管主要分为3种类型:非晶硅薄膜晶体管、低温多晶硅薄膜晶体管和铟镓锌金属氧化物晶体管。与其它两种晶体管相比,低温多晶硅薄膜晶体管具备高迁移率和稳定性的特点,因此在像素电路中得到了广泛的应用[2-3]。但是,工艺局限性导致的不均匀性,长时间工作下电应力的影响,都会导致驱动晶体管(驱动管)阈值电压(VTH_TD)和迁移率(μ)漂移,引起OLED的驱动电流变化。因此,有必要设计像素驱动电路来补偿上述因素的影响,稳定OLED的驱动电流。

现已报导的像素驱动电路主要分为两种:电压编程型和电流编程型[6-7]。与电流编程型相比,电压编程型具有对比度高、充电时间快、更适用于高分辨率显示等优点。因此,电压编程型像素驱动电路已成为像素电路设计的主流[8-13]。

早期的电压编程型像素驱动电路仅能补偿驱动管阈值电压的漂移。后来的电路既能补偿驱动管阈值电压漂移,又能补偿驱动管迁移率的漂移。为此许多研究者提出了自己的思路:文献[14-16]利用在数据输入阶段引入电位变化量,提高驱动管栅极电位或降低源极电位,以实现对驱动管迁移率漂移的补偿;文献[17]推导出了上述电位变化量的具体表达式;文献[18-19]在电路中引入镜像结构;文献[20]对数据输入阶段的时序进行调整,使驱动管提前开启或关闭,以引入电位变化量。文献[21]中提出的5T2C电路,虽然能有效补偿驱动管阈值电压的漂移,但不能补偿驱动管迁移率的漂移。因此,本文在文献[21]的基础上,通过优化电容的布局,调整数据输入阶段的时序,实现了驱动管迁移率漂移的补偿。

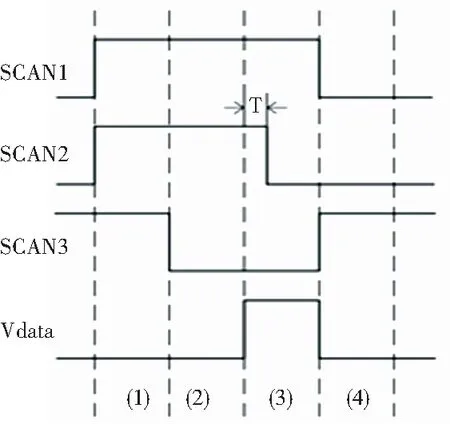

图1 电路工作时序

1 像素电路结构与原理

像素电路的结构如图2所示。

图2 像素电路结构

电路由5个N型低温多晶硅薄膜晶体管和二个电容C1、C2构成。T1~T4为开关管,TD为驱动管。SCAN1~SCAN3为扫描信号线,Vdata为数据输入线。电路的工作时序如图2所示,共分为4个阶段:重置阶段、补偿阶段、数据输入阶段、发射阶段。对各阶段电路的工作原理分析如下:

(1)重置阶段。SCAN1~SCAN3均为高电平时,T1~T4处于导通状态。数据电位Vdata为低电平,其值为Vdata_L。由于T1管导通,因此A点电位和数据电位Vdata相同,即Vdata_L。T4管处于导通状态时,C点与接地端相连,C点为零电位。电源电位VDD通过T2、T3管给B点充电至VDD。

驱动管TD产生的驱动电流IOLED通过T4流向接地端,不会流经OLED,因此OLED不会发光。

(2)补偿阶段。SCAN1、SCAN2保持高电平,T1、T2、T4保持导通状态。SCAN3变为低电平,T3管截止。Vdata保持低电平Vdata_L,C点保持零电位。本阶段,驱动管TD初始时导通且处于二极管连接状态,B点逐渐放电,电位下降至VTH_TD,此后TD截止。

由于T4管导通,本阶段OLED不会发光。

(3)数据输入阶段。SCAN1保持高电平,T1、T4保持导通状态。SCAN3保持低电平,T3保持截止状态。

在进入数据输入阶段的瞬间(t=0时刻),Vdata变为高电平Vdata_H。该变化量经T1传递至A点后,再经C1和C2耦合,使B点电位瞬间升高,此时B点电位为:

(1)

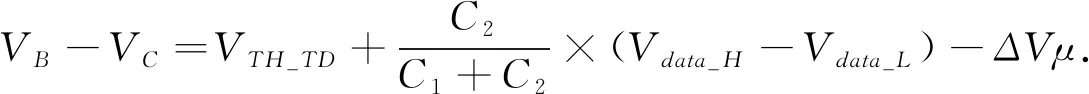

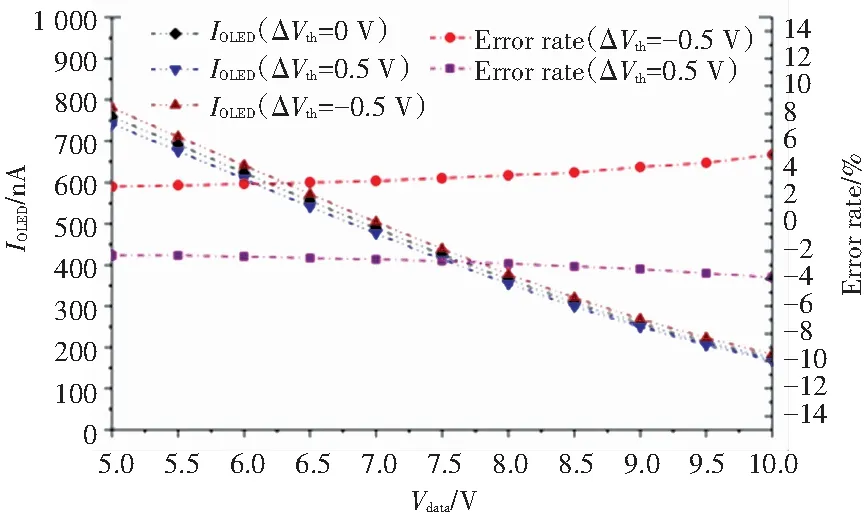

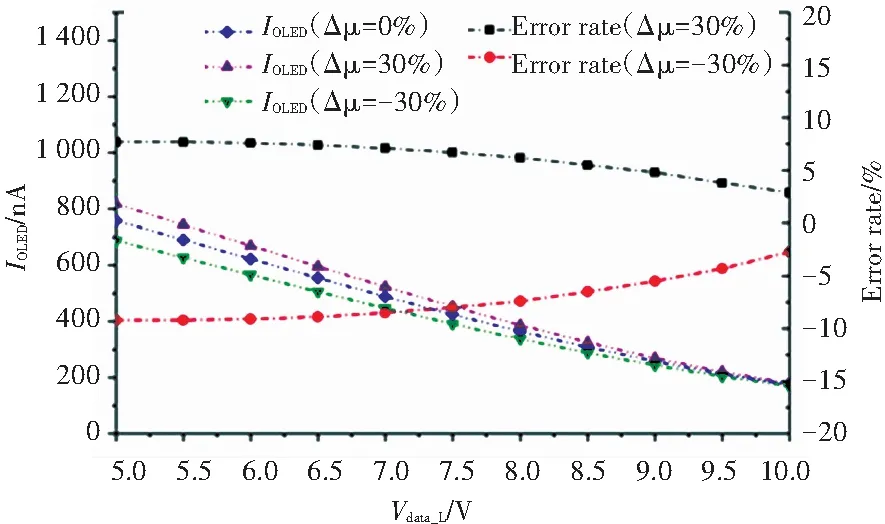

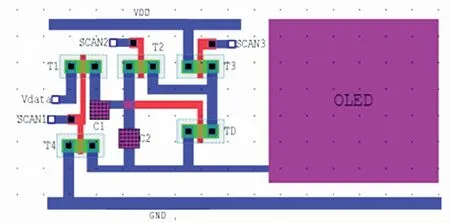

当0 在t≥T时, SCAN2变为低电平,T2截止,驱动管TD电流为零,B点电位不再降低。此时B点电位为: (2) 在本阶段,由于T4保持导通状态,C点保持零电位。 C2两端的电压为: (3) 由于T4管导通,本阶段OLED不会发光。 (4)发射阶段。SCAN3变为高电平,T3导通。SCAN1变为低电平,T1和T4截止。SCAN2保持低电平,T2保持截止状态。T4截止,C点电位由零电位瞬间升高VTH_OLED。由于C2两端的电压值不能突变,保持VC2,B点电位也瞬间升高VTH_OLED。驱动管TD导通,其栅源电压VGS等于VC2,TD驱动OLED发光。OLED的驱动电流公式为: (4) VGS=VC2. (5) 将式(3)代入式(5),再将式(5)代入式(4),得到OLED的驱动电流为: (6) 其中,k=μCOXW/L。COX为栅氧层的电容,W/L为驱动管TD沟道的宽长比,k与驱动管TD的迁移率μ成正相关。 由式(6)可以看出,IOLED与驱动管TD的阈值电压VTH_TD无关,说明该电路能补偿阈值电压VTH_TD漂移。k和ΔVμ均与驱动管TD的迁移率μ成正相关,说明该电路能补偿迁移率μ的漂移。 本节将对本文所提出的电路进行SPICE仿真。仿真电路中,OLED的模型由一个N型薄膜晶体管TOLED和一个电容COLED并联代替。仿真时,用到的器件参数与施加的电压见表1。 表1 器件参数与施加的电压 在不同VTH_TD时,B点的电位VB随时间的变化情况如图3所示。在第3)、4)阶段,当VTH_TD增大或减小0.5V时,VB大约增大或减小0.5 V,验证了式(2)的正确性。 在不同VTH_TD时,OLED的驱动电流IOLED及其误差随Vdata_L的变化情况如图4所示。IOLED随着Vdata_L的增大而减小,验证了式(6)的正确性。当VTH_TD增大或减小0.5 V时,IOLED的误差率约为4%,表明电路能有效补偿VTH_TD的漂移对IOLED的影响。 在不同μ时,OLED的驱动电流IOLED及其误差随Vdata_L的变化情况如图5所示。IOLED随着Vdata_L的增大而减小,验证了式(6)的正确性。当μ增大或减小30%时,IOLED的误差率范围约为3%~9%,表明电路能有效补偿μ的漂移对IOLED的影响。本电路与文献[24]中的电路相比,优化了电容布局。使得在数据输入阶段,电容C1与驱动管TD的栅极隔开,数据电平Vdata的细微波动就不会影响到ΔVμ,因而实现了对迁移率漂移的补偿。 图3 不同VTH_TD时,VB随时间的变化 图4 不同VTH_TD时,IOLED及其误差随Vdata_L的变化 图5 不同μ时,IOLED及其误差随Vdata_L的变化 本电路的版图结构如图6所示。左边为5个N型晶体管及二个电容,右边为OLED。 图6 电路的版图 本文改进了一种电压编程型像素补偿电路,相比于未经改进的电路结构,增加了新的补偿功能,即对驱动晶体管的迁移率漂移问题进行补偿。本文所提电路通过对电容布局和数据输入阶段时序进行优化,产生一个与驱动晶体管迁移率成正相关的电位变化量,用来补偿迁移率的漂移。SPICE仿真结果表明,驱动管的阈值电压改变±0.5 V时,驱动电流变化的误差率约为4%;驱动管的迁移率改变±30%时,驱动电流的误差率范围为3%-9%,补偿效果较好,验证了电路设计的正确性和可行性。在此基础上绘制了电路的版图,为后续电路的实物化做好了铺垫。

2 仿真结果分析

3 结束语