多通道音频采集前端硬件设计

王小稳

摘 要:现有技术中,通常用DSP芯片来对音频进行MP3压缩处理。当一片DSP芯片内要同时运行多个压缩程序来完成多路音频同时压缩时,由于内部资源不够,是无法实现的。但随着广播事业的发展,多通道音频监测的路数逐渐增多,面对多路音频采集压缩,采用一个芯片压缩一路音频的方法,会造成严重的资源浪费,增加设备的成本,同时,会增大电路的规模及设计难度。因此,亟待解决这个问题。是对DGN-32F数字音频电平监测系统[1]硬件设备的升级换代。

关键词:多路音频压缩;音频监测;多路音频采集;MP3压缩

中图分类号:TN912.3 文献标志码:A 文章编号:2095-2945(2020)08-0096-03

Abstract: In the existing technology, DSP chip is usually used to compress audio with MP3. When multiple compression programs are run at the same time in a DSP chip to complete multi-channel audio compression at the same time, it can not be realized because of the lack of internal resources. However, with the development of broadcasting, the number of multi-channel audio monitoring is gradually increasing. In the face of multi-channel audio acquisition and compression, using one chip to compress one audio will cause a serious waste of resources, increase the cost of equipment, and at the same time, will increase the scale of the circuit and the difficulty of design. Therefore, it is urgent to solve this problem. It is the upgrading of the hardware equipment of the DGN-32F digital audio level monitoring system.

Keywords: multi-channel audio compression; audio monitoring; multi-channel audio acquisition; MP3 compression

前言

在广播电视监测领域,音频信号监测是必不可少的重要手段。从开始的音频有无判断到音频幅度监测,再到现在的音频内容监测。随着技术水平不断的向智能化、自动化发展。这对音频采集前端设备的要求也越来越高。现在的多通道音频采集前端设备要实现的功能不僅仅是判断信号有无和幅度大小,还要将多路的音频全部信息通过压缩打包传输给计算机系统。本文介绍的设备即是把多路模拟音频或者数字音频AES 3接口标准[1]的数字音频信号,经过转码、MP3压缩,经过局域网,发送到服务器。

1 设备工作原理简述

模拟或数字音频信号通过接口板衡输入,使用专业音频ADC芯片,将模拟或模拟音频转化为统一格式的信号发送给控制板。控制板采用4块DSP和FPGA对信号进行处理。采用3块DSP分别压缩。使用FPGA对信号进行分配,平衡每块DSP的负载。余下的第4块DSP负责接收3块DSP压缩后的数据并控制网口将数据发送到服务器。压缩算法采用MP3算法,可以最大限度的降低数据量,并且保证音质。

2 设备的板卡功能介绍

设备的板卡按照功能块划分为五个电路板:

(1)液晶板:采用2.2寸HMI无触摸串口智能屏,通过内置单片机编程驱动。屏幕可显示本机IP、本机端口、上位机IP、上位机端口、当前监听通道以及通道总数,完成友好的人机交互操作功能,方便用户使用。

(2)电源板:结合两块开关电源,可以实现双电源冗余供电,为其它板提供稳定可靠的+15V、-15V、+5V电压。

(3)模拟接口板:采用平衡差分输入,使用专业音频ADC芯片,使用48kHz抽样率、24位精度将模拟音频转化为标准的IIS格式的串行数字信号发送给控制板。一块模拟接口板,最多支持16路模拟音频输入,可根据用户需求配置路数。

(4)数字接口板:其输入信号为标准AES3数字音频信号[2],经过转换专用芯片,转换成同模拟接口板相同(IIS格式)的串行数字信号发送给控制板。一块数字接口板最多支持8路立体声数字音频输入,亦可以根据用户需求配置。

(5)控制板:控制板基于嵌入式FPGA+DSP的架构设计。使用高速DSP芯片对音频PCM数据进行实时压缩编码,在压缩效率和音频质量方面取得较好的平衡;实时计算每路音频的峰值,以便节约计算机资源。峰值数据和实时音频通过网络控制芯片上传至服务器。网络传输部分采用嵌入式FPGA和DSP芯片共同完成压缩后音频数据实时IP封装和网络协议控制。

3 控制板的设计

控制板的设计是本设备的技术难点,我们重点解决了:利用单颗DSP芯片实现6路音频的复用编码,使一个标准的MP3码流中传输6路音频节目。大幅降低硬件系统设计难度及设备硬件成本。

3.1 控制电路板硬件设计

控制板电路主要由FPGA、DSP、DAC、DC/DC等芯片组成。利用ADSP技术[2]实现多通道语音信号的MP3压缩编码,组帧后经过以太网实现数据的远程传输。设备具备成本低,单板实现多通道音频数据传递。

处理板卡含4片低成本定点DSP处理器,包含1片主控DSP和3片压缩编码DSP处理器。其中每片压缩编码DSP处理器可完成6路数字音频的MP3压缩编码,3片DSP实现18路数字音频的压缩编码传输。主控DSP实现18路压缩数据的组帧,网络的传输控制,液晶显示控制等功能。

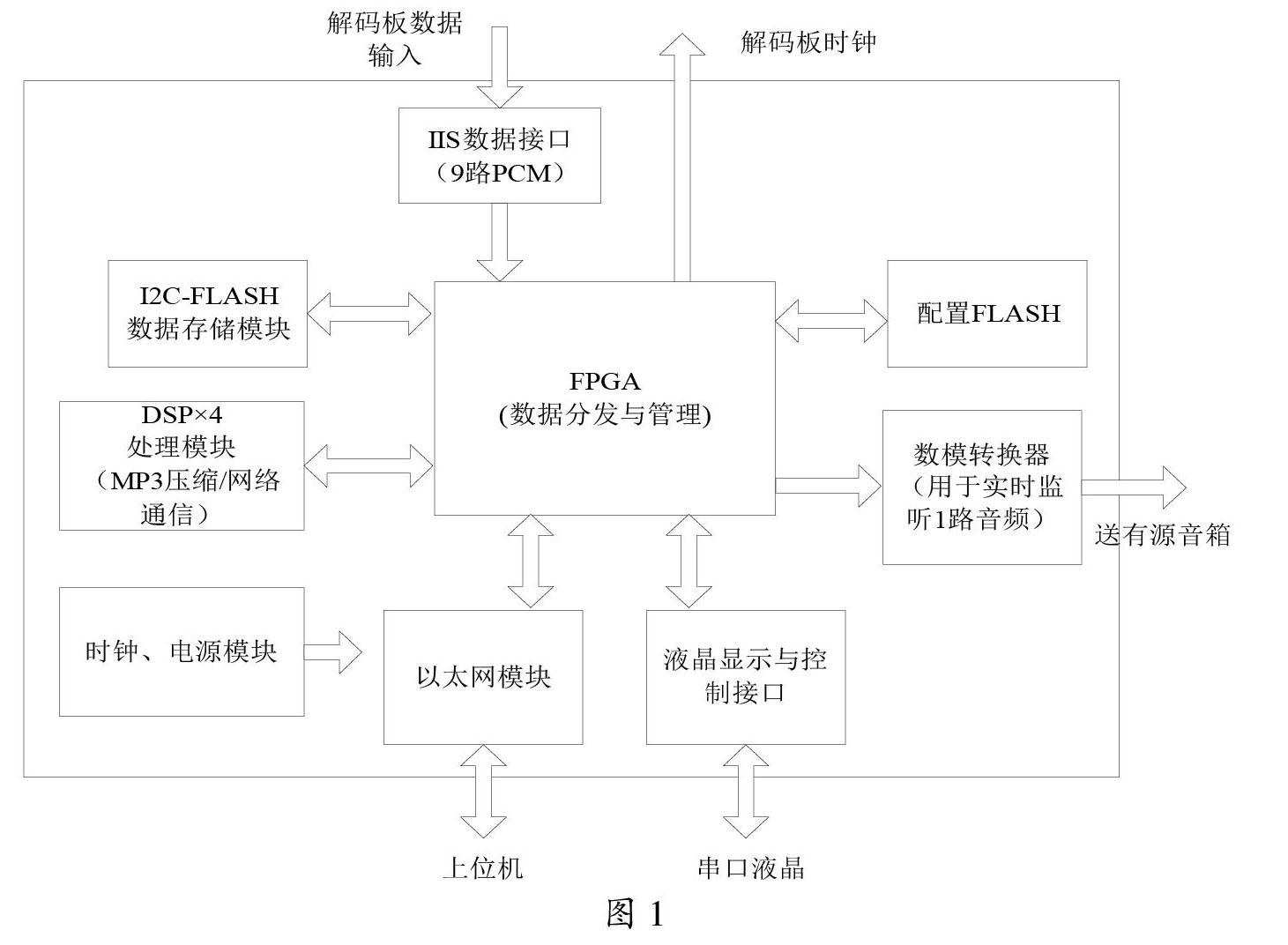

控制板硬件模块组成结构如图1所示。

3.2 FPGA芯片功能

FPGA主要功能为接收解码板IIS数据,完成串并转换,并将18路音频数据分成4组送3组DSP处理器完成压缩编码。FPGA对输入的9个通道的IIS数据进行数据处理,计算出每路一段时间内的峰值。FPGA接收压缩编码后数据组帧后送以太网上传。FPGA通过I2C-FLASH实现系统配置信息的固态存储。FPGA通过串口连接液晶显示器,可以实现系统信息的显示。FPGA可选择18路音频数据中的任意一路进行DAC转换后输出,通过有源音箱可实现音频数据的本地实时监听。

根据上述功能的需求,要求FPGA具备一定数据缓存功能和控制功能,可以采用嵌入式MicroBlaze处理器方式实现。为了控制成本,可以选用Xilinx公司的Spartan-6系列的FPGA。

3.3 DSP处理器主要功能

DSP处理器主要完成接收的音频数据的MP3压缩编码处理,由于需要对18路信号进行压缩,考虑到算法的实时性和成熟性,拟采用ADI公司的BF533SBBZ500。考虑有一定的设计冗余,采用4片DSP,根据实测结果压缩18路音频需要3片DSP芯片。第四块DSP芯片完成网络数据打包功能,利用冗余算法解决通道间音频串扰问题。

3.4 以太网模块

以太网模块主要完成编码数据的上传和接收控制、配置信息。拟采用高集成度的工业经以太网芯片W5300,可实现UDP等网路传输协议,同时支持设备IP地址、端口号、目标PC机IP地址、目标PC机端口号等配置信息的修改。

3.5 数模转换器模块

数模转换器模块实现一路音频数据的模拟转换输出。可以采用AD1852等芯片直接实现IIC数据流的转换输出。AD1852支持24bit,48K的数据转换输出。

3.6 时钟、电源模块

控制电路板采用板内晶体振荡器为基准时钟源,送FPGA锁相环路产生各个数字模块所需的时钟。

电源模块为将控制板提供的各个芯片所需的电压。由多种DC/DC芯片PTH08T240WAD组成。

4 控制板软件设计

控制板的软件设计包括FPGA和DSP两部分,其中FPGA软件主要包括IIS接口模块、以太网接口控制模块、I2C-FLASH控制模块、FPGA-DSP接口控制模块、数模转换器接口控制模块,串口液晶显示接口模块等。DSP软件主要功能实现MP3压缩编码,接收FPGA提供的48K-24bit的原始音频数据,按照指定压缩率实现MP3数据流,通过双口RAM将压缩数据流送FPGA,再经过以太网送上位机等功能。

4.1 FPGA软件

FPGA的IIS接口主要是提供3.072M位时钟和48K帧时钟到解码子板,同时FPGA接收解码芯片CS8416输出的IIS码流信号或专业音频ADC芯片输出的IIS码流信号。FPGA将16路串行IIS数据流进行并行转换后分别缓存在内部双口RAM中交换给DSP。同时FPGA将补码格式的PCM码流进行求模运算,在规定计时周期内(可通过软件配置周期)比较缓存数据最大值。具体接口时序关系参考CS8416数据手册。IIS的接口模块还支持解析数字音频用户数据编码器[3]插入的用户信息的解析,可以用于音频传输的路径监测和音频内容的甄别。

FPGA内部构建MicroBlaze处理器实现以太网的控制,包括以太网控制器的初始化、工作模式控制,数据接收、发送、组帧操作。MicroBlaze处理器读取DSP处理器的编码数据、16路PCM码流缓存数据最大值,按照一定组帧格式(待定)组帧后以UDP方式向指定上位机传輸。MicroBlaze处理器接收从以太网得到的配置信息,通过I2C接收将配置信息固化到I2C-FLASH,具体接口时序关系参考I2C-FLASH数据手册。MicroBlaze处理器还可以通过串口实现液晶显示器的控制,将系统所需显示的信息输出。串口速率一般为115200。FPGA-DSP接口采用双口RAM实现数据交换,在FPGA内实现总线接口时序。FPAG采用IIS接口输出音频数据到数模转换器,具体时序图参考AD1852器件手册相关说明。

AES3模块将串行双声道音频数据转换为并行数据,数据率为48K,16bit分辨率,一共18路。

DAC控制模块可以根据设置选择一路音频数据送DAC转换器,形成模拟音频输出。

DSP数据接口模块采用双端口RAM结构,实现18路数字音频的数据缓存,将数据送DSP处理器。18路数字音频分为3组,每组6路,分别送一个DSP处理器。由于MP3压缩帧,一帧需要1152个采样值,为了保证数据的一致性,设计双端口RAM容量为2304,采用乒乓方式实现数据向DSP传递。

FPGA软件构建了MicroBlaze处理器实现液晶显示的控制。液晶显示器采用RS232协议。

4.2 DSP软件设计

DSP软件主要功能实现MP3压缩编码,接收FPGA提供的48K-24bit的原始音频数据,按照指定压缩率实现MP3数据流,通过双口RAM将压缩数据流送FPGA,再经过以太网送上位机。

重点是解决两个问题:一是单颗DSP芯片实现多路音频的压缩,二是利用冗余数据形成保护间隔,有效的防止音频通道间的混叠。

DSP处理器分为主控DSP处理器和压缩编码处理器。压缩编码处理器完成音频数据流的MP3编码。

一片DSP处理器可运行一路压缩算法,MP3压缩算法在码率为32kbps以上时,是按照1152个原始音频数据组帧压缩。数据采样率为48kHz,即数据帧周期为1152×(1/48000)=24ms。由于DSP处理器运行速度快,主频可达到500MHz,完成一路压缩所需时间小于1ms。如果一片DSP处理器只完成1路音频数据压缩,18路音频压缩则需要18片DSP处理器,会造成资源的浪费。由于一个DSP的存储器资源不足,实际上是无法实现多个MP3压缩程序同时运行的。

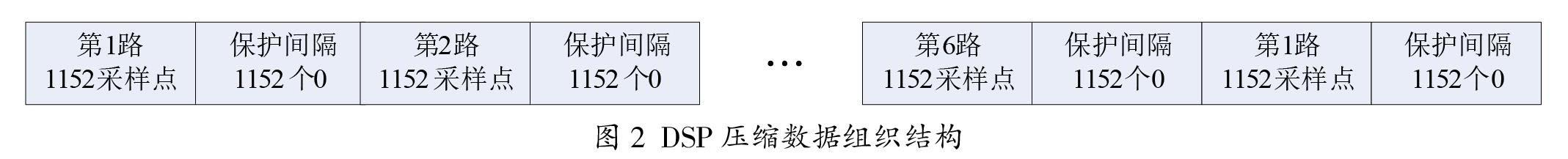

根据测试,可以将多路原始音频数据按次序组成一组数据流,这样理论上是可以实现用一块DSP压缩多路音频的问题。但经过实测发现,简单的将原始音频数据按照次序组成数据流,进行压缩编码,在经过上位机的解码后会出现通道间的声音混叠。为了解决此问题我们又在相邻两个音频数据帧之间增加数据保护间隔,在解码时丢掉保护数据。这样就可以用一片DSP处理器实现多路音频无混叠的压缩,具体组织格式如图2所示。

即将6路原始需要压缩的数据先按照1152个连续数据点组帧,每2路数据帧之间增加1152个0,一共6路原始数据按上图方式组织成数据流。此数据流按照常规MP3压缩算法进行压缩上传,这样一片DSP处理器就实现了6路原始数据的压缩。

5 结束语

通过我们的技术创新,成功的解决了制约成本的关键技术难点,实现了低成本的多通道音频采集设备的量产。为全国的广播电视系统提供了性能优越、网络化的多通道音频采集前端。配合上位机软件和自主研发的音频内容比对算法,实现了发射机输入输出音频内容是否一致和音频质量好坏的“可视”化实时并行监测。给台站提供判斷播出音频信号质量的自台监测手段,结束了没有自台播出音频质量监测手段的历史,有效提高了各台站的科学化、规范化、数字化管理水平,为台站管理的科学决策提供了可靠依据。

参考文献:

[1]肖社生.多通道音频电平监测器的系统设计[J].有线电视技术,2011(9):42.

[2]刘欣荣,肖社生,沈聪.数字音频AES3接口标准——线性表示双信道数字音频数据的串行传输格式[J].有线电视技术,2003(08):20-29.

[3]肖社生.数字音频用户数据位在广电系统中的应用[J].广播电视信息,2011(11):65.