基于异构双核FPGA系统验证设计与实现

李婷 黄苏芳 梁浩 陈龙

[摘 要]单核系统在同一个时间只能做一个任务,传统的单核系统已无法满足高性能的要求,双核系统甚至多核系统的架构也逐渐发展起来。为了降低产品风险,芯片在流片之前都需要对其所有功能进行验证和评估,验证是整个设计过程中非常重要的一个环节。随着嵌入式产品的发展,芯片越来越复杂,这导致FPGA验证平台越来越复杂。FPGA接近真实的芯片环境,速度快,实现方便,系统验证时通过软硬件同步工作能尽早发现设计上的问题。与软件仿真相比,FPGA不仅可以让设计运行在较高的频率上,还能运行复杂的系统程序,适合做长时间的系统验证和稳定性测试。本文提出了基于CORTEX-M4和CORTEX-M0双核异构的FPGA系统的验证方法,用于流片前对芯片进行系统功能验证和性能评估。本文重点提出通过SPI验证系统功能。经过该平台验证的目标芯片,流片回来的芯片所有的功能和性能都符合设计需求,可以进行量产。

[关键词]FPGA验证;双核验证;SPI验证

[中图分类号]TP391.41;TN791 [文献标志码]A [文章编号]2095–6487(2020)10–00–03

Design and Implementation of System Verification Based on

Heterogeneous Dual Core FPGA

Li Ting,Huang Su-fang,Liang Hao,Chen Long

[Abstract]A single core system can only do one task at a time. The traditional single core system can not meet the requirements of high performance. The architecture of dual core system and even multi-core system is gradually developed. In order to reduce the product risk, all functions of the chip need to be verified and evaluated before it is produced. Verification is a very important link in the whole design process. With the development of embedded products, the chip becomes more and more complex, which leads to the FPGA verification platform becoming more and more complex. FPGA is close to the real chip environment, which is fast and easy to implement. When the system is verified, the problems in design can be found as soon as possible through the synchronous work of software and hardware. Compared with software simulation, FPGA can not only make the design run at a higher frequency, but also run complex system programs, which is suitable for long-term system verification and stability test. In this paper, a verification method based on cortex-m4 and Cortex-M0 dual core heterogeneous FPGA system is proposed, which is used to verify the system function and evaluate the performance of the chip before it is taped. This paper focuses on the verification of system functions through SPI. All functions and performances of the target chip verified by the platform meet the design requirements and can be mass produced.

[Keywords]FPGA verification; dual core verification; SPI verification

1 FPGA結构

1.1 目标芯片结构

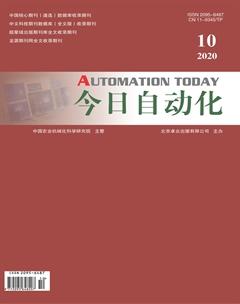

目标芯片集成了Cortex-M4和Cortex-M0双核,系统频率最高是300MHz。Cortex-M4核通过AHB2APB访问外设,主要外设包括调试单元(DBG)、2M SPI FLASH、2块256KB的DRAM、64KB PROM、2MB SDRAM、GPIO、UART、I2C、SSP、WDT、PWMTMR、DMA、CRC、GMAC和SPI_PROBE。调试单元支持外部调试器通过JTAG接口访问内核和外设。Cortex-M0核通过AHB2APB访问外设,主要外设包括2块32KB的DRAM、128KB的PRAM、CRC、DMA、UART、PWMTMR和GPIO。目标芯片基本结构如图1所示:

1.2 FPGA验证结构

载板选择的FPGA是XC2V1000,载板上面主要电路是:电源、晶振、调试接口、FPGA芯片,上面挂载了2片FLASH芯片。仿真器使用通用仿真器JLINK,通过JTAG跟目标芯片连接,实现下载程序和调试。系统时钟来源于25MHz的晶振,通过芯片内部时钟电路倍频到最高300MHz。如图2所示。

2 目前验证技术现状

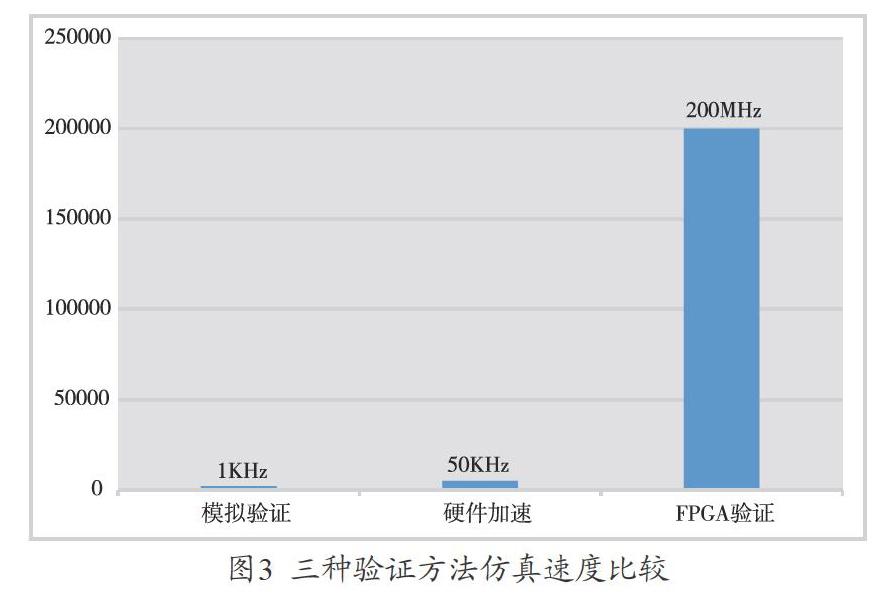

通常在高性能芯片处理器验证过程中,软件模拟验证、硬件加速仿真验证和FPGA验证是最常见的方法。

2.1 软件仿真

使用EDA工具验证设计,外部施加激励,通过查看判断结果是否符合预期,从而判读设计是否合理。这个方法更适用于单功能验证,仿真灵活、简单,模拟精准,是当今高性能芯片验证中最常用的一种方法。缺点是随着芯片规模的提升,系统级验证速度慢,时间长,系统验证不方便,只适用于前期单IP功能验证。如果IP功能不继承之前的IP或者不是通用的IP功能,需要重新搭建验证环境,搭建环境时间较长,比如搭建UART验证环境,最少需要2周的时间,整个项目无法保证验证周期内完成验证。

2.2 硬件加速

硬件加速相对于软件仿真,速度有所提升,但是价格昂贵,使用不方便。

2.3 FPGA验证

该验证接近真实的芯片环境,可以直接用于测试系统和应用程序开发,验证功能和系统的正确性。软件开发在真实的硬件上执行,实现软件和硬件协同工作。

FPGA验证和软件仿真相比,运行速度快,软件仿真在较为理想的情况下速度才可以达到KHz水平,而FPGA验证可以达到几百MHz。搭建软件仿真前期时间长,搭建FPGA环境时间短,速度快。硬件加速有较好的仿真速度,但是硬件仿真价格昂贵,并且使用不方便,在很多场合不能达到需要的性能。所以综合考虑,目标芯片选择FPGA验证。如图3所示。

2.4 FPGA验证面临的挑战

FPGA验证的流程是设计人员把设计生成mcs或者bit文件,验证人员把这个流文件烧入FPGA,通过IDE环境编程生成验证程序,然后通过烧写器烧入到目标芯片中。FPGA验证无法脱离烧写器和IDE环境,而搭建IDE环境需要一定时间,而且现在很多IDE环境需要付费,开源的IDE环境使用时不方便,且可能碰到很多问题,开源的IDE环境对最新的内核支持不如付费的好用,因此在验证初期降低效率。SPI_PROBE可以解决这个问题,可以直接把bin文件写入到RAM中,这样程序在RAM中运行,可以用于初期验证系统功能,也可以验证单个IP功能。Bin文件可以通过很多IDE环境生成,因为只需要编译,不用考虑下载。由于目标芯片的JTAG一次只能连接一个内核,切换另外一个内核时需要外部boot管脚重新选择,并且需要硬件复位之后切换才生效,SPI_PROBE能解决这个问题,SPI_PROBE可以直接访问总线,并且可以halt住内核,也可以让内核重新跑起来。在系统验证时,目标芯片在normal模式时,JTAG无法连接目标芯片,SPI_PROBE可以连接目标芯片,当系统验证不通过时,可以通过SPI_PROBE排查和查找原因。

3 验证方案

验证平台采用底板加载板架构,载板是FPGA,底板是采用STM32F429。底板的通用接口和载板连接,比如底板的UART和载板的UART接口连接、底板的SPI和载板的SPI接口連接,这样可以通过底板验证载板的通信接口功能。载板的调试接口连接到通用调试器,这样可以直接调试目标芯片。FPGA接近真实的芯片环境,这样验证人员可以使用C或者C++语言,在通用的IDE(IAR或MDK)开发环境下进行功能和系统的验证。作者使用的IDE环境是MDK-5.31。本文重点讲述在SPI协议的基础上,定义约定的协议,让目标芯片通过SPI_PROBE和PC机通信,PC机可以通过SPI接口访问目标芯片。

3.1 SPI_PROBE

SPI_PROBE是目标芯片特殊的一种功能,可以通过SPI访问AHB总线,达到访问总线上面的寄存器或者内存;SPI协议是4线SPI协议,目标芯片作为从机,PC机作为主机。如图4所示。

3.2 SPI_PROBE协议

根据目标芯片规定的协议,外部PC机通过SPI接口跟目标芯片连接,这样可以直接通过AHB总线访问memory和AHB总线上的寄存器以及部分内核寄存器;这个功能可以在验证初期,软件环境还未搭建时快速验证功能。还能解决在JTAG连接不上芯片时,可以通过这个功能访问芯片的寄存器和内存,这个功能在验证时期非常适用,不仅可以节省搭建环境的时间,还可以在JTAG连接不上时访问芯片。SPI_PROBE有个非常重要的功能,PC机通过SPI_PROBE传输bin文件给目标芯片的RAM。这个功能可以让RAM运行指定的程序。验证初期环境未搭建时,节省验证时间,快速验证部分功能,提早发现问题,让设计人员解决。

SPI_PROBE功能如下:

字节、半字、字读写指定RAM;

把Bin文件传输给RAM,从RAM拷贝Bin文件给PC机;

Halt M4/M0内核,让M4/M0内核跑起来;

读写总线上面的寄存器。

3.3 字节、半字、字读写命令

这个命令用于读写RAM和总线上面的寄存器。

SPI_PROBE命令如表1所示:

命令协议如表2所示:

读命令,数据不用发送给目标芯片,发送命令和地址之后,目标芯片会应答数据。

写命令,发送完命令和地址之后,再发送数据。

4 验证结果

使用SPI_PROBE,在验证初期,把程序烧入M4上面的PRAM运行程序,程序运行如预期执行,现象也如预期一样。把验证DRAM和SDRAM程序烧入PRAM,验证结果都是正确的。验证DRAM和SDRAM字读写,通过字写0x55AA55AA到DRAM和SDRAM,写完之后读出数据跟0x55AA55AA比对,比对一致认为验证DRAM和SDRAM字读写功能正确,字读写功能验证通过。生成验证DRAM和SDRAM的bin文件使用了0.5h,测试时间5min得到结果。如果需要搭建烧写环境,比如搭建MDK烧写环境,需要1天的时间。使用SPI_PROBE节约了1d的时间,也可以更早发现DRAM和SDRAM问题,设计人员可以更快解决发现的问题。

参考文献

[1] 陆兆春. 基于FPGA的YAK SOC原型验证平台设计与实现[D]. 北京:北京工业大学,2010.

[2] 朱英,陈诚,许晓红,等.一款多核处理器FPGA验证平台的设计与实现[J].计算机研究与发展,2014(6):139-147.

[3]Taylor S,Quinn M,Brown D,et a1.Functional verification of a multiple—issue,out—of—order,superscalar Alpha processor—the DEC Alpha 21264 microprocessor EC]/Proc of the 35th Design Automation Conf.New York:ACM,1998:638-643.