基于FPGA的嵌入式多路信号采集系统

王硕 殷树娟 李翔宇

摘 要:随着物联网技术的高速发展,终端与智能设备间的数据交互变得越来越频繁。因此如何将数据准确、快速地送到处理单元是突破物联网技术发展瓶颈的关键。在FPGA中整合多种高速接口,对不同应用开发提供灵活的设计方案。以Xilinx公司的Nexys4开发板为基带处理单元,实现了一种多路数据采集并可将数据上传到上位机的嵌入式系统。

关键词:物联网技术;数据交互;FPGA;嵌入式系统;Nexys;模数转换

中图分类号:TP39;TN4文献标识码:A文章编号:2095-1302(2020)01-00-03

0 引 言

在物联网技术应用中,智能设备通过红外、射频识别、激光扫描等信息传感设备采集信号并通过终端互联方式实现数据交互。因此高速稳定的数据采样和传输是物联网技术中不可或缺的一个关键点,随着数字集成电路的发展,高性能的FPGA(Field Programmable Gate Array)不仅拥有了更多的可配置逻辑资源,更集成了多种高速接口,使得FPGA的应用变得更加丰富[1]。主流的FPGA厂商设计了功能多样的开发工具,为开发者提供了从软件设计仿真到硬件实现的完整设计流程。本文以Xilinx公司的Nexys4开发板为基础,使用配套集成开发环境Vivado设计实现了一种信号采集嵌入式系统。

1 FPGA发展概述

FPGA是现场可编程门阵列的缩写,是在可编辑器件基础上进一步发展得到的产物,既有优于定制电路的高灵活性,又解决了可编辑器件门电路数有限的缺点。对于集成电路设计行业而言,FPGA就像一块“橡皮泥”,可以用来模仿任何电路,并且可以随时进行修改和二次设计。

通常FPGA通过硬件描述语音Verilog和VHDL等进行电路的设计,但随着FPGA配套开发环境的不断进步,其开发方式也变得更加灵活多样。在主流的FPGA厂商中,以Altera和Xilinx的FPGA性能最为优越。Altera是可编程逻辑器件的发明者,但是随着Altera公司被英特尔收购,其工作重心也发生了转移。Xilinx公司定义了FPGA,并占领了大部分市场。Xilinx对应的开发环境Vivado整合了全套FPGA开发工具,不仅包括硬件仿真、分析和综合,还包括软件的深度开发和软硬件联合调试等。同时还提供了图形化块设计流程,其中大部分复杂的逻辑器件都以IP形式封装,用户可以直接调用,大大缩短了开发周期[2]。

国内的FPGA产业近些年蓬勃发展,但是硬件国产化率仍然较低,主要依赖国外厂商。原因在于FPGA專业人才集中于几家龙头企业,且FPGA需要先进封测工艺与大量功能IP才能满足市场需求。但随着国家逐渐大力支持集成电路产业发展,中国的FPGA企业也迎来了发展的黄金时期,不论是从国防信息安全还是产业独立发展的角度来看,中国都需要做自己的FPGA。

2 FPGA信号采集系统设计

2.1 模数转换单元

Nexys4是Dligilent公司基于Xilinx Artix-7系列FPGA制作的开发板,具体如图1所示。A7系列的可配置资源较为丰富,内部有多达10万个逻辑单元(Logic Cells),且提供了统一总线(AXI)功能丰富的IP资源。该开发板集成了多种外设数据接口,主要包括Mirco USB接口(串口与编程共用)、USB HID主机接口、12位VGA接口、Pmod接口、以太网口等。

该系列FPGA还支持片内的模数转换器,即XADC。XADC由一个双12位的ADC和片上传感器组成,可以作为一个通用、高精度的模拟接口,其基本结构如图2所示。

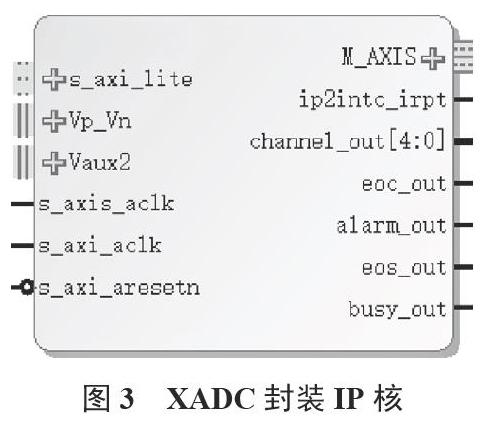

在Vivado集成设计环境中可以直接在IP库中找到已经封装XADC的IP核,如图3所示。在构建本文的采集系统时,模数转换模块直接调用该IP到板块设计图纸即可。该ADC支持多通道输入,只需激活Channel Selection选择Channel Sequencer即可。

从图3中可以看到两个主要的总线接口,即s_axi_lite和M_AXIS。其中axi_lite是AXI总线协议的简化版本,占用资源较少,主要作为微处理器MicroBlaze对XADC的驱动配置命令接口,对XADC进行初始化和基本配置。M_AXIS是AXI Stream的简称,通常这种总线协议被用来传输逻辑单元的数据,M是英文Master的缩写,表明数据的主从方向[3]。数据从Vaux2引脚输入到XADC中完成模数转换后,通过M_AXIS将数据送到下一个逻辑处理单元。

2.2 数据传输单元

数据传输单元主要用到的IP为直接内存存取单元 (Direct Memory Access,DMA)和片外存储单元PSRAM。其中DMA的主要功能是通过对地址的访问,向PSRAM中写入XADC的采样数据,然后PSRAM可以将数据暂时存储,进行下一步操作。由于片外存储单元容量有限,因此不能将无限的数据送入存储单元中,所以在逻辑上需要对数据量的大小进行控制。由于逻辑上通常使用计数方式,因此需要自建一个逻辑模块对数据量进行控制。

逻辑模块主要对XADC的数据进行计数,当达到预先设定的量时通过发送停止命令来关断数据搬运。因此在设计中,我们参考一个DMA Controller的IP核,做了一个简单的计数功能模块。该模块的初始化由MicroBlaze通过GPIO写入一个pkt_length(数据最大量)来实现。当通过的数据量达到pkt_length的值时就会发送停止命令[4]。

数据从XADC输出,经计数模块后由DMA搬运至PSRAM。Vivado内部提供的AXI_DMA的IP核如图4(a)所示。S_AXI_LITE引脚同上述XADC s_axi_lite的引脚功能,用来做初始化配置。M_AXI_S2MM是对存储器进行数据写入的引脚,S_AXIS_S2MM是Stream协议数据的流入引脚,用来接收计数模块的输出,DMA配置功能表如图4(b)所示。

通过图4(b)可以看到IP核的一些基本设置。第一栏为设置DMA的工作模式,普通的工作模式下DMA将对连续的地址进行读写,当读完最后一个地址时发送一次中断,Scatter Gather模式的DMA是对一个预先存储好的地址链表(不连续)进行访问。本设计对片外存储器进行连续写入,所以采用普通模式的DMA即可。另外,在下一栏的设置中需要激活写功能。

当数据被DMA搬运到PSRAM中暂时存储后,还需要将这些数据取出并发送到上位机中进行后续处理。本文将串口作为与上位机的通信手段,在Vivado中提供了用来作为通信端的串口IP核(UART模块),如图5所示,可在模块设计中直接调用。

2.3 控制单元

在Vivado设计中,已经封装好的逻辑IP模块通常内部都带有一个配置寄存器,通过对配置寄存器的修改,可以使这些IP模块灵活实现多种功能,以适应不同的环境。在开发环境中,允许通过软件来编写驱动,初始化逻辑器件,或者更改配置寄存器来实现更多功能。

目前,许多FPGA都集成了内部ARM核心,例如Xilinx的ZYNQ系列开发板。在设计时将ARM作为处理系统,称为PS(Processing System),逻辑部分称为PL(Progarmmable Logic)。这种开发板已经可以实现更为强大的SoC(System on Chip)[5-7]。本设计采用的Nexys4系列开发板虽然内部无ARM核,但Xilinx公司通过逻辑单元搭建了一个被称为MicroBlaze的软核,同样可以实现软件的深度开发。

在Vivado设计环境中通过SDK进行软件部分的设计,并且在开发板支持工具包中预先编辑对应IP的初始化驱动,如果仅实现该IP块的基本功能,则可直接调用对应的驱动函数,然后定义初始化顺序和启动顺序,从而实现软硬件协同的嵌入式系统[8-10]。本文设计的采集系统软件部分首先对各模块进行初始化操作,然后啟动XADC和DMA,当DMA启动时复位计数器模块。当计数器模块复位后,XADC的数据才能被送入DMA中。当DMA传输完毕后,启动UART模块将数据发送至上位机。

2.4 功能测试

在SDK模式下将上述设计生成的比特文件烧入FPGA中,并启动软硬件联合调试功能。本文用一个锯齿波作为测试的模拟信号,通过伪差分转换后送入XADC。启动系统,采集数据后将PSRAM中存储的数据发送至PC进行还原,结果如图6所示。

3 结 语

本文以Nexys4开发板为基础,通过Vivado开发环境设计了一种嵌入式系统,将SDK部分的驱动调用进行了软硬件协同的功能调试。测试结果表明,该系统基本实现了对模拟信号的采集,这对于测试仪表行业有一定的参考意义。

注:本文通讯作者为殷树娟。

参 考 文 献

[1]朱剑.基于FPGA汽车防撞雷达信号处理机的设计与实现[D].南京: 南京理工大学,2008.

[2]张志伟,赵峰.基于FPGA的LED显示控制系统设计[J].科学技术与工程,2013(3):753-756.

[3]邵伯川,侯书铭,贾小小,等.一种基于FPGA的多路高精度加速度计数据采集系统设计[J].科学技术与工程,2012(35):9486-9490.

[4]胡锐,薛晓中,孙瑞胜,等.基于FPGA+DSP的嵌入式GPS数字接收机系统设计[J].中国惯性技术学报,2009(2):187-190.

[5]王美玲,牛剑凯,刘彤.一种应用于嵌入式领域的GPS接收机的硬件设计[J].中国惯性技术学报,2006(2):43-46.

[6]张正烜,张其善,寇艳红.GPS接收机基带信号处理模块的FPGA实现[J].遥测遥控,2006(4):13-17.

[7]张占来,任红光,季新明.基于ARM+FPGA高分辨率液晶显示系统的设计与实现[J].微型机与应用,2014(6):30-32.

[8]张强,王华,苏宏锋,等.基于Xilinx FPGA的硬件协处理器设计[J].数字技术与应用,2017(4):173-174.

[9]张春宇,王晓君.FPGA单倍线测试方法研究[J].微处理机,2014(6):17-18.

[10]包可佳.基于FPGA的高速实时数字存储示波器设计[D].南京:南京航空航天大学,2007.