双路可移相信号发生器设计

李海生

(长治学院电子信息与物理系,山西长治046011)

信号发生器在仪器仪表、传感器检测、雷达遥测等很多领域有着广泛的使用。比如在线路负载及故障检测中,需要对电阻、电容、电感及其组成的网络频率特性进行测试需要产生扫频信号。随着电子技术的发展,对其性能要求越来越高,传统的设计方法无法满足需求,并且在某些应用场合有时需同时提供两路甚至三路具有相对相位差的信号。通过借助于直接数字频率合成(Direct Digital Synthesizer, DDS)技术和现场可编程门阵列(Programmable Gate Array,FPGA),可以很好的实现满足这些需求,设计出高性能、稳定度好的信号发生器[1]。

1 系统设计原理

1.1 DDS原理

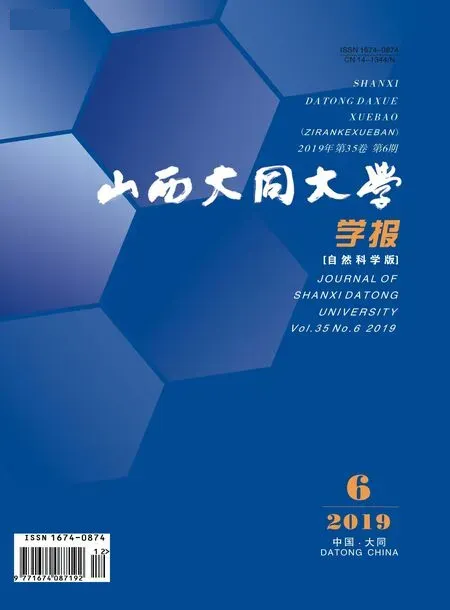

信号发生器的核心是采用DDS技术,DDS是从相位的角度去直接合成所需波形,具有低功耗、高分辨率、可编程和控制灵活方便等优点。DDS基本的原理结构如图1所示,核心部分主要有相位累加器、波形数据查找表、数模转化器三部分构成[2]。

图1 DDS基本结构图

DDS 的核心是相位累加器,在系统时钟fs触发下,相位累加器便以特定步长(即频率控制字,FSW)不断累加,其输出作为波形数据查找表的地址进行波形幅值的查找输出,输出的数字幅度值通过数模转化器后,就可以得到相应的波形模拟值[3]。

一个n位的相位累加器,存在2n个可能的相位点,而频率控制字FSW是相位累加器在每个系统时钟fs周期内递增的步长,所以输出波形的频率fo计算公式为:

通过公式(1)可以看出,当系统频率fs和相位累加器位数n固定时,改变频率控制字FSW就可以改变输出信号频率fo[4]。

1.2 系统整体设计

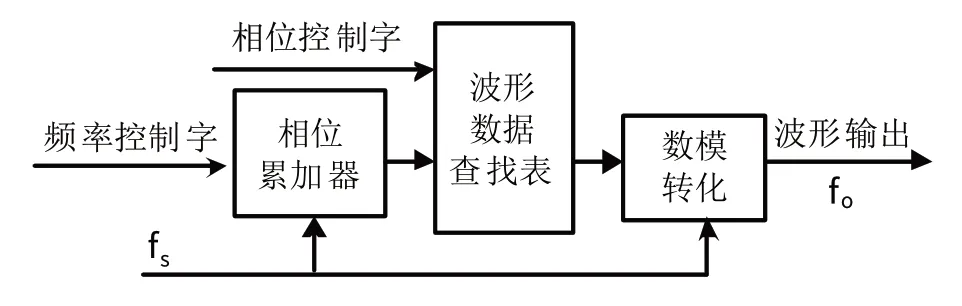

双路可移相信号发生器的设计主要分为人机交互模块、FPGA 处理模块和波形转化模块三大部分,系统结构如图2所示。人机交互模块主要是键盘和显示两部分,键盘完成外部波形类型、频率、幅度、相位等参数的输入,显示采用LCD1602完成波形数据参数的实时显示。波形转化模块主要完成FPGA输出的波形数字幅度值到实际模拟波形的转化。

图2 系统硬件结构框图

2 系统电路设计

2.1 FPGA设计

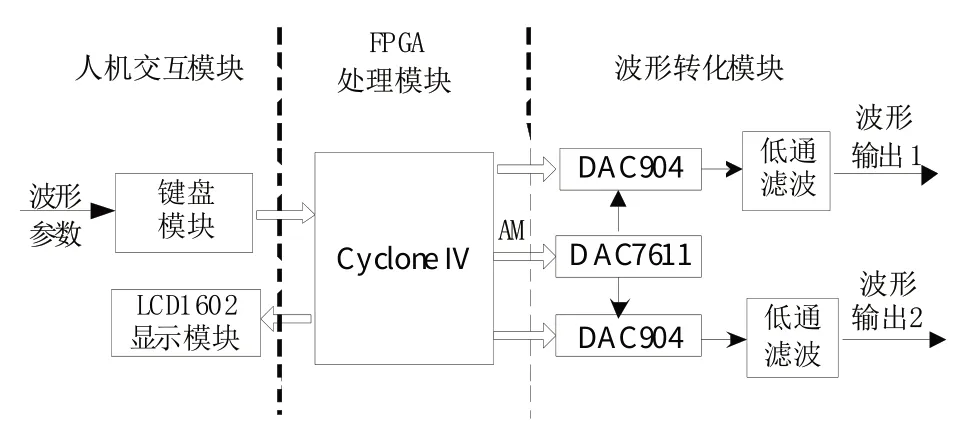

FPGA 处理模块的设计是整个系统的核心部分,选用Altera公司的Cyclone IV系列的FPGA芯片完成。FPGA的内部逻辑设计主要包括键盘扫描模块、PLL模块、调频模块、调幅模块、波形类型选择模块、LCD 显示模块等。系统逻辑设计完成后,在Quartus II软件中查看RTL视图如图3所示。

图3 FPGA内部逻辑设计RTL视图

调频模块的核心是相位累加器,在设计中,经过PLL倍频后系统时钟fs=256 MHz,相位累加器位数n=32。当相位增量FSW=1时,相对于32位的相位累加器的所有位都用来寻址,此时输出信号频率最低,fo(min)=0.06 Hz,这个值也是输出信号的最小分辨率。

波形类型选择模块是采用FPGA内部的IP核设计,是一个储存正弦波、锯齿波等各种波形幅值的ROM,主要完成波形数据的查找。ROM 的不同的地址对应了一个周期内波形不同相位下的幅度值,通过寻址对应波形的ROM 查找表就可以完成不同波形的选择输出。在实际应用设计中,相位寄存器的位会截断成14 位用来寻址ROM,这样可以减小查找表的大小,并且不影响频率分辨率。

双路移相是在单路波形输出的基础上,再输出另一路具有相对相位差的信号。通过将波形数据查找表的ROM 再例化一次,将设定的相位控制字叠加在第一路信号寻址地址上,作为第二路波形数据寻址地址进行查找输出,这样就完成两路具有相位差信号的输出。寻址的地址有14 位,相位精度可达0.02°,可以实现不同相位差的调整输出[5]。

2.2 其他电路设计

D/A 转化器电路设计中,选用两块14 位的DAC904来完成两路波形数据查找表输出的数字幅值到模拟波形的转化,输出波形幅值的控制选用12位的串行DAC7611来完成。

低通滤波器设计中,由于D/A转化器输出波形在幅值上是离散的阶梯型,含有大量的高次谐波成分。在给定前提条件下,椭圆函数滤波器是最好的一种低通滤波器,具有最窄的过渡带。在此设计中选用二阶电压跟随椭圆低通滤波器,将高频杂波滤除,从而得到平滑的波形输出。

3 系统设计验证

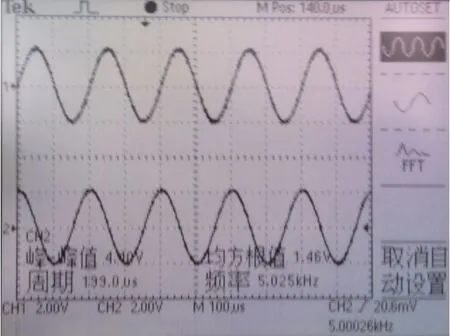

通过键盘输入两路波形的各项参数,液晶屏实时显示波形幅值、相位差和频率等参数,如图4所示。本系统完成了方波、正弦波、锯齿波、三角波等不同波形的输出,两路波形相位差调整范围:0°~360°,精度0.02°;频率输出范围:1Hz ~ 2MHz,误差:±0.5%;电压输出范围是0.01 ~4.095 V,精度±1%。方波频率输出范围:1Hz ~256MHz,占空比0~100%,精度可达1/232。图5是使用示波器测试了频率为5 kHz,幅值为4.095 V,具有90°相位差的两路正弦波条件下的输出情况,满足设计要求。

图4 双路可移相信号发生器的显示屏

图5 示波器测试的正弦波数据

4 结论

将DDS 技术与FPGA 相结合,在Quartus II 软件中,使用Verilog语言完成了系统的开发、仿真和验证。经过测试,输出的两路波形频率和幅值可调、相位差可控,很好地实现设计需求。所设计系统具有输出频率范围广、相位差可调、集成度高、多种波形输出等优点,在线路故障检测等领域具有很广泛的应用价值。