基于PowerPC+FPGA的音频转换模块设计与实现

文/柴俊 王维 陈玲 杨松

1 引言

嵌入式系统通常由一个或多个处理平台组成。PowerPC是一种精简指令集架构的中央处理器。Powerpc处理器有广泛的实现范围。同时该处理器具有非常强的嵌入式表现,因为它具有高性能、低功耗、低散热的特点。

FPGA包含可编程逻辑元件的集成电路,是在PAL、GAL、CPLD等编程器件的基础上进一步发展的产物。它的出现既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

本文提出一种以PowerPC为核心,FPGA为协处理器的音频转换模块的设计方案。其中包括硬件设计、应用软件设计,以及FPGA程序设计方案。

2 整体架构设计

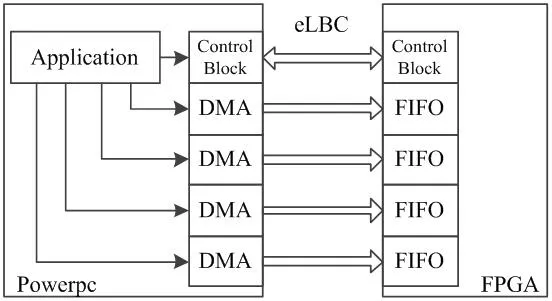

本文采用FPGA+PowerPC架构作为音频数据转换模块的核心,PowerPC作为主处理器,用于音频数字信号接收、解包、命令收发以及将解完包的音频数据传输给FPGA使用。PowerPC通过Local Bus总线与FPGA相连,通过映射的地址空间进行命令与数据的交互。FPGA作为协处理器,接收来自PowerPC的相关指令和音频数字信号,对音频数据进行处理。FPGA处理完成之后的数据通过DAC模块生成模拟音频数据,如图1。

表1:测试结果

图3:PowerPC软件流程

图4:FPGA逻辑设计框图

3 硬件电路设计

主控CPU采用freecale公司的PowerPC架构P1020处理器,外接两片512MB的DDR3存储器、64MB的NorFlash以及512MB NandFlash。P1020外接3路千兆以太网PHY芯片(88E1111)用于音频数据接收、命令接收以及调试。在板子上引出1路MAX3232接口用于打印调试。VPX接口与VPX底板连接。选用Xilinx公司的KINTEX-7系列芯片作为协处理器用于数据管理。FPGA芯片使用DDR3接口外扩4片DDR3芯片,总容量为1GB,同时使用4个PCM5102用于D/A转换,如图2所示。

4 PowerPC软件设计

PowerPC通过以太网接口与音频信号源进行通信,通过Localbus总线与FPGA进行交互。

FPGA与PowerPC通信,首先需要将FPGA映射到PowerPC的地址空间中。本文使用Localbus总线,通过配置eLBC_BR2和eLBC_OR2寄存器将1M空间从FPGA映射到PowerPC地址空间中。

PowerPC通过以太网接收音频数据,将收到的数据根据协议解包获得音频数据的元数据。本文中的音频模块提供4种采样率,根据协议将包头信息中采样率的字段解析后,并将其写入FPGA在PowerPC映射空间ControlBlock中的控制采样率寄存器。控制命令写入后,将音频元数据根据包头中的通道号写入不同通道的DMA空间中。再配置DMA控制器的DMA_MR、DMA_SAR、DMA_SATR、DMA_DAR、DMA_DATR、DMA_BCR寄存器使DMA符合FPGA的需求,就可以写入FPGA的数据接收地址,数据通过Localbus总线传至FPGA中。如图3所示。

5 FPGA逻辑设计

Xilinx公司的KINTEX-7芯片拥有丰富的外围接口,可以用来实现多模块间的复杂通信。KINTEX-7系列高容量高性能FPGA采用Verilog HDL硬件描述语言来进行编程,能够灵活的实现信号的采集及存储、提高了程序的可移植性和可维护性。

FPGA逻辑设计按照功能模块,可划分为eLBC控制器模块,FIFO模块,时钟模块,IIS控制器模块,FPGA逻辑设计框图如图4。

音频数据接收过程中,音频转换板上的PowerPC通过网络接收到数据和指令,然后通过localbus总线传输给FPGA的eLBC控制模块。eLBC控制模块收到命令后将采样率和通道选择命令传给时钟模块。时钟模块根据指令对FIFO收到的数据根据采样率进行采样。

FPGA中的FIFO模块收到PowerPC通过localbus传输的音频数据,将收到的16位音频数据通过拼接生成32位的音频数据。拼接之后的数据,再根据之前配置好的时钟模块进行采样按照一定的节拍写入IIS控制器中进行并串转换。串行数据通过IIS传到DAC模块中生成模拟信号,最后通过VPX底板传出。

6 试验测试

在实验室进行了多通道多采样率的测试,测试结果如表1所示。

7 结语

本文将PowerPC和FPGA结合的设计实现的音频转换模块,合理利用了PowerPC控制功能和FPGA的运算能力。经测试表明,本音频转换模块具备多通道多采样率,灵活切换,易于扩展等特点。