基于PCI核的BUFFER模式下链式DMA的设计

涂传亮

摘 要:数字电视信号的采集速度要求不低于270 Mbit/s,为了保证如此高速的数据流持续存入主机磁盘,且不丢失任何数据,必须解决数字视频采集卡的PCI接口设计这一关键问题。文章研究了一种基于ALTERA公司开发的PCI核PCLmt32的链式DMA的设计方法。这种方式的DMA能够实现BUFFER模式下的最高传输效率,速度达到2.112 Gbit/s,使得数字视频采集卡的PCI总线能够持续、高速地传输大量数据。

关键词:PCI;链式DMA;SOPC;Win Driver

随着数字广播电视技术的普及,人们的视觉品位要求越来越高,将数字视频信号采集到计算机中,在计算机中可以方便地对采集的视频进行各种特效处理后再播出,这样可丰富视频特效种类、提高视频的视觉效果。为了高速、实时地采集数字视频信号,必须解决外设部件互连标准(Peripheral Component Interconnect,PCI)总线接口技术这一关键问题。

本文介绍了基于链式直接存储器访问(Direct Memory Access,DMA)方式控制点云库(Point Cloud Library,PCL)mt32核完成66 MHz、32位数据传输的PCI接口设计的方法,该设计是在ALTERA公司的Cyclone II EP2C20Q240C8为主处理芯片的电路板上完成的。

1 SOPC系统框架组成

采集卡的可编程片上系统(System-on-a-Programmable-Chip,SOPC)主要由3大组件组成,主控组件是PCI组件、DMA组件、自定义数据采集组件。

PCI组件相当于此系统的CPU组件,控制DMA组件与data_in自定义组件,在PCI组件中,bar0_Prefetchable Avalon Master,表示預取址Avalon-MM主端口,提供PCI内存对Avalon-MM从设备的高带宽访问。Bar1_Non_Prefetchable Avalon Master,表示非预取址Avalon-MM主端口,提供PCI内存对Avalon-MM从设备的低延时访问。Control Status Registers Avalon Slave,表示控制状态寄存器,包含了很多与PCI-Avalon总线配置有关的寄存器,通过对它们的设置订制所需的功能。PCI Bus Access Avalon Slave,表示PCI总线通道,可以通过程序设定,映射为程序申请的内存空间。

2 DMA控制器

在实现DMA开始工作时,对主机产生一个中断,此时,主机CPU参与响应中断,在DMA工作后,不需要CPU参与,可以自行进行数据传输,采用DMA方式进行数据传输,可以大大减轻CPU的压力,提高设备的性能。

在ALTER的SOPC Builder中,可定制的DMA分为2种:BLOCK DMA和scatter-/gather DMA。Block DMA要求主设备提供PCI和Local的起始地址、传输字节数和传输方向。主机启动DMA传输并当所有数据传输完成时,PCI接口控制器将向主机申请中断。scatter/gather DMA加入了一个描述符模块,该模块存储PCI和Local的起始地址,传输字节数和下一个描述模块的地址。其传输的过程大概如下:当启动DMA状态机时,PCI接口控制首先读取DMA起始地址,开始完成第1个模块指定的数据的传输。当第1个模块中的数据传输完毕,DMA根据描述符先进先出队列提供的下一个模块的指针连续加载下一个模块,直到检测到“链结束位”,PCI接口控制器向主机申请中断。

本文设计的链式DMA是基于BLOCK DMA,能过驱动控制BLOCK DMA从而实现scatter/gather DMA的功能。

2.1 DMA Core寄存器

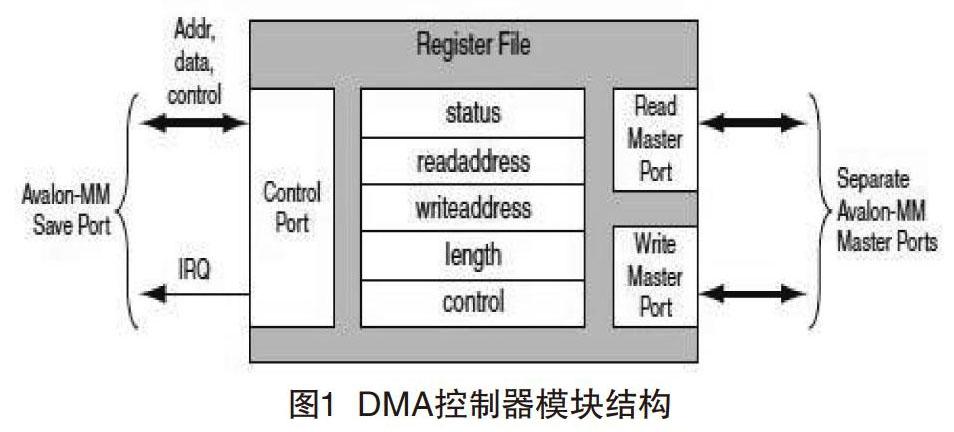

DMA控制器主要有5个寄存器,如图1所示,分别是状态寄存器status,读地址寄存器readaddress,写地址寄存器writeaddress,长度寄存器length,控制寄存器control。

在启动DMA时,首先需要分别配置readaddress,writeaddress,length和control这4个寄存器,然后总线就会启动DMA传输,DMA控制器向readaddress寄存器指向的地址中读取数据,将数据写入至writeaddress寄存器指向的地址,整个DMA操作所需传输的数据个数存储在length中,而数据传输的模式存储在控制寄存control中。

2.2 DMA BUFFER的选择

当DMA工作在突发模式下,一次DMA传输最多传送1 024个32位宽度的数据,每传送完1 024个字则需要对DMA进行中断,频繁地对DMA中断会对程序计数器效率造成影响。

当DMA工作在非突发模式下,一次DMA传输则可以传输任意大小的字,当传输完规定的数据个数后才进行一次中断,此时传输的数据个数不受1 024的控制。而两种工作状态下,数据传输的效率是不一样的。

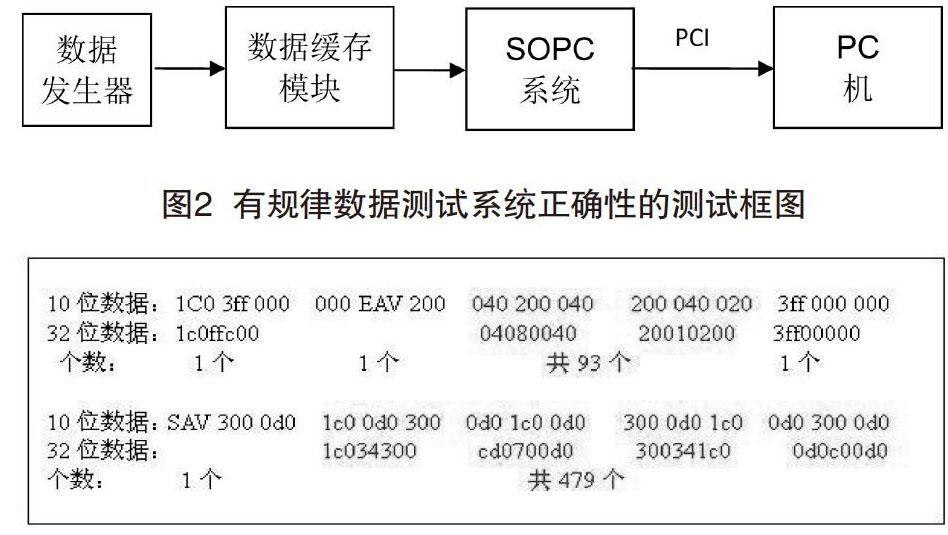

DMA工作在非突发模式下,经过逻辑分析仪采集的数据图,逻辑分析仪的主时钟为PCI的工作时钟66 MHz,yushu_out(即SOPC系统中自定义组件的地址)信号每隔5个时钟周期进行一次地址的自增,也意味着每隔5个时钟周期SOPC才接收一个动态随机存取存储器(Dynamic Random Access Memory,DRAM)的输出数据,效率变为标准的1/5。

DMA工作在突发模式下,经过逻辑分析仪采集的数据图,逻辑分析仪的主时钟为PCI的工作时钟66 MHz,yushu_out信号每隔1个时钟周期进行一次地址的自增,也意味着每隔1个时钟周期SOPC接收一个DRAM的输出数据,这完全按照PCI的工作效率进行。

因此,为了满足数字分量串行接口(Serial Digital Interface,SDI)的传输要求,使采集卡的传输效率达到最高,我们将DMA设置工作在突发模式下。

3 结果分析

使用两种方法测试BUFFER模式下DMA操作是否正确。

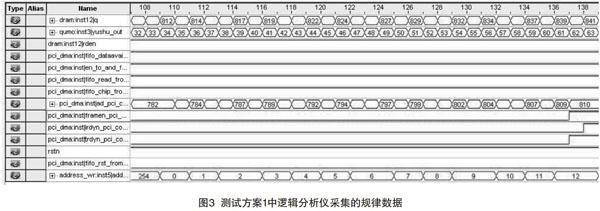

图2为测试方案1,即使用数据发生器测试数据的方法。

如图3所示,接收到的数据通过PCI的数据线输出,在108时刻连续输出782,783,784,785,786,787,788等数据,一个66 MHz时钟周期输出一个32位数据。

第二种方法即可采集数字视频信号至PC机的内存,观察内存中的数据是否正确来判断BUFFER模式下DMA是否工作正确。

将10位数据合并后32合所得的数据如图4所示,图4中的数据,均可以找得到,其中EAV SAV奇场与偶场均是不一样的,因此,其含有EAV SAV的数据是变化的,其他的数据均是固定周期出现的。

连续采集合成后的视频数据,存储在起始地址为5000000的主机内存中,截取主机中两段视频数据。

仔细观察数据,发现所有数据都与图4中标准数字视频信号数据一致。

在采信卡采集数据时,速度完全满足PCI的速率要求,即每66 MHz时钟周期,输出一个有效的32位数据。根据设计原理,是将30位数字视频信号,在高2位补零,组成32位传输数据,因此,可以知道有效数据的传输效率为1.98 Gbit/s。

4 结语

本文利用超高速集成电路硬件语言实现了基于PCI核BUFFER模式下的链式DMA,并在Altera公司的QuartusII开发工具上利用嵌入式逻辑分析仪对系统进行了测试,表明BUFFER模式下DMA的快速性,并通过分析主机中所采集到的视频数据表明了链式DMA的正确实现。通过理论分析和测试,本设计完全可以满足數字视频信号实时采集系统的要求。

[参考文献]

[1]沈羽.基于PCI总线的实时高速数据记录器研究[D].北京:中国科学院研究生院,2006.

[2]PCI-SIG.PCI Express Card Electromechanical Specification Revision2.0 [EB/OL].(2007-09-17)[2019-04-10].http://xueshu.baidu.com/usercenter/paper/show?paperid=967178a2675c137057d4cb6fcb4fbacf&site=xueshu_se&hitarticle=1.

[3]PCI-SIG.PCI Express Base Specification Revision 1.1[J].PCI Express,2005(27):272.