对数字电路中逻辑芯片相互通讯时的时序问题探讨

刘艳萍,昝国平

(山西职业技术学院,山西 太原 030006)

近年来,随着科学技术的迅速发展,数字电路的集成化程度越来越高,大量的门电路或元器件都被集成到了一片很小的半导体芯片上.当我们利用数字电路知识设计一个电路时,电路中一般会用到多个逻辑芯片,而芯片之间要相互连接、相互通讯,就好比人与人之间需要交流一样.然而这些芯片的运行速度不尽相同,有快有慢,这就使得我们在实际调试电路时经常出现一些意想不到的现象,造成整个时序电路的误动作,这种现象必须绝对避免[1].理论上分析电路设计思路是合理正确的,不应该出现这些非正常现象,但是实际中却确实出现了.究其原因,这是由于芯片相互通讯时的时序问题而导致的.本文将分类讨论逻辑芯片相互通讯时存在的时序问题.

1 两片型号相同的芯片相互通讯时存在的时序问题分析

计数器是数字系统中最常用的时序逻辑电路之一[2],在构成任意进制计数器时,通常需要采用多片集成电路.以两片相同型号的芯片构成的计数器为例来说,在它正常工作时,这两片芯片同时发出信号,但是在信号传输过程中两芯片经常会一快一慢,导致计数器不能正常计数.下面是我们在实训室调试这类电路过程中所遇到的两种情况.

1.1 从电路的源头处解决时序问题的情况

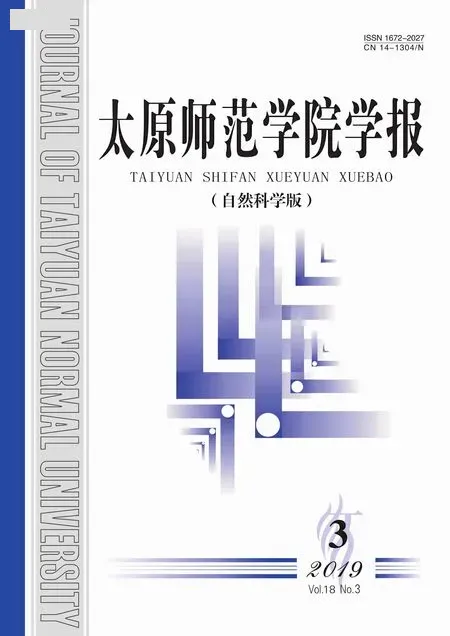

然而,实际运行电路时,经常会在第一轮递减完显示00后,下一秒直接显示20或04,而非数字24.虽然出现这种现象的几率较小,即二十个实训台可能有两三个台子出现了这种现象,但这足以说明电路设计是不完善的.我们在设计电路时必须把所有的可能因素全部考虑进去,做到无可挑剔.显然,对已出现的现象进行认真分析,不难得出结论:虽然十位和个位的芯片同为CD40192,但是两片芯片的运行速度有差别,即时序有先后,我们在设计时并未考虑到时序问题.若十位的芯片运行快,则从00置数时可能出现20;若个位的芯片运行快,则从00置数时可能出现04.这些都是瞬间的干扰信号造成的.为解决这个问题,我们在芯片外部重新设计了置数电路,如图2所示.

图1 二十四进制减法计数器电路图图2 二十四进制减法计数器中置数电路图

1.2 从电路的中间处解决时序问题的情况

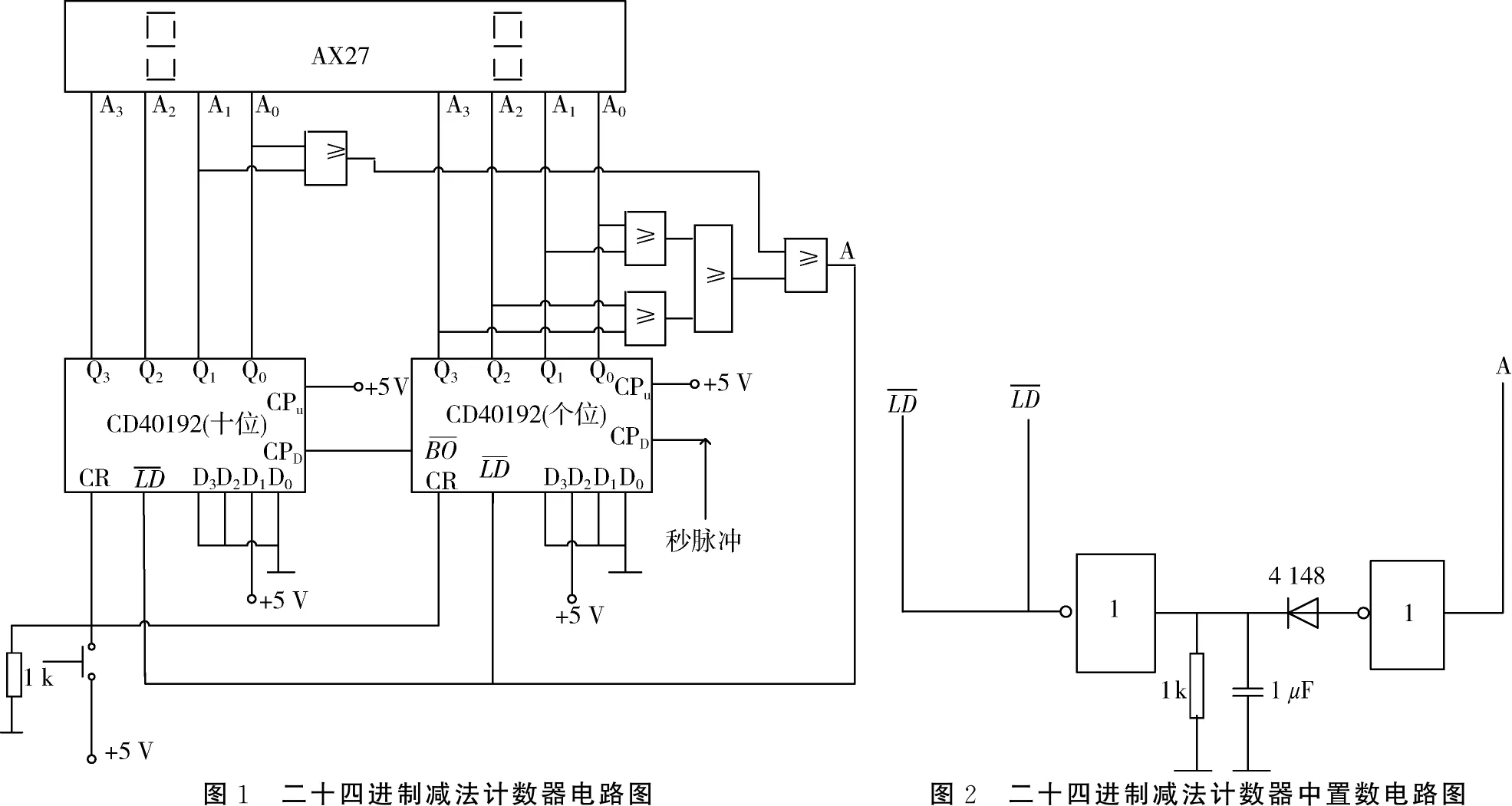

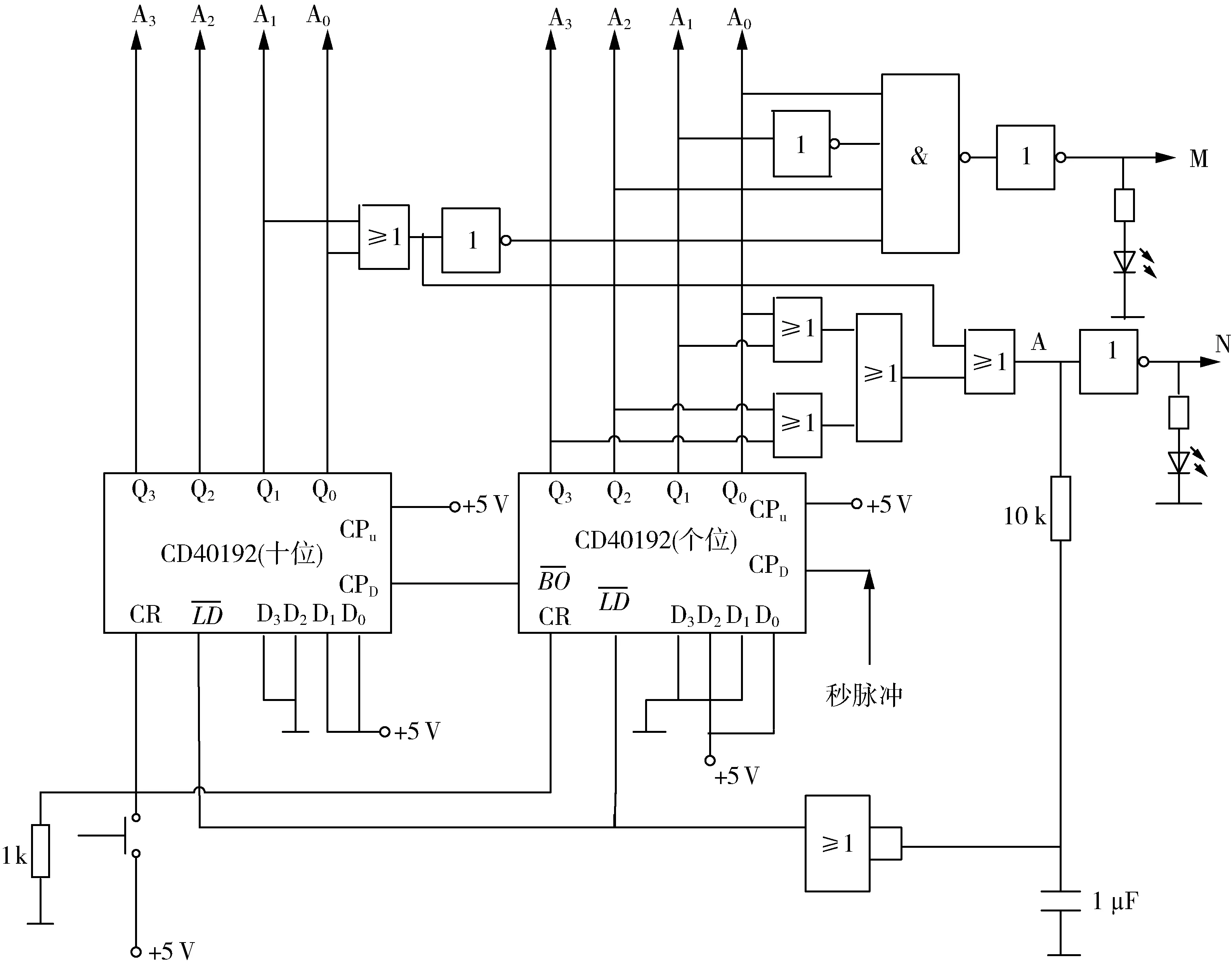

我们在设计一个交通信号灯控制电路时,必不可少地要用到倒计时电路.实训时的交通信号灯电路是从35 s开始倒计时的,倒计时电路如图3所示.电路要求一上电就复位,显示屏显示00,然后很快置数到35并开始倒计时.在计时到00 s和05 s时需要切换状态,为后续电路服务,因此我们要在00 s时检测出输出端N为高电平1,在05 s时检测出输出端M为高电平1,其余时刻这两端均为低电平0.这里的高电平1可以用发光二极管点亮的状态来显示.

图3 交通信号灯中35 s倒计时电路

但是,电路在实际运行时,出现了意想不到的现象.这主要体现在两方面:一是电路一上电复位时M端的发光二极管亮了,二是在倒计时至10 s时N端的发光二极管亮了.分析这种现象不难发现,这是由于两片CD40192芯片的时序性造成的.若十位上的192芯片比个位上的192芯片传输速度快,则在从复位显示00到置数为35的极短时间内,可能瞬间就会出现05这个数,此时M端就输出高电平;从10计数到09的极短时间内,可能瞬间就会出现00这个数,此时N端就输出高电平.

基于以上分析,我们对电路做了改进,分别在采集点M和N之前的电路上加了由10 k电阻和1 μF电容构成的延时电路,如图4所示.实践证明,改进后的电路现象正常,圆满解决了时序问题.

图4 改进后的交通信号灯中35 s倒计时电路

2 两片型号不同的芯片相互通讯时存在的时序问题分析

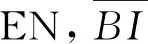

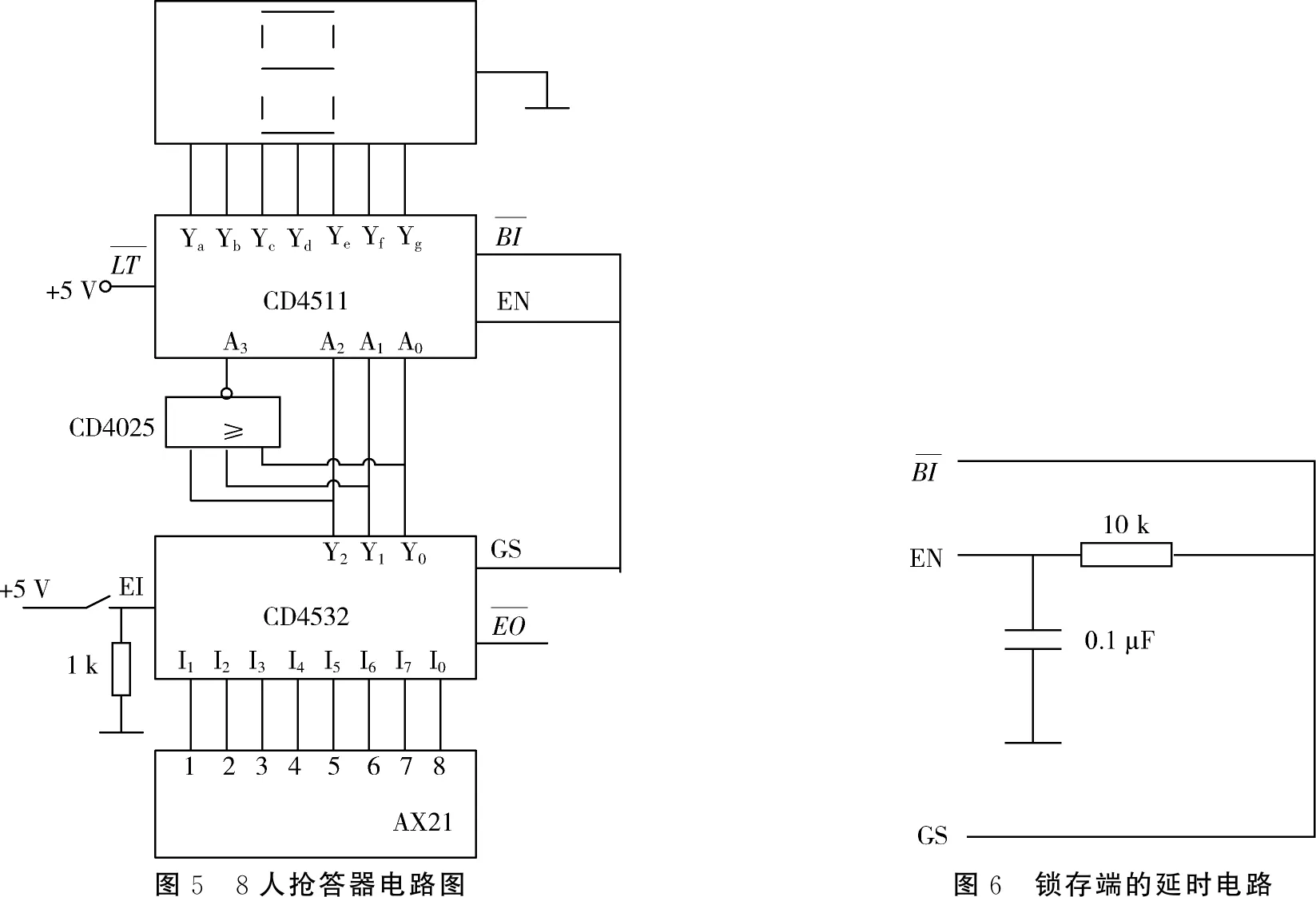

一个电路中经常用到多个不同型号的芯片,电路工作时,其中一个芯片会发出不同的信号,有向主通道发出的信号,也有向控制通道发出的信号,这时不可避免地又出现了因时序问题而导致的不正常现象.下面以8人抢答器电路为例来讨论这个问题.

2.1 主通道信号和控制通道信号之间存在的时序问题

然而,在上电演示电路时,却未出现预期的现象.任何一个钮子开关合上时,显示屏均显示数码“8”,而非正确的台位号.原来,在无人抢答时显示屏本应显示8,只是电路将8消隐掉了;在有人抢答时,消隐解除,然后将8锁存住了.很明显,这是时序问题造成的.有人合上开关抢答时,编码器CD4532同时发出两路不同的信号,即主通道信号和控制通道信号.主通道信号要经过或门CD4025和译码器CD4511两个芯片进行传输,而控制通道信号则只通过一根导线就传过去了,因此控制通道信号一定比主通道信号传输得快.要解决这个问题,可将控制通道信号滞后,对锁存端作一个延时,如图6所示.锁存端作了适当的延时后,电路能够正常地锁存了.实践证明,主通道信号和控制通道信号之间确实存在时序先后问题,而这种改进后的锁存电路的确是解决这个问题的办法之一.

图5 8人抢答器电路图图6 锁存端的延时电路

特别指出,锁存端的延时电路中电阻和电容的参数应该反复调试,调至刚能将抢答上的选手号码锁存住为止,尽可能使延长时间越短越好.因为延长时间若太长,两个人几乎同时抢答时,速度稍快的那人的台位号还没来得及锁存,稍慢的那人的号码却被抢先锁存了.

2.2 控制通道不同信号之间存在的时序问题

3 结语

时序,即时间的先后顺序,数字电路中芯片级联时的时序问题指信号同时通过不同芯片传输时的先后顺序或传输快慢问题.这种时序问题在教材中一般不会分析讲解,理论上也很难涉及到,我们只能在电路上电运行过程中才能发现并及时想办法解决.文章中所举实例均是实验实践中真正出现过的现象及问题,我们深入分析研究它们,不仅对提升自身的实践能力有很大帮助,同时也对设计实际的综合应用电路积累了丰富而全面的实践经验.因此,我们在设计电路时,不仅要考虑逻辑关系,更要考虑时序问题,只有这样,我们才能很好地将理论和实践融为一体,才能设计出更具可行性的电路.

——浙江舟山港主通道百年品质工程建设的理念与措施