基于FPGA的复杂脉冲调制序列测量技术

李强 李金山

【摘 要】本文介绍了复杂脉冲调制序列测量的原理及设计思想,分析了触发屏蔽系统的实现方法,并成功应用于某型号峰值功率分析仪中。结果表明,触发屏蔽系统可以实现复杂脉冲调制序列的稳定测量。

【关键词】脉冲调制序列;触发屏蔽;触发信号

中图分类号: TN24;TN791文献标识码: A 文章编号: 2095-2457(2019)22-0054-002

DOI:10.19694/j.cnki.issn2095-2457.2019.22.023

0 引言

目前,峰值功率分析仪可以对周期性脉冲调制信号进行二极管检波得到脉冲包络,通过随机取样实现信号波形的稳定显示[1]。而雷达、遥感追踪、核磁共振成像和无线通信应用如TDMA、GSM等复杂调制信号如图1所示,脉冲序列在时域上是不规则分布的。由于脉冲序列的非周期性,峰值功率分析仪无法稳定触发这种类型的脉冲信号。

1 触发屏蔽系统

1.1 触发屏蔽系统原理

对于图1所示复杂脉冲调制序列,在较长时间内是重复的周期信号,但在短时间内则不是。峰值功率分析仪可以在脉冲上升沿触发,但脉冲序列在一个周期内有3个触发点,触发脉冲是随机的,因此实际测量中会出现测量波形混叠现象[2]。为解决这个问题,本文采用了触发屏蔽系统,即在每次触发之后加入一定时间间隔,在这段时间内禁止触发,使得每次触发总是从相同脉冲边沿开始,从而得到稳定的波形显示。同时完成时间延迟触发和事件延迟触发功能,实现脉冲序列中任意脉冲边沿作为触发沿,完成快时基下任意脉冲边沿的细节测量。

图2是具有触发屏蔽功能的峰值功率分析仪原理框图,触发屏蔽功能在FPGA内部实现。微波毫米波脉冲调制信号经峰值探头检波和对数放大后进入峰值功率分析仪主机的前置放大器,信号经前置放大后,进入后置放大器。探头输入信号经前置放大器和后置放大器调整为合适电平,进入ADC,在时基控制单元采样时钟下将信号转换为n位并行数字信号。

经前置放大器的信号同样输入到触发单元,与触发电平比较产生触发信号(TRIG),触发信号输入到时基控制单元,此时CPU产生采样开始信号使能时基控制单元。时基控制单元接收使能信号后,发送采样时钟信号到ADC响应触发信号。同时,采样时钟使用时基控制单元的地址计数器来计数,n位并行数字信号在采样时钟下存入存储器,存储地址由地址计数器产生。当地址计数器计数到预置值时,时基控制单元产生采集完成信号到CPU,CPU将需要的波形数据从存储器读出并处理后到显示。然后CPU再次发送采样开始信号给时基控制单元开始新一轮的数据采集过程。

触发信号(TRIG)同时输入到触发屏蔽单元,触发屏蔽电路产生触发屏蔽信号,响应触发信号上升沿。触发屏蔽信号期间禁止其他触发,这段时间内触发屏蔽信号一直为高。为高的时间间隔是由CPU控制实现,触发屏蔽单元可以通过调整触发屏蔽信号的时间间隔提供同一触发脉冲沿到时基控制单元。存储器在每一个采集周期的同一个点开始数据采集,因此,重复波形可在显示屏幕上稳定显示。

1.2 触发屏蔽功能的实现

图3是图2中的触发屏蔽单元,在FPGA内部实现。触发屏蔽计数模块输入端包括门信号GATE和触发屏蔽计数器HOLDOFF_CNT,由CPU提供,时钟信号CLOCK由外部晶振输入至FPGA倍频产生,触发屏蔽信号HOLDOFF_TRIG为D触发器输出。触发屏蔽计数模块输出TRIG_CLR输入到D触发器的D端,同时连接至非门输入端。D触发器时钟输入端连接时钟信号CLOCK,输出Q端和非门输出端均连接与门输入端相与,与门输出端连接非门输入端,与门输出端连接到D触发器的CLRN输入端,D触发器的D输入端和PRN输入端接高,时钟输入端连接TRIG,输出端为触发屏蔽信号HOLDOFF_TRIG,并连接到触发屏蔽计数模块输入端。

触发屏蔽信号HOLDOFF_TRIG进入时间延迟触发模块和事件延迟触发模块的输入端,时间延迟触发模块的输入端还包括时间延迟门信号TIME_GATE和时间延迟计数器TIME_CNT,由CPU提供,时间延迟触发模块输出时间延迟触发信号TIME_TRIG。事件延迟触发模块的输入端还包括事件延迟门信号EVENT_GATE和事件延迟计数器EVENT_CNT,由CPU提供,事件延迟触发模块输出事件延迟触发信号EVENT_TRIG。时间延迟触发信号TIME_TRIG、事件延迟触发信号EVENT_TRIG和触发屏蔽信号HOLDOFF_TRIG输入到选通开关,输出系统触发信号SYS_TRIG。

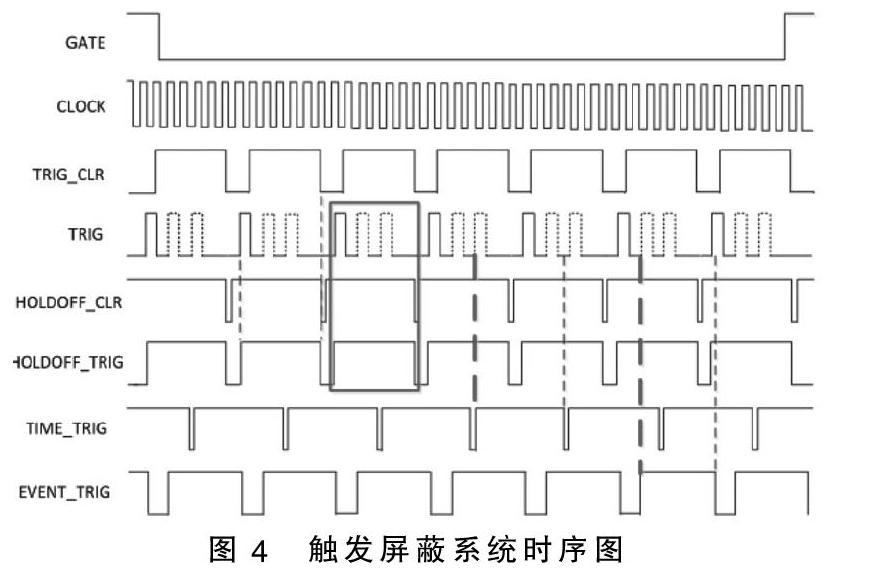

图4是图3中主要信号时序关系图。输入到触发屏蔽计数模块的门信号GATE拉低时,在触发屏蔽信号HOLDOFF_TRIG的上升沿开始计数,触发屏蔽计数器的输出TRIG_CLR拉高,当计数到预置值时,TRIG_CLR拉低。D触发器的输出与TRIG_CLR经过非门和与门的组合后产生HOLDOFF_CLR信号,该信号在TRIG_CLR信号拉低时变为低电平并维持一个时钟周期后变高,然后输入到D触发器的CLRN输入端。当TRIG_CLR为低电平时,D触发器的输出端HOLDOFF_TRIG为低电平,当TRIG_CLR为高时,使能D触发器,在此期间检测TRIG上升沿后HOLDOFF_TRIG拉高,当TRIG_CLR再次拉低时,HOLDOFF_TRIG变低。因此触发信号TRIG为虚线的脉冲被屏蔽,HOLDOFF_TRIG仅捕获触发信号TRIG的第一个脉冲上升沿。

当输入到时间延迟触发模块的门信号TIME_GATE拉低时,在触发屏蔽信号HOLDOFF_TRIG的上升沿开始对延迟时间计数,计数完成后时间延迟触发信号TIME_TRIG拉低,并在之后触发信号TRIG的第一个上升沿,将时间延迟触发信号TIME_TRIG拉高,然后继续检测触发屏蔽信号HOLDOFF_TRIG的上升沿,这样可以得到任意延迟时间后的脉冲信号。

当输入到事件延迟触发模块的门信号EVENT_GATE拉低时,在触发屏蔽信号HOLDOFF_TRIG的上升沿開始对延迟事件个数(触发信号TRIG上升沿)计数,计数完成后事件延迟触发信号EVENT_TRIG拉低,并在之后触发信号TRIG的第一个上升沿,将事件延迟触发信号EVENT_TRIG拉高,然后继续检测触发屏蔽信号HOLDOFF_TRIG的上升沿,这样可以得到任意延迟事件后的脉冲信号。

2 结束语

通过设置合适的触发屏蔽时间,可以实现复杂脉冲调制序列的稳定测量,另外,通过事件延迟和时间延迟的设置,可以选择脉冲序列中的特定信号进行触发,并通过时基的设置,观测当前波形的上升时间等细节信息。

【参考文献】

[1]李金山,吕大伟.随机取样在峰值功率分析仪中的应用[J].国外电子测量技术,2008,27(3):62-64.

[2]孙万荣.数据采集系统中触发采集控制电路的设计[J]. 电子技术应用,1997,7(4):31-35.