绝缘栅双极晶体管(IGBT)表面耐压结构仿真研究

范晓波

(西安电力电子技术研究所,陕西 西安 710077)

随着电力电子技术的迅猛发展,为了进一步满足市场的需求,IGBT 器件的电压也做的越来越高。由于实际的PN 结始终存在着中断面以及会有部分暴露于硅片表面,使得器件的耐压达不到设计指标。为了获得理想的击穿特性,本文对器件的表面终端结构进行计算机仿真,为保证芯片耐压提供重要的依据。

1 表面击穿及终端结构的理论分析

1.1 表面击穿的原理

IGBT 芯片采用多元胞并联技术,单元之间不存在击穿问题,但最外侧的元胞与衬底之间存在很高的电势差,PN 结在这些区域由于受柱面和球面结曲率的影响,电场要远远高于体内的平面结,使器件的耐压水平大为降低。对这些区域采取保护,降低其峰值电场以提高击穿电压就变得尤为重要。

1.2 表面终端结构

IGBT 作为平面器件,其终端保护技术分为场限制环和场板两大类,旨在降低表面处的电场,提高器件的耐压。但实践表明,场板技术过分依赖其本身的长度、氧化层的厚度以及衬底的掺杂水平。而场限制环技术又对环间距极其敏感,随着器件电压水平的不断提高,发现其分压的能力在不断下降,要想提高器件的耐压水平,必须采用多环系统,但势必会减小芯片的有效面积,使得通流能力大为减弱。因此,本文采用一种部分覆盖的环场板混合终端结构来优化器件的耐压水平与通流能力之间的矛盾。

2 表面终端结构的计算机仿真

本文针对耐压水平为3300V 的表面终端结构进行了仿真。采用14 环系统,分别对其电势、电场及击穿特性进行了模拟。

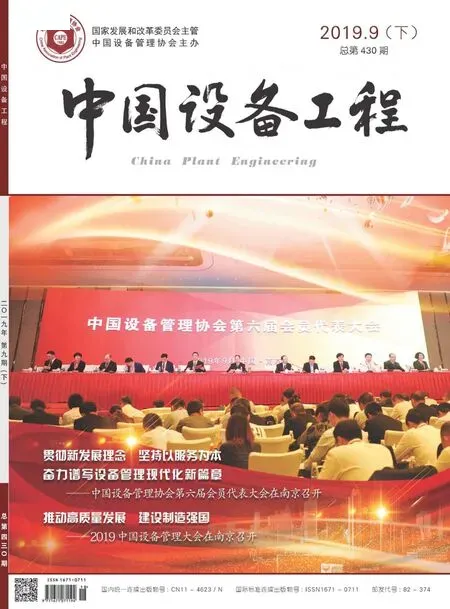

图1 终端的二维电势分布

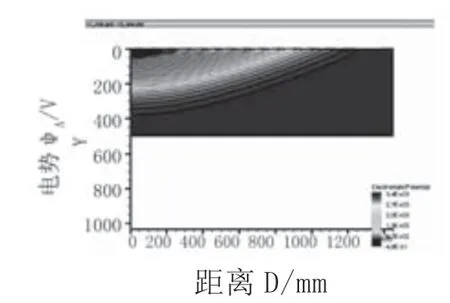

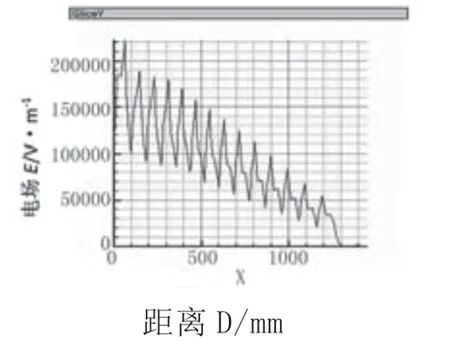

图2 1 终端的二维电场分布

2.1 终端结构的二维物理特性模拟

(1)终端的二维电势和电场分布。如图1、图2,电压等势线由主结向外环扩展,且在各个环间均匀分布,表明电压在各个环间均匀分布。在PN 结表面处,电场逐渐从主结处降低。

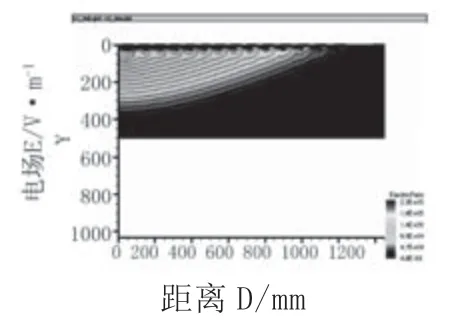

(2)终端表面电势和电场的分布。如图3、图4,电势在各个环间均匀分布,且主结承受的电压最高,最外环承受的电压最低。电场从主结处开始近乎线性的下降,在主结的拐角处产生了最强电场,远高于表面电场的最大值。

图3 终端表面电势的分布

图4 终端体内电场的分布

2.2 击穿特性的仿真

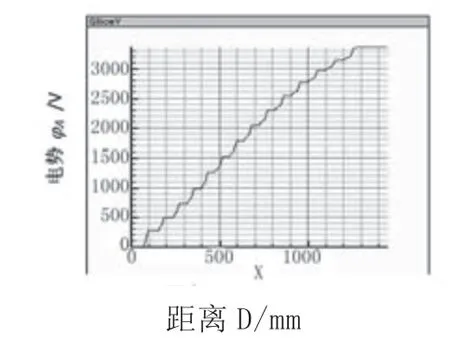

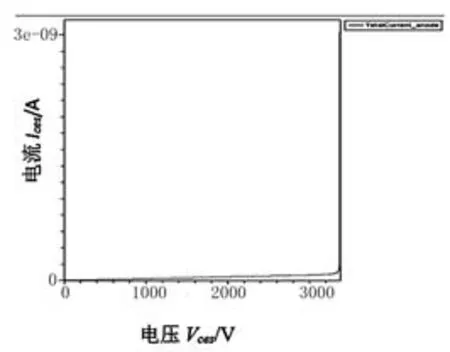

如图5,击穿电压大于3300V,且表现出硬的击穿特性。

3 结语

对IGBT 的表面终端结构进行计算机仿真研究。通过研究14 环系统,结果表明,高压平面器件为了提高耐压水平,必须采用多环系统,随着电压的进一步提高,环数也必须增加以满足耐压的需要。

图5 击穿曲线