多电平闪存信道下阈值电压高效检测算法

范正勤,韩国军

广东工业大学 信息工程学院,广东 广州 510000

随着半导体制程工艺的进一步缩小、多电平存储技术的使用,存储单元成本大幅下降,NAND固态数据存储已广泛应用于各种消费类电子产品及部分数据中心。对于NAND闪存器件,存储密度提升的同时,存储单元受到的噪声干扰进一步加剧,导致数据存储可靠性降低[1]。一般数据存储误码率要求必须低于10-15。相较于使用硬判决译码方法的Bose-Chaudhuri-Hocquenghem (BCH)纠错码,低密度奇偶校验(low-density parity-check,LDPC)纠错码使用软判决译码方法,能极大地降低误码率[2]。多种噪声引起阈值电压偏移而产生误读数据,单元间干扰[3]和持久性噪声[4]是制约NAND闪存数据存储可靠性的主要噪声。目前,为了补偿噪声对阈值电压的影响,闪存采用重读机制[5-8]。动态优化读参考电压[7-11]以适应阈值电压的偏移,采用优化的读参考电压可以获得最低的原始误码率,从而达到改善存储可靠性的目的。在读电压检测范围内,Cai等[7]提出等间隔降低读参考电压操作,该方案可以降低阈值电压检测的范围。

针对阈值电压检测时读操作带来的时延问题,通过对重叠区的原始误码率分析,本文提出了非均匀迭代更新读电压优化方案,该方案有效地降低了读操作的次数。

1 阈值电压检测

1.1 系统模型

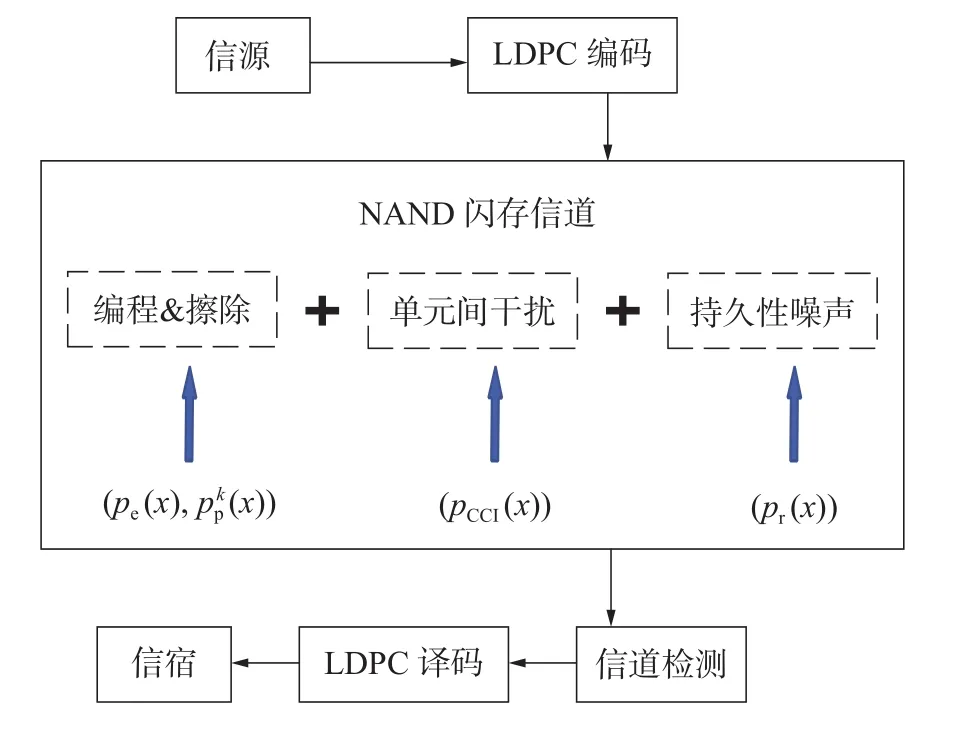

数据闪存系统模型如图1所示,数据经过LDPC编码后通过编程和擦除操作写入闪存单元;经过信道噪声干扰后(单元间干扰和持久性噪声),单元阈值电压产生偏移造成数据误读,需要进行信道检测优化;读操作得到单元对应的对数似然比信息,再通过LDPC译码算法进行纠错处理[1-2,12]。

图1 系统模型

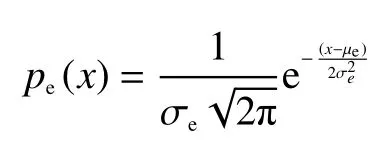

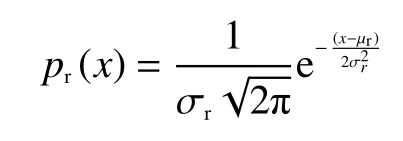

1)擦除操作:数据写入单元前必须要先擦除。擦除状态的阈值电压服从高斯分布。擦除状态的阈值电压概率密度函数如下:

式中μe和σe分别表示擦除状态的均值和方差。

2)编程操作:ISPP技术应用于写入数据。擦除状态的阈值电压服从均匀分布。第k个编程状态的阈值电压概率密度函数如下:

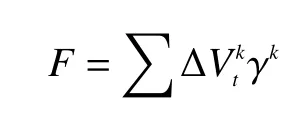

3)单元间干扰(cell-to-cell interference, CCI):相邻单元间干扰是由于寄生电容耦合效应引起的,会使阈值电压向右偏移。

4)持久性噪声(retention noise):持久性噪声是由于氧化层电荷泄露引起的,会使阈值电压向左偏移。持久性噪声服从高斯分布,概率密度函数建模如下:

式中:x0,At,Bt, αi和 αo都是常数;T表示持久性噪声时间;p表示编程擦除次数。

1.2 读电压优化

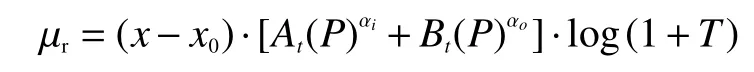

对于MLC型NAND闪存,每个单元写入2 bit信息,阈值电压被划分为4种存储状态(11,10,00,01)。如图2所示,Ⅰ表示经过编程和擦除操作后的阈值电压分布,进行数据写操作;Ⅱ表示经过单元间干扰,单元间干扰使阈值电压向右偏移,根据文献[3]进行对数似然比(log-likelihood-ratio, LLR)计算;Ⅲ表示经过持久性噪声,持久性噪声使阈值电压向左偏移,因此在电压重叠区上,传统的固定读参考电压Vread会引起数据误读。为了克服噪声对信道的影响,通过动态调整读参考电压进行补偿。最后,通过最优读参考电压Vopt读取单元阈值电压对应的LLR值,再通过LDPC译码算法进行解码。

图2 读电压优化

1.3 read-retry机制

当读取数据时,重读(read-retry)机制产生的全部时延[7]为:

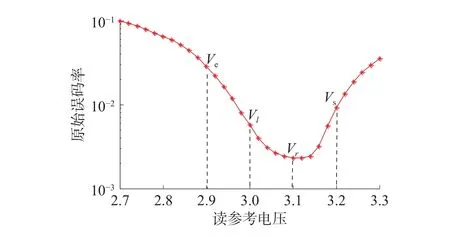

为了弥补噪声对信道的影响,选取低时延的ROR读电压优化技术[7],即原始误码率最低点作为优化读参考电压,算法流程如图3所示。Vs表示每个块中最后编程页的 优化读电压作为阈值电压检测的上限。V1和V2表示每一次需要更新的读参考电压。ROR技术需要向左等间隔偏移Δ去搜索最优读参考电压,直到原始误码率开始增加就立即停止检测,具体步骤如算法1所示。其中,NERR(Vi)表示读参考电压为Vi时的原始比特错误数目,算法1全部读操作次数为

图3 重读机制算法流程

算法1 重读机制

输入:信道电压检测的上限Vs, 电压偏移Δ

输出:优化后的读参考电压Vopt;

2 优化方案

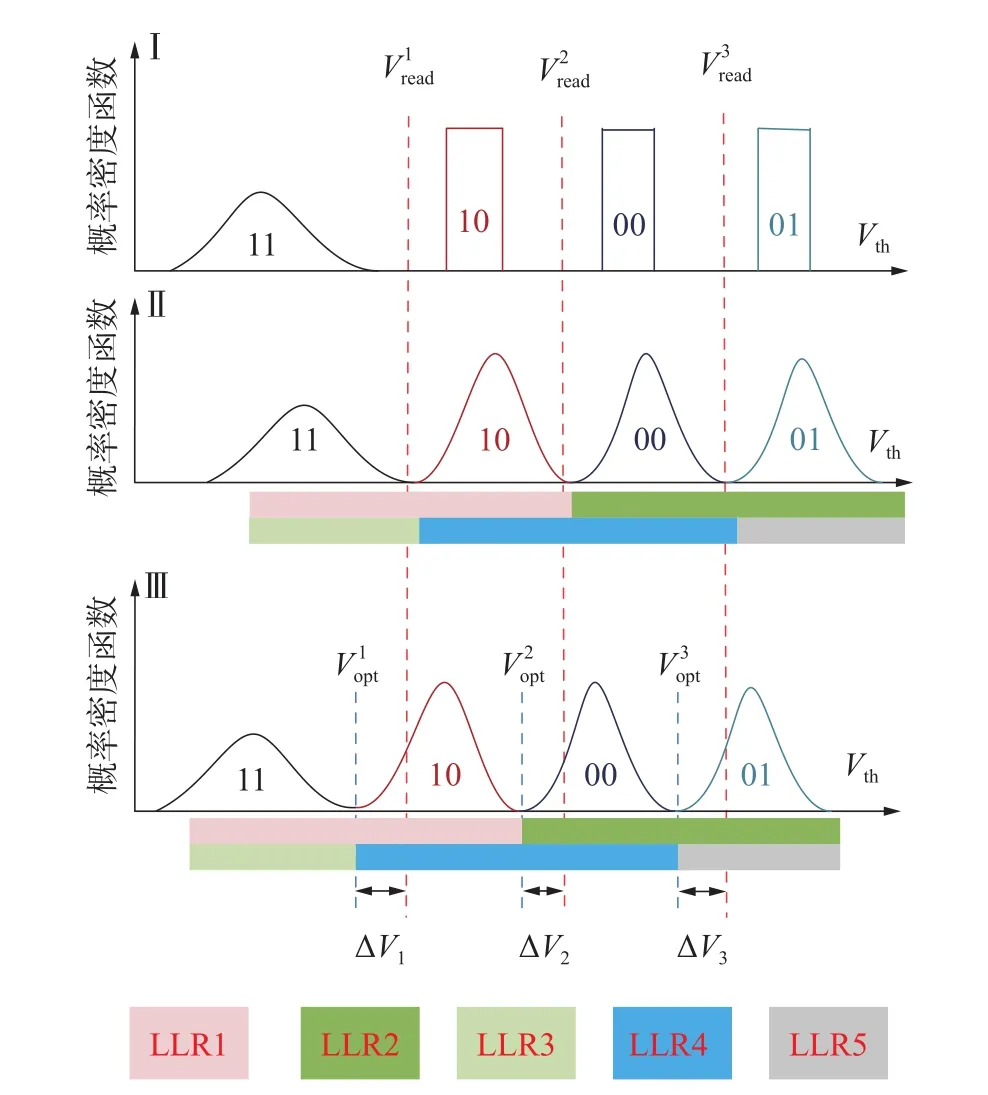

相邻存储状态重叠区的原始误码率分布情况如图4所示,Vs和Ve是信道阈值电压检测的上下限,Vl和Vr是阈值电压检测范围的三等分点。首先,根据噪声特性,电压重叠区上原始误码率呈凹函数分布。其次,三分法求凹函数极值思想应用于读电压优化中,逐步缩小电压检测范围。最后,为进一步减少读操作次数,改进三分法,下一次迭代利用上一次迭代原始误码率较低的读电压,再更新读参考电压,则每一次缩小电压检测范围只需要更新一次读电压。算法流程图见图5,优化方案算法2所示。

图4 原始误码率分布情况

算法2 改进的重读机制

输入:信道电压检测的上限Vs、 下限Ve,最小检测距离 Δ;

Step1 判断 |Vs-Ve|是否小于Δ。若是,转Step7;若否,转Step2;

判断Vmin是 否大于Vmid。若否,转Step5;若是,转 Step6;

判断Vmin是否大于若否,转Step5;若是,转 Step6;

Step7 判断NERR(Vl)是否小于若是,Vopt=Vl;若否,

其中,Step0初始化需要执行2次读操作;Step3表示如果信道阈值电压检测范围缩小为再更新或Step4表示如果信道阈值电压检测范围缩小为再更新或Step5和Step6表示每一次迭代需要执行1次读操作。

3 仿真结果

基于MATLAB平台对闪存信道建模仿真,参数如下:重叠区上信道检测范围

3.1 多噪声信道下原始误码率仿真

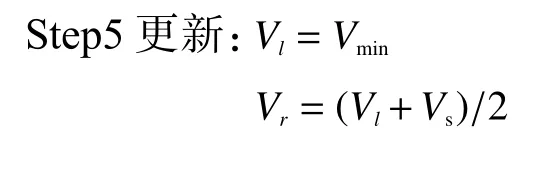

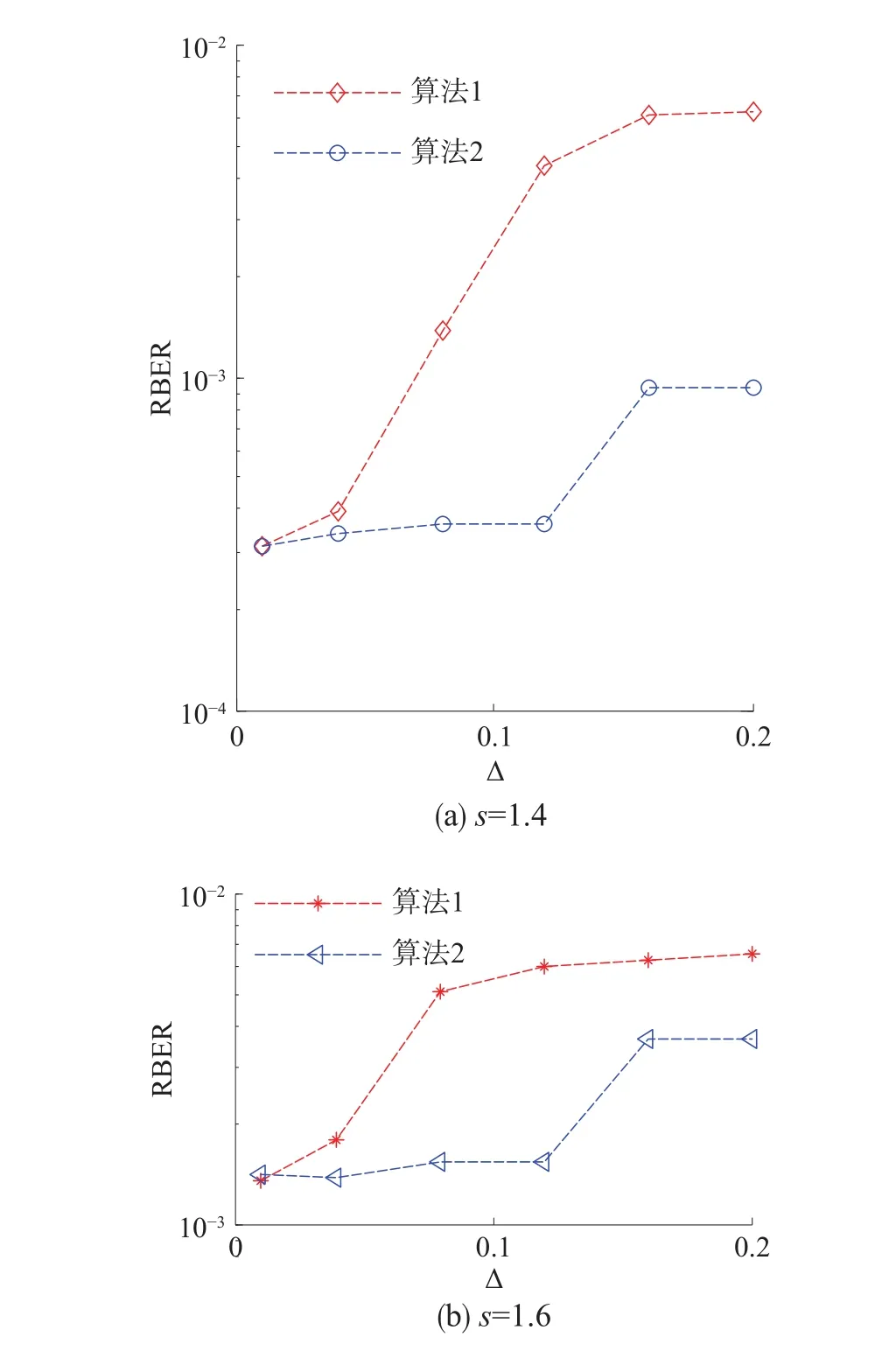

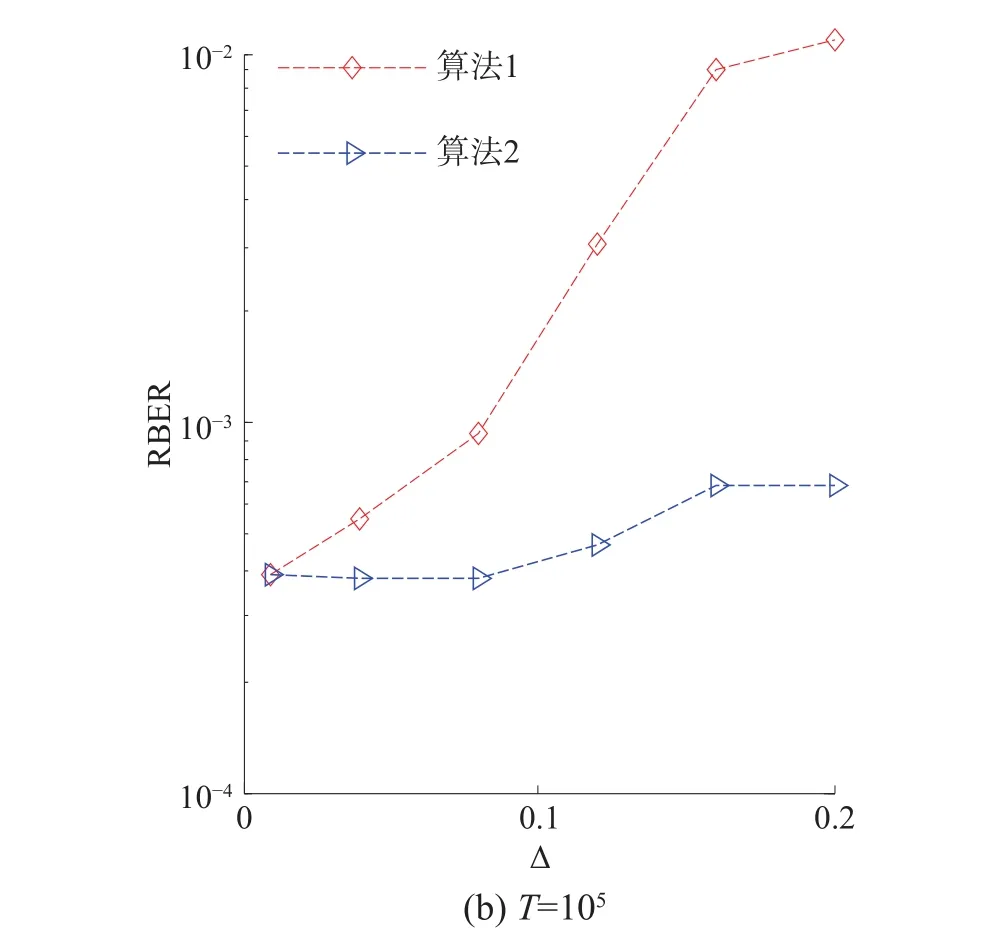

图6、7表示仿真不同的噪声环境下,所提出方案的可靠性。在单元间干扰下,图6表示不同的耦合强度因子s下原始误码率(raw bit error rate,RBER)受的影响;在数据保持噪声干扰下,图7表示不同的持久性噪声时间T下原始误码率受Δ的影响。

仿真结果显示:1)信道检测精度越高,误码率越低,数据存储可靠性越高;2)与算法1相比,在相同的检测精度下,改进的重读机制有更好的纠错性能。

图6 单元间耦合因子s不同时的误码率

图7 持久性时间T不同时的误码率

3.2 高精度信道检测误码率比较

信道阈值电压检测精度越高,误码率越低,纠错性能越好,检测精度 Δ =0.01。信道仿真环境如下:LDPC码率为0.901 4,采用最小和译码算法,最大迭代次数为30,单元间耦合强度因子为1.4。

图8是在闪存信道下不同检测算法的误码率比较。仿真结果显示:1)相对于传统方案,采用阈值电压检测能有效地提升数据存储的可靠性;2)在高精度检测下,改进的重读机制不会有性能损失。

图8 误码率性能比较

3.3 高精度信道检测时延比较

阈值电压检测虽然带来了纠错性能的提升,但会产生较大的时延。读时延与读操作次数成正比,读操作次数越小,读时延越低。单元间耦合强度因子为1.4。相对于目前的重读机制,图9是在闪存信道中改进重读机制的时延降低率。

图9 读时延性能比较

仿真结果显示:1)相对于目前的重读机制,改进的重读机制具有更低的时延;2)随着噪声的增加,改进的重读机制具有更高的时延降低率;3)在高精度、大噪声闪存信道中,改进的重读机制具有更好的性能。

4 结论

基于重叠区错误比特的分布特性,本文提出了一种低时延重读机制优化方案。该优化机制在保证数据可靠性的前提下,可以有效降低读操作次数,具有可行性。另一方面来说,闪存控制器需要执行较多的比较操作,会产生少量延时,但该操作不会对闪存芯片产生影响。通过上述的理论分析及数据仿真,得出以下结论:1)对比现有的重读机制,该优化方案可以有效地提高数据存储的可靠性;2)对比现有的重读机制,该优化方案可以降低大量时延;3)在实际应用方面,该方案具有一定的可行性。