使用动态元件匹配技术的带隙基准源的设计

杨志强,冯全源

西南交通大学 微电子研究所,成都 611756

带隙基准源广泛用于各种模拟集成电路上,其精度以及稳定性直接影响到整体电路的性能,因此高精度以及高稳定性的带隙基准源对于提高整体电路的性能必不可少。传统的带隙基准结构[1-3]在理论上可以达到很高的精度以及稳定性,但是在实际运用中由于工艺的差异会导致元件失配,从而影响基准的精度[4],而且随着工作时间的增加,元件之间的失配也会逐渐变大[5],造成的结果就是基准的稳定性随着时间的增加越来越差。器件的失配严重影响了基准的精度以及稳定性。针对该问题,本文设计了一款全新结构的电压基准源,该基准源充分使用动态元件匹配技术,最大程度地减少了器件的失配。通过仿真表明,该电路能够非常好地改善由于器件失配而造成的精度以及稳定性的恶化。

1 基准源的工作原理

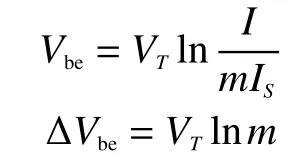

带隙基准的基本原理是正负温度系数抵消,从而减小基准电压随温度的变化。根据参考文献[1],三极管的基极-发射极电压Vbe具有负温度系数,2个三极管的基极-发射极电压之差 ΔVbe具有正温度系数。可以将这2个参数进行线性组合得到:

如果式(1)对温度的偏导为0,该式产生的电压V就是基准电压。

图1为传统的带隙基准电压源电路,QP1与QP2为PNP三极管,前者发射极面积为后者的m倍;OTA为运算放大器,其输出Vref的计算公式为:

图1 传统带隙基准电路

由参考文献[6],运算放大器OTA的作用为:

所以:

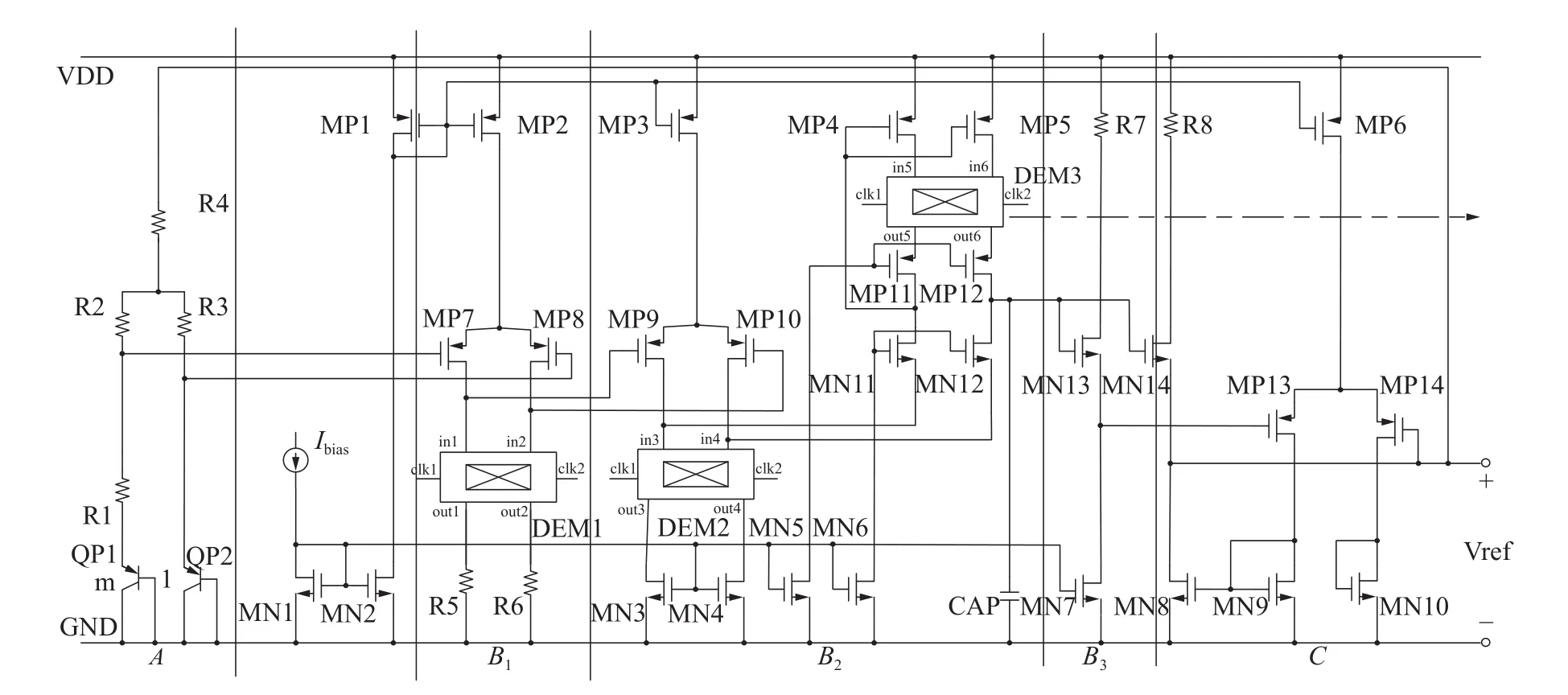

由参考文献[1],可以得到Vbe及 ΔVbe关于温度电压VT的表达式:

所以,式(2)可以写成:

式(4)与式(1)具有相同的结构,式(4)对温度T求导,并令求导结果为0,则有:

由式(5)可以看出,只要选择合适的m、R1、R2、R4,就可以得到与温度无关的基准电压。

式(3)是得到基准电压的核心条件,为保证该式成立,必须使用高增益、器件高度匹配的理想运算放大器。在实际运用中,高增益可以通过多级放大器实现,但是器件高度匹配对电路的结构以及器件的一致性要求非常高,这也是本文主要解决的问题。

2 电路设计与实现

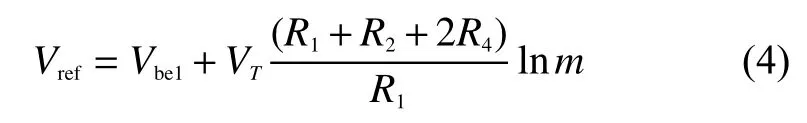

图2为本文提出的电路原理图,该电路由3部分组成,A为基准核心部分,B为运算放大器,C为输出电压稳定电路。该电路的偏置电流Ibias由单独的启动电路提供。

图2 本文提出的带隙基准电路

2.1 电路结构说明

根据工作原理分析,结合图2的A部分,可以得出该基准的输出电压计算公式为:

B部分为运算放大器,为两级放大,第一级B1为普通的双输入双输出的共源差分电路,其增益为:

式中gm7为MP7的跨导。

第二级B2为折叠共源共栅差分放大器[7],其增益为:

式中:gm10、gm12分别为MP10与MP12的跨导;ro10、ro12为MP10与MP12的漏源电阻。由式(6)可以看出第二级增益为第一级的平方,所以具有高增益的特点。

总的增益为两级增益的乘积,能够符合理想放大器高增益的特点。

B3为共漏结构的缓冲器,能够减少运算放大器的功耗以及噪声。

C部分为电压稳定电路,通过负反馈减少由于输入电压的变化带来对输出基准电压的影响。

B部分性能的好坏直接影响到式(3)能否成立,该部分性能指标是增益以及器件匹配程度,前面的分析已经得出该放大器具有大的增益,所以最大的影响来源于器件的匹配程度。

2.2 电路元件失配分析

在2.1节已经分析得出,从增益的角度来讲,该基准运算放大器可以看作是理想的,因此影响运放性能的主要因素是器件的失配。由于运放由差分电路组成,对差分电路来说,器件的失配主要是差分电路两路器件的失配造成的,这些失配为:

1)B1中 MP7与 MP8、R5与 R6的失配;

2)B2中 MP9与 MP10、MN3与 MN4的失配;

3)B2中MP4、MP11 组成的支路与MP5、MP12组成的支路的失配。

对失配造成的影响进行分析,B1中MP7与MP8、R5与R6的失配:假设MP7与MP8的输入电压相等,由于MP7与MP8的失配使流过MP7与MP8的电流产生差异,设差异量为ΔI;假设R5与R6的失配量为ΔR,则由此造成的输出电压失配量为ΔV=ΔIΔR;其他失配造成的影响与上述分析相似。

可以看出,如果可以消除这些器件之间失配,就能很好地保证运放为理想的。

2.3 动态元件匹配

动态元件匹配技术是为了保证差分电路支路信号相等。图3为动态元件匹配等效结构框图,i1,i2,···,in为n个输入信号,o1,o2,···,on为n个输出信号,s1,s2,···,sn为n个开关。动态元件匹配(dynamic elements matching,DEM)电路相当于一个分配器,将n个输入按照一定的概率分配到n个输出,并且保证同一时间点每个输入只有一个输出、每个输出也只有一个输入,该功能由控制信号对开关s1,s2,···,sn的控制来实现。在实际设计中开关由CMOS管来实现。

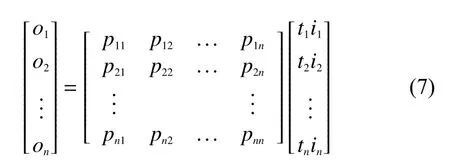

控制信号使用n相不交叠时钟来实现[8],在时钟为高电平时开关开启,低电平时关断。假设每个输入对应的开关开启时间为ti,则可以得出输出矩阵与输入矩阵的关系为:

式中pij为输入ii被分配到输出oj的概率。

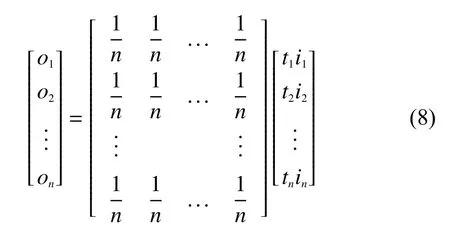

如果了解某一输入的误差大小,则可以赋予该输入特定的权重[9-11],这样可以自主地控制误差的比重。在实际运用中,相同工艺的器件失配率都是一样的,所以采用随机概率,这样在一段时间后概率都相等,为1/n,所以,式(7)可以表示为:

可以得到各个支路的输出都相等:

保证了每条支路的信号都相等,这样就消除了由于器件失配带来的误差。

图 2中,DEM1、DEM2、DEM3为动态元件匹配电路[7],分别用来解决2.2节所提出的3个失配。可以看出它由2个时钟控制,可以得出在本设计中n=2,时钟为2相不交叠时钟。具体的DEM电路及控制时钟如图4、5所示,各开关的开启时间相等设为t。将这些参数带入式(8),可以得出2条支路的输出电压表达式为:

可以得到输出的失配量为0,很好地解决了器件失配造成的输出失配。

图4 动态元件匹配实现

图5 动态元件匹配时钟信号

3 仿真结果与分析

基于BICMOS 0.15 μm工艺,通过Cadence的spectre仿真软件对电路进行仿真。为了说明动态元件匹配技术对于器件失配的改善效果,需要仿真3种电路:加入失配、使用动态元件匹配技术电路(mismatch with DEM),加入失配、没有使用动态元件匹配技术电路(mismatch)以及没有加入失配、理想情况下电路(no mismatch)。分别仿真了这3种电路的温度特性、电压特性以及不同工艺角下的特性。仿真过程中加入失配的方法是对2.2节中提到的器件加入2%的失配[12]。

图6为3种电路在供电5 V、温度233~378 K(-40~105 ℃)条件下的Vref温度特性。对于仿真结果,从整体看,mismatch with DEM与no mismatch的曲线更加接近。在298 K(25 ℃)时,no mismatch的Vref为1.248 7 V;mismatch的Vref为1.270 7 V,产生的误差为22 mV;mismatch with DEM的Vref为1.244 6 V,产生的误差为-4.2 mV,后者减少了81% 的误差。在仿真温度 233~378 K(-40~105 ℃),mismatch与mismatch with DEM相对于no mismatch的最大误差分别为28.4 mV与9.2 mV,后者减少了68%的误差。通过对比可以得出温度变化时,使用动态元件匹配技术的电路能够更好地改善器件失配带来的误差,保证了Vref的精度以及稳定性。

图6 温度特性仿真结果对比

图7为3种电路在温度为298 K(25 ℃)、供电电压为4.5~5.0 V条件下Vref的电压特性。对于仿真结果,从整体看,mismatch with DEM与no mismatch的曲线更加接近。在VDD=5 V时,no mismatch的Vref为1.248 7 V,mismatch的Vref为1.270 7 V,产生的误差为22 mV,mismatch with DEM的Vref为1.244 6 V,产生的误差为-4.2 mV,后者减少了81%的误差;mismatch、mismatch with DEM相对于no mismatch的最大误差分别为23 mV与7 mV,后者减少了70%的误差。通过由整体到细节的对比可以得出:在输入电压变化时,使用动态元件匹配技术的电路能够更好地改善器件失配带来的误差,保证了Vref的精度以及稳定性。由于加入固定失配,所以电源电压越低,造成的误差率越高;随着电源电压升高,误差减小。mismatch中由于失配大,误差大,所以在低电压时误差会很大,造成曲线走势与其他2条线不同。

图7 电压特性仿真结果对比

表1为在298 K(25 ℃)、电源电压5 V时,3种电路在不同工艺角情况下的Vref。可以看出在不同工艺角情况下采用动态元件匹配技术的误差更小,且相对没有使用动态元件匹配技术的电路减少的误差最小为68%。

表1 不同工艺角基准电压输出

4 结论

提出了一款基于动态元件匹配技术的带隙基准,该基准能够很好地降低器件失配带来的误差,保证了Vref的精度以及稳定性。

1)通过对电路的温度特性仿真表明,5.0 V供电、温度在 233 K(-40 ℃)~378 K(105 ℃)变化时,相比于没有使用动态元件匹配的电路,该电路最少能够减小68%的误差;

2)通过对电路的电压特性仿真表明,25 ℃、电压在4.5~5.5 V变化时,相比于没有使用动态元件匹配的电路,该电路最少能够减小70%的误差;

3)在不同工艺角情况下,相比于没有使用动态元件匹配的电路,该电路最少能够减小68%的误差。

由于改善了器件失配造成的影响,可以得出该电路具有高稳定性。本论文只在一种工艺下进行了验证,在不同工艺下是否需要不同的考虑,这是以后需要研究的方向。