强电磁干扰环境下机载总线接口设计与实现

潘 皓,李声飞

(中国西南电子技术研究所, 成都 610036)

随着现代航空电子技术的发展,航电系统集成了大量的通信、导航、雷达等无线电设备,干扰源覆盖了甚低频、载频、射频及微波等频段,信号发射功率范围为10~50 dBm。在此环境下,因设备间通信误码率提高会导致系统工作异常,严重时将影响飞行安全,属于强电磁干扰环境[1-2]。本文提出了一种适用于强干扰环境的总线接口单元,采用改进的摩尔投票算法对采样电平进行加权,降低了通信误码率,提高了总线的可靠性;此外,在物理层和应用层对总线接口进行标准化设计,将CAN、RS422/RS485、LVDS等串行总线进行集成设计,对数据收发驱动器、总线控制器等器件选型进行统一规划,解决了各设备间接口规范、电气标准[3]不统一而带来的互连互通问题。通用总线接口单元主要用于航电分系统内设备互连,适用于对实时性、可靠性、功耗、体积、成本等要求较高的场合。

1 系统结构及原理

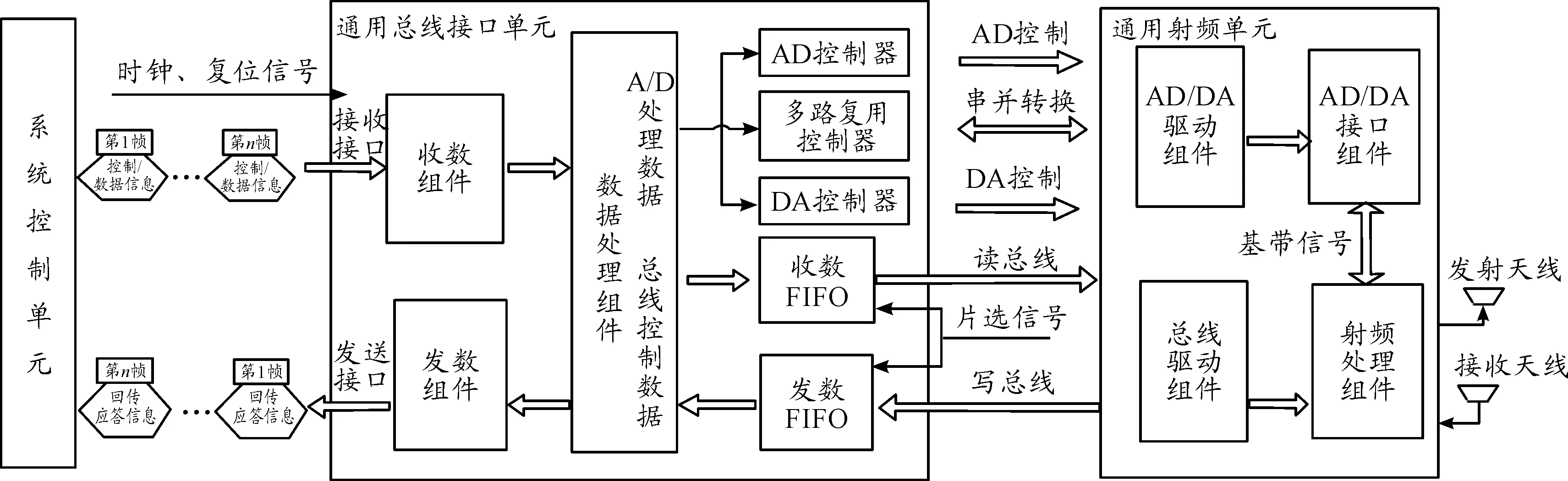

典型的机载通信链路系统[4-5]由系统控制单元、通用总线接口单元、通用射频单元组成,原理如图1所示。系统控制管理单元主要实现航电总线接口功能,用于连接航电主干网络,如FC、AFDX、1553B等总线;采用高速数字信号处理器作为主控,通过同步总线与通用总线接口单元通信,完成系统控制指令和数据下发,如配置系统工作模式、工作参数等控制命令;接收来自通用总线接口单元的应答数据帧,并采集系统工作状态和健康状况。

通用总线接口单元是系统控制单元与通用射频单元间的纽带,完成系统控制指令的转发和处理。收数组件接收来自同步总线的数据帧和命令帧,对帧信息进行缓存和解析,并将有效帧负荷传给数据处理组件。数据处理组件对帧负荷进行解析和处理,将有用信息分成A/D数据、总线控制数据,并分别传给对应的通道,其中A/D数据传给A/D控制器、多路复用控制器、D/A控制器,完成对前端射频单元A/D的控制和管理;总线控制数据传给收数FIFO缓存,缓存后通过读总线传给后端射频模块,用于射频模块控制,如模式选择、宽窄带选择、滤波器设置。数据接收为发送的逆过程,通用射频单元接收数据后进行A/D转换,将数字信号通过总线接口单元缓存和处理后,送至系统控制单元。

图1 典型机载链路通信系统原理框图

2 数据处理流程

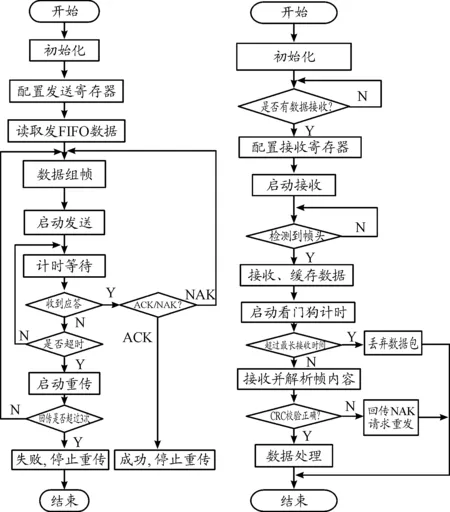

通用总线接口的数据发送流程如图2所示,处理器启动后运行初始化函数,初始化对外I/O接口、配置中断触发模式以接收外部中断,然后进入主流程。当判断有数据待送时进入发送流程,配置发送寄存器,包括设置发送波特率、帧格式、选择发送电平(如RS422、RS485、RS232等)、校验方式等参数,然后读取发FIFO数据并对数据组帧,增加帧头、帧尾、源/目的地址、校验信息,一帧数据准备好后启动发送程序发送数据,并启动接收计时器等待回传信息。如果收到应答信息,则判断应答为ACK帧还是NAK帧,若为NAK帧表示接收方数据校验失败请求回传,则重新组帧并发送。如果接收为ACK帧表示接收方已收到数据且校验成功,则发送成功,停止重传。如果未接收到任何应答帧信息,则判断接收是否超时,如果未超时则继续等待接收应答帧信息,如果超时则启动重传机制对数据帧重传,如果重传超过3次仍未收到应答帧,重传失败,停止重传。

当判断到有数据到来时进入接收流程,如图3所示。首先配置接收寄存器,包括设置接收波特率、缓存大小、中断触发方式等参数,然后启动接收进程。检测是否有帧头,如果没有帧头则继续等待,检测到有帧头就开始接收并缓存数据。随后启动看门狗计时器,判断是否超过最长接收时间,如果超过则丢弃当前数据包,否则解析接到的帧内容并进行CRC校验,如果校验失败则回传NAK帧请求发送方重传,校验成功则将数据传给数据处理流程,接收流程结束。

3 改进的摩尔投票算法

传统的电平采样方法多采用单次采样,该方式易受电磁干扰而造成通信错误,当误码率超过阈值时会导致系统工作异常。而多次采样[6]方法中,传统的摩尔投票判决算法[7]能在一定程度上消除噪声对判决结果的影响,但由于未对判决因子进行加权处理,总线传输误码率难以进一步降低。

通过分析总线电平特性可知,信号在保持期间电平较为稳定,而在建立或翻转时波动较大,根据这一特性对摩尔算法进行改进,具体方法:在整个电平范围内,采用多个采样点对目标进行判决,根据每个采样点位置不同分配不同的加权因子,信号中间位置分配较大权重,依次往两端递减。加权因子设置为服从标准正态分布[8]的函数,统计在整个样本空间内目标的概率值η如下:

(1)

式(1)中:η为目标概率值,N为采样次数,Xi为第i次采样值,φ(Xi)为Xi的加权分布因子。用为简化计算,将该因子的分布函数,采用标准正态分布表示如下:

(2)

图2 数据发送流程框图 图3 数据接收流程框图

改进的摩尔投票算法的判决流程如图4所示,首先采集样本空间内Xi,对采集到的样本按正态分布概率函数进行查表加权,依据式(1)计算出目标概率η,若η大于设定阈值则判断为目标,流程如图4所示。

图4 摩尔投票算法流程框图

4 算法实现

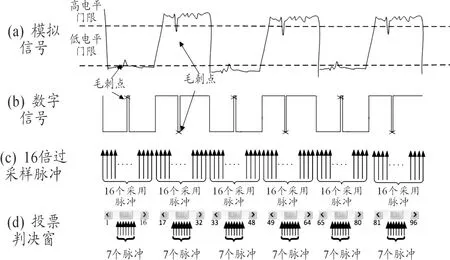

利用FPGA高速并行处理的优势,实现了改进的摩尔投票算法,流程如图5所示,在高精度晶振输出的时钟控制下,通用总线接口内部FPGA对接收到的串行总线信号进行采样判决。图5(a)为串行总线的模拟信号,速率为3.125 Mbit/s;模拟信号由于受到周围电磁环境、传播路径影响,信号局部会随机出现毛刺,设置高电平门限、低电平门限作为模拟信号数字化的基准。图5(b)为经数字化后的信号,模拟信号的毛刺超过预先设定的高电平门限、或者低于预先设定的低电平门限,数字化后信号就会出现“毛刺点”;如果采样时刻在毛刺点附近,就会影响到采样结果;图5(c)为过采样时钟信号,频率为50 MHz的高速脉冲,对3.125 MHz的串行数字信号进行16倍过采样,每个比特电平持续16个采样周期;图5(d)为FPGA内设置的宽度为16个采样周期的投票判决窗口。用改进的摩尔投票算法,确定该比特电平值。具体方法如下:通过查表法对所有采样值进行加权求和,计算出电平“1”的值,当“1”值大于0.35时判决该比特电平值为“1”,否则判决该比特电平值为“0”。

图5 改进的摩尔投票算法流程

5 实验结果与分析

为了验证通用总线接口单元通信可靠性和抗干扰能力[9],搭建如图6所示试验环境。在复杂电磁环境下,选取设备A作为数据发送设备,将测试数据发送至总线接口单元,总线接口单元对接收到的测试数据进行处理,并将处理后的结果发送至设备B,设备B上运行统计软件,对通信误码率、通信报文大小进行统计,并将统计结果传输到监控计算机上显示。

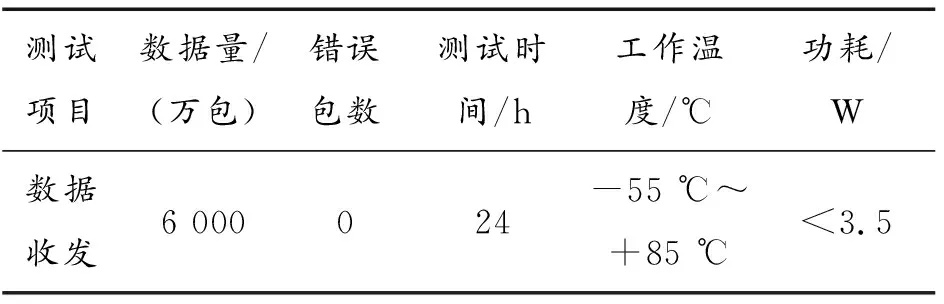

通过温度循环检验总线接口单元环境稳定性,一个循环条件设置为:低温-55 ℃,保温2 h;常温+25°,保温2 h;高温+85°,保温2 h,升降温速率为5(°)/min。经过4个循环共计24 h的进行数据收发测试,在6 000万包(256 Byte/包)大数据量压力测试下,总线通信误码率小于10E-11,测试结果见表1所示。

图6 总线接口单元试验环境示意图

测试项目数据量/(万包)错误包数测试时间/h工作温度/℃功耗/W数据收发6 000024-55 ℃~+85 ℃<3.5

6 结论

本文以机载设备总线通信为背景,设计了一种基于改进摩尔投票算法的总线接口单元,根据采样电平特征,将不同的采样值按正态分布分配不同加权因子,避免了传统贝叶斯分布的随机性,解决了强电磁环境下总线通信抗干扰问题;此外,对设备间串行总线接口进行标准化设计,遵循总线物理层和传输层规范,在应用层上对帧传输格式、校验方式,重传机制等方面进行统一规划,使得各厂家设备在统一的总线规范下进行通信,提升了系统的开放性和通用性。进一步降低强电磁环境下总线误码率、提高设备的容错性[10-11]仍是今后研究的方向。