TPM芯片通信异常问题分析

苏小峰

摘 要:TPM芯片是一種标准的安全加密芯片,能保证系统数据安全,防止攻击者恶意修改数据,Z32H320TC是一款支持TPM2.0规范的可信安全芯片,使用SPI接口进行加密,在使用该芯片时发现TPM芯片经常校验失败,最终定位是CPU的SPI接口速率过高引起的。文章对TPM芯片通信异常问题进行了分析。

关键词:TPM;SPI;加密;接口速率

Z32H320TC是一款支持TPM2.0规范的安全芯片,生产厂商国民技术宣称该芯片为世界首款支持中国密码算法的芯片,在工业及民用领域,越来越多的产品开始使用这款芯片。

1 Z32H320TC上电校验失败

在对Z32H320TC芯片进行打板验证时,发现该芯片在进行算法校验时,有的板子可以成功,有的板子会失败,不同的板子概率不一样,有的设备一直成功。咨询了TPM芯片厂商的FAE,对方回复说华为在某项目中也遇到过类似的问题,最终定位为SPI信号被干扰。

2 校验失败问题分析

在发现问题前期,使用示波器对芯片的电源进行测量,供电电源3.3 V没有明显的波动,且电源纹波在±1%范围内。使用示波器测量芯片复位管脚上下电状态,复位也正常。芯片的电源和复位并不是引起校验失败的主要原因。

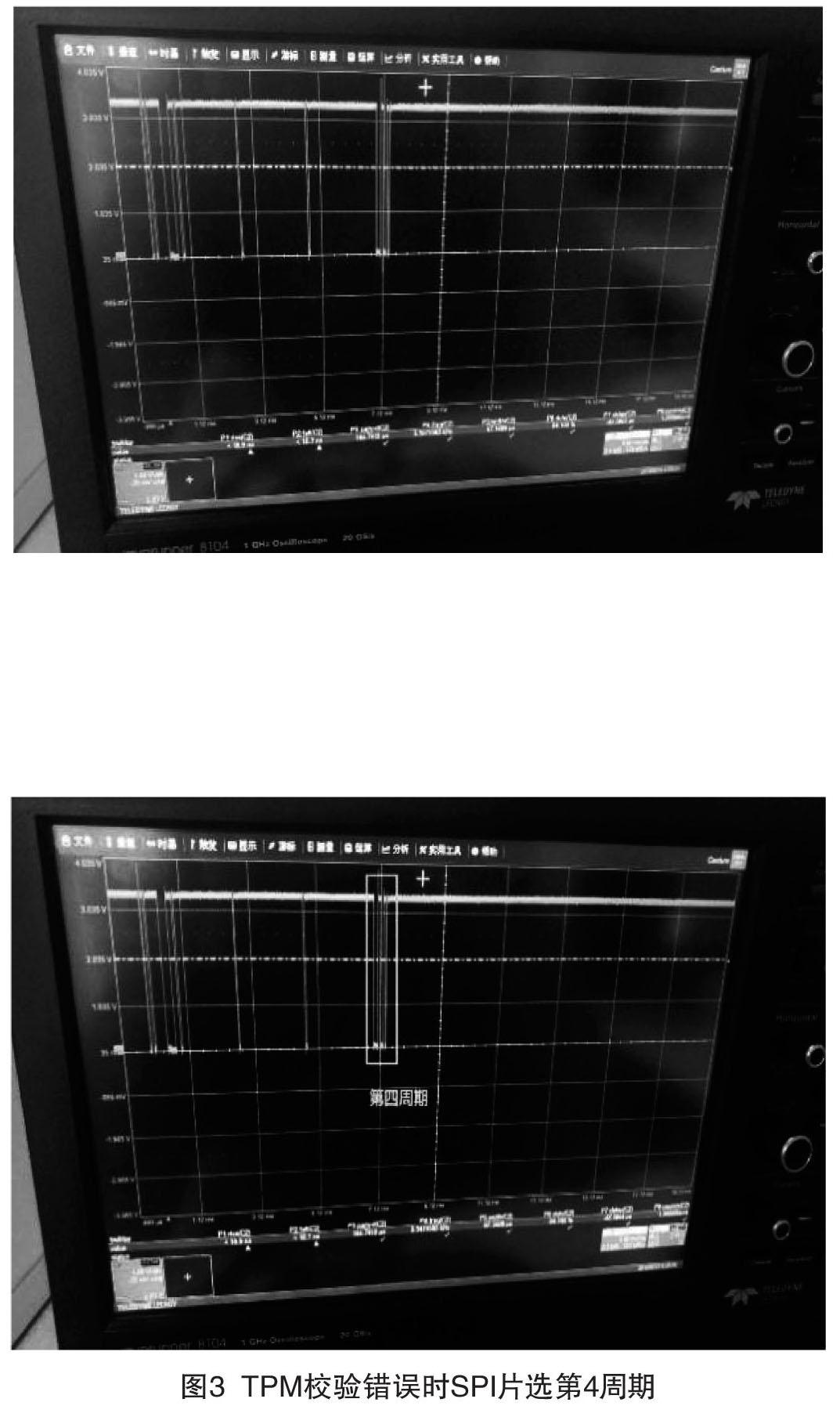

使用示波器对PI_CS_TPM,SPI_CLK,SPI_MOSI,SPI_MISO进行测试时发现,当TPM芯片校验失败,则SPI_CS_TPM,SPI_CLK,SPI_MOSI,SPI_MISO会无持续数据,具体如图1所示。当TPM芯片校验成功,则SPI_CS_TPM,SPI_CLK,SPI_MOSI,SPI_MISO会有持续数据,具体如图2所示。

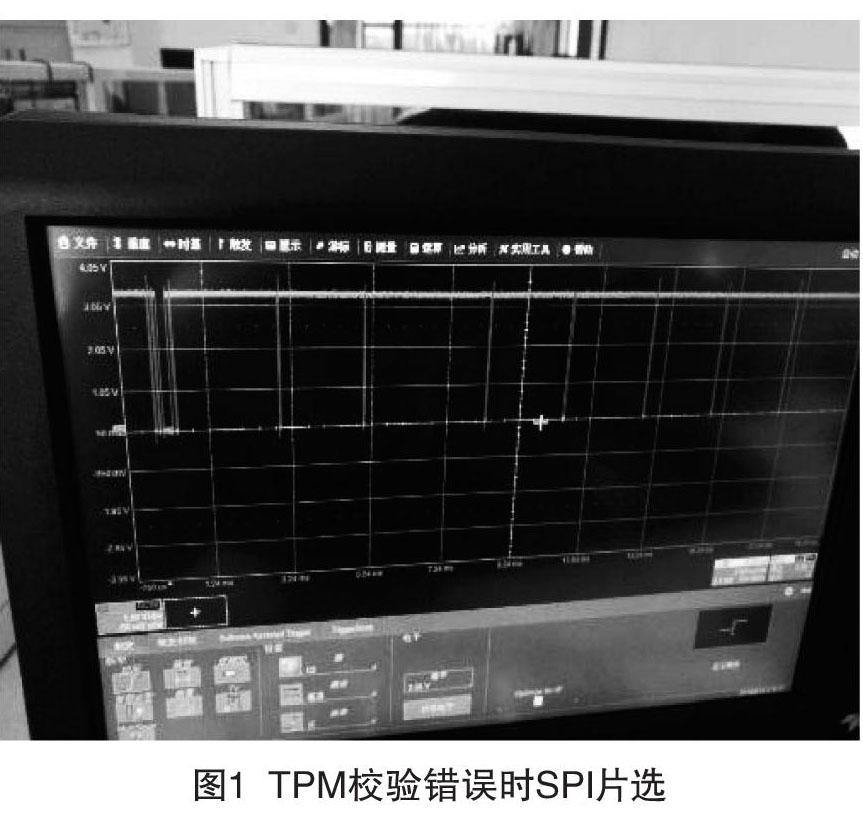

经过几十次波形测试发现,如图3—4所示,只要第4个周期的数据不出现问题,则TPM芯片校验不会出问题。TPM芯片校验不正确,全都是第4个周期波形不正常。

经过多次观察错误/正确数据发现,第4周期前面的数据都是一样的,只有第4周期出现问题。后续通过SPI总线分析仪分析的数据也可以验证这一观点,具体如图5—6所示。

经过多次对比正确、错误数据,通过软件写入的79个数,一直都是正确的,也就是无论TPM芯片是否校验成功,CPU写入的79个数通过SPI总线分析仪分析后,都写入正确。TPM芯片校验不正确时,总是出现在第80个数据。

3 实验结果

无论TPM校验是否正确,SPI总线上前79个数据都是一样的、正确的,如果是总线问题,每次都是第80个数据出现问题有点解释不通。

总线分析仪可以抓到SPI数据,且每次出问题都是SPI总线上的MISO第80个数据出现问题,即TPM芯片回数据出现异常。实际上SPI的MOSI正常,即CPU芯片发送数据正常。SPI总线能被相关设备解析出数据,证明SPI总线应该还是满足规范的。

从总结的信息来看,错误数据都是在同样的时间点出问题,此时开始怀疑是否SPI时序出现问题,是否是CPU和TPM芯片的SPI总线时序经常对不上,导致数据错误,最终影响TPM芯片的校验。

重新整理驱动,发现CPU将SPI总线的速率配置为10 Mbps,对SPI总线来说,10 Mbps速率是比较高速的。而TPM芯片手册并没有描述SPI总线速率的相关信息,后续通过修改驱动,将CPU的SPI总线速率降为5 Mbps以下时,TPM芯片再没有出现过校验不成功的情况。

4 结语

设计并不是简单地把接口连接起来,同样都是SPI总线,由于芯片内部设计的区别,有些SPI总线可以支持高速率,有些则不行。在设计前期要尽量对接口总线的性能有所了解,避免产品阶段出现问题。

Abstract:TPM chip is a standard secure encryption chip, which can guarantee the security of system data and prevent attackers from modifying data maliciously. Z32H320TC is a trusted security chip of TPM2.0 specification, which uses SPI interface to encrypt. When using the chip, it is found that the TPM chip often fails to check, and the final location is caused by the high rate of SPI interface of CPU. In this paper, the abnormal communication problem of TPM chip is analyzed. In this paper, the abnormal communication problem of TPM chip is analyzed.

Key words:TPM; SPI; encryption; interface rate