一种小型化高密度FPGA系统级3D封装电路

杨进

摘 要:本文简要介绍了一种小型化高密度FPGA系統级3D封装电路,详细阐述了该电路的三维架构、电路设计和工艺方案。本设计大大缩小了电路体积;同时具有良好的气密性、高可靠性;PCB layout设计简单,具有较强的实用性。

关键词:小型化;高密度;FPGA;系统级封装;三维集成

中图分类号:TP391.41 文献标识码:A 文章编号:1671-2064(2019)09-0065-03

0 前言

上世纪90年代以来,便携式、微型化电子产品以及航空航天、军事电子进入了一个高速发展时期,要求半导体器件最大程度地实现小型化、轻量化、高密度的同时满足高可靠性。集成电路技术应运而生。然而,目前集成电路的工艺技术已经接近其物理极限,摩尔定律(Moores Law)将无法保持。在这样的背景下,提出了系统级封装(System in Package,SIP),作为“超摩尔定律”(More than Moore)的重要技术。“超摩尔定律”的概念着眼于系统集成的层面,为电子行业的发展提供了新的方向[1-2]。

国际半导体技术蓝图(ITRS,International Technology Roadmap for Semiconductors)对SIP进行了明确的定义:SIP是采用任何组合将多个具有不同功能的有源和无源电子元器件以及诸如MEMS、光学甚至生物芯片等其他器件组装在单一封装中,形成一个具有多种功能的系统或子系统。

SIP采用目前最先进的工艺与技术,主要包括:

(1)材料技术(半导体材料、陶瓷材料、金属材料、金属基复合材料);(2)芯片技术(逻辑芯片、数字芯片、模拟芯片、功率芯片);(3)互联技术(高密度多层互联、芯片与芯片互联、倒装焊接、引线键合);(4)封装技术(BGA、芯片级封装、无源集成);(5)组装技术(层叠封装、芯片堆叠、高精度组装);(6)测试技术(裸片测试、封装测试、系统测试)。

本文设计了一款基于FPGA裸芯片和FLASH裸芯片的小型化高密度系统级3D封装电路。该封装电路将FPGA裸芯片、FLASH裸芯片、电源电路、去耦电路、配置电路等FPGA最小系统电路在一个小型化陶瓷电路中实现,通过BGA(球栅阵列)扇出,同时实现了高集成度和高可靠性。

1 系统三维架构

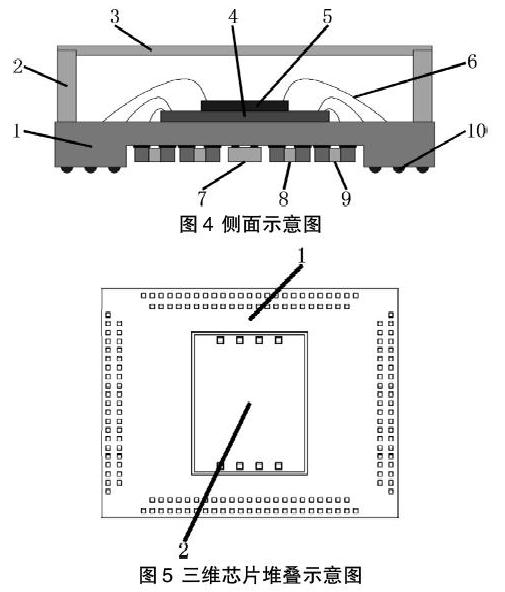

本3D封装电路由10部分组成。其中,包括LTCC基板电路1、可伐框2、可伐盖板3、FPGA裸芯片4、FLASH裸芯片5、引线键合6、电源电路7、配置电路8、去耦电路9和BGA10,如图1~图4所示。

本3D封装电路架构上主要采用了三维芯片堆叠、无源集成和球栅阵列:

1.1 三维芯片堆叠

因为FPGA裸芯片和FLASH裸芯片都是硅芯片,属于同质芯片,金属化体系相同,所以可以堆叠[3]。FPGA裸芯片1和FLASH裸芯片2通过金字塔式堆叠在LTCC基板电路上的TOP层,如图5所示。

1.2 无源集成

基于电路小型化的考虑,本3D封装电路在LTCC基板电路的背面设计了一个无源集成腔1,用于将电源电路2、去耦电路3、配置电路4埋置到无源集成腔内的SMT层电路,如图6所示。这样的设计有2个显著优点:

(1)充分利用三维空间,实现电路小型化和高集成度;(2)根据去耦电路的机理,去耦电容离芯片电源PAD路径越短越好。传统的去耦电路都是去耦电容排列在FPGA封装器件的四周或者背面,路径较长,去耦效果不够理想;本设计极大地改善了去耦效果;(3)由于本设计集成了电源电路、去耦电路和配置电路,外部PCB只需要单电源供电,无需再设计电源电路、去耦电路和配置电路,极大地简化了PCB设计。

1.3 球栅阵列

LTCC基板电路通过高密度多层布线,将FPGA的I/O、VCC、GND和JTAG功能PAD重新排布,合理分布在BOT层电路的四周,通过BGA焊球形式扇出,如图7所示,包括球栅阵列PAD1、球焊料2。

2 系统电路设计

2.1 电路总体设计

本系统电路以FPGA处理器和FLASH存储器为核心构建FPGA最小系统电路。FPGA外围电路包括电源电路、去耦电路、配置电路等,在一个LTCC基板电路上实现。系统电路原理图如图8所示。

LTCC基板电路共有十层电路结构,分别为TOP层、SIG1层、GND1层、VCC层、SIG2层、SIG3层、GND2层、SMT层、GND3层和BOT层。电路实物照片如图9所示。各层电路功能如下:

(1)TOP层实现FPGA裸芯片和FLASH裸芯片的三维芯片堆叠以及芯片各功能PAD和基板电路的互联;(2)SMT层实现电源电路、去耦电路和配置电路;(3)SIG1、SIG2、SIG3层实现高密度信号布线;(4)VCC层实现电源平面;(5)GND1、GND2、GND3层实现地平面;(6)BOT层实现BGA球栅阵列扇出;(7)GND3和BOT层陶瓷中间开腔,SMT层的电路埋置在腔中。

2.2 电路优点

传统的FPGA器件,所有功能PAD都做扇出,PAD数量众多、排布复杂,器件体积大,PCB Layout设计难度大;本文设计的封装电路不仅实现了传统FPGA器件的所有功能,还把FPGA最小系统电路全部集成在金属陶瓷封装中,减少了PAD数量,大大缩小了电路体积,在实现高集成度的同时实现了高可靠性,显著降低了PCB Layout的设计难度。

LTCC基板电路通过十层高密度陶瓷电路对FPGA各功能PAD重新布局和布线,其中FPGA管理功能PAD在内部实现互联,只需要将基本的I/O、VCC、GND和JTAG功能PAD通过BGA扇出,大大减少了PAD数量,布局更加简洁合理。

原来设计FPGA系統电路的PCB时,至少需要8层Layout,设计难度大,加工周期长;现在设计PCB时,只需要连接VCC、GND,将JTAG和I/O扇出连线即可,仅仅需要4层甚至更少的Layout即可,极大地简化了PCB设计,缩短了加工周期,具有很强的实用性。

3 工艺实现方案

本文设计的封装电路,巧妙利用芯片堆叠、引线键合、LTCC技术、SMT工艺和BGA植球的优势,实现多种功能:

(1)通过金字塔式芯片堆叠工艺,将FPGA裸芯片和FLASH裸芯片组装到TOP层;(2)通过引线键合工艺,实现FPGA裸芯片和FLASH裸芯片各功能PAD和基板电路的互联。FPGA裸芯片和FLASH裸芯片通过内中外三层引线键合,将FPGA裸芯片和FLASH裸芯片上的3层PAD键合到LTCC基板TOP层电路对应的内中外三层键合PAD上,实现了高密度信号互联,如图10所示;(3)通过LTCC高密度多层电路工艺[4],实现FPGA和FLASH的信号互联、电源、去耦、配置电路布线,将FPGA的I/O、VCC、GND和JTAG功能PAD重新排布,合理分布在BOT层电路的四周;在LTCC陶瓷基座上焊接可伐边框,通过平行封焊工艺封盖,实现封装电路的高气密性;(4)通过SMT工艺,将电源电路、去耦电路和配置电路组装到SMT层,埋置在GND3和BOT层的腔内;(5)通过BGA植球工艺,将BOT层的I/O、VCC、GND和JTAG焊盘通过球栅阵列扇出。

4 结语

本文设计的封装电路通过十层高密度陶瓷电路布线、金字塔式芯片堆叠和陶瓷开腔工艺埋置电路,大大缩小了电路体积,实现了电路小型化;陶瓷基座上焊接可伐边框,通过平行封焊工艺封盖,实现封装电路的高气密性。该封装电路具有集成度高、体积小、可靠性高等优点。

本设计的目的在于提供一种小型化高密度FPGA系统级3D封装电路,满足对FPGA小型化、可靠性有较高要求的应用场景。本设计的电路大大缩小了电路体积,实现了电路小型化;同时具有良好的气密性、高可靠性,PCB Layout设计简单,具有较强的实用性。

参考文献

[1] 代明清,韩强,邓豹,段小虎,等.基于ARM和FPGA的SiP系统级封装设计[J].微型机与应用,2014,33(1):25-28.

[2] 冉彤,白国强,等.基于系统级封装SIP的信息安全芯片集成设计[J].微电子学与计算机,2012,29(1):10-14.

[3] 王喆垚.三维集成技术[M].北京:清华大学出版社,2014.

[4] 高岭,赵东亮.系统级封装用陶瓷基板材料研究进展和发展趋势[J].真空电子技术,2016(05):11-14.