一种PCIe接口逻辑的FPGA实现

秦固平,毛瑞娟,杨小勇,常振杰

(1.中国人民解放军66138部队,北京 100043; 2.国家无线电频谱管理研究所有限公司,陕西 西安710061)

0 引言

随着现代通信技术的发展,在无线电监测领域,大带宽、高性能和高效率特性已经成为无线电监测设备中高速数据传输总线的基本要求。PCIe作为第三代互连技术已经广泛应用于无线电通信领域[1-3]。PCIe总线采用差分链路作为数据传输通道,由于差分信号可以使用更高的总线频率,使得PCIe总线的数据传输带宽较其他总线有很大的提高[4-6]。

本文针对无线电监测设备对高速数据传输总线的需求,采用基于FPGA的信号采集处理板卡作为端点设备,以工控板作为根复合体,完成了二者之间PCIe总线的接口设计。其中,FPGA采用Xilinx Kintex 7系列xc7k410tffg900芯片,工控板配置为Windows7 64位操作系统,i5处理器。按PCIe传输的流程分模块设计了PCIe总线的接口逻辑,并在FPGA中实现64位数据接口的DMA模式写数据传输,实现了数据的高速传输。这种以模块式的设计方法实现PCIe接口的DMA传输模式可以在无线电监测设备等嵌入式设备中得到应用。

1 PCIe总线总体设计

1. 1 PCIe IP核接口设计

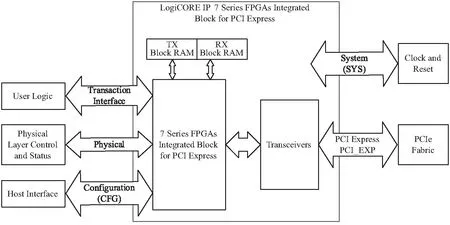

Xilinx 7系列FPGA的PCIe IP核是一种大带宽、可扩展和可靠性强的串行结构模块[7-10]。PCIe IP核遵循PCIe基本规范,内部集成了物理层、数据链路层和事务层,并且已经完成了物理层和数据链路层的相关逻辑功能,预留出了相应的逻辑接口供用户使用[11-13]。IP核中的事务层采用数据包的形式在设备之间交换信息,用户只需要对事务层进行操作,即可完成PCIe设备之间的数据交互[14]。PCIe IP核的顶层功能块和数据接口如图1所示。

图1 PCIe IP核的顶层功能块和数据接口

事务层作为PCIe总线协议的顶层,首先要完成的是对事务层数据包进行组装和拆解,Xilinx FPGA PCIe IP核分为2种事务层接口:64位事务层接口和128位事务层接口[15-17]。设计中PCIe总线接口选择64位事务层接口类型。

典型的64位事务层接口32位可寻址存储器写请求TLP格式严格遵循PCIe总线协议规范,PCIe总线上每个时钟周期传输64位数据。其中Byte0表示第一个时钟周期的低32位数据,Byte4表示第一个时钟周期的高32位数据,Byte8表示第2个时钟周期的低32位数据,Byte12表示第2个时钟周期的高32位数据,依次类推。

1. 2 PCIe DMA写逻辑框架设计

在PCIe体系结构中,根复合体和存储器在同一层架构上,所以DMA模式在数据传输过程中,无需经过CPU主机内存与外设内存之间可以直接进行数据交换,并且可以一次传输多包数据,使得设备具有大的数据吞吐量,适用于大带宽数据传输[18-20]。由于数字接收机中传输的数据量大,传输带宽大,所以必须采用DMA模式的存储器写事务进行。而传统的DMA模式每传输一包数据都需要进行一次DMA启动过程,这样会影响数据传输带宽,所以在此采用链式DMA模式,链式DMA模式下每启动一次DMA,可以传输多包数据。该过程需要配合MSI(Message Signaled Interrupt)中断才能有效执行,MSI中断即消息中断,属于PCIe总线的消息事务。对于每次中断传输的数据包数以及每一包数据的大小需要PCIe驱动端与逻辑端协商而定。

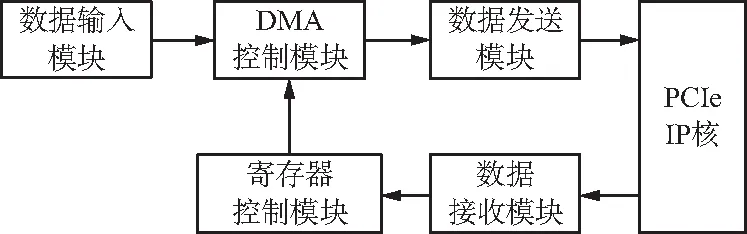

无线电接收机PCIe DMA控制结构分为6个模块,分别是PCIe IP核、数据接收模块、寄存器控制模块、DMA控制模块、数据发送模块以及数据输入模块。各模块的逻辑关系如图2所示。

图2 PCIe DMA控制结构

数据输入模块主要用来存储前端数据。在FPGA板卡中,接收机接收到无线信号首先要进行模拟信号到数字信号的转换,也就是A/D转换,然后把转换后的数据储存在数据输入模块中,当上位机发送传输启动信号之后,再进行DMA传输。数据输入模块在本设计中用FIFO来实现,不再对此模块做详细论述。

数据接收模块是用来接收用户对数字接收机的配置信息及DMA传输机制的相关参数,并根据PCIe字节规范协议进行解包,提出有用信息传给寄存器控制模块进行存储。

寄存器控制模块主要用来存储数据接收模块解析出的基地址信息、传输包长度信息、传输包大小信息及无线电监测设备的相关参数信息等,并对数据接收模块解析后的信息进行重新组包,对数据写入地址进行控制。寄存器地址及存储的内容由FPGA部分和驱动部分协议决定。

DMA写控制模块主要完成DMA写数据传输过程中数据包长度的控制和相应的DMA写偏移地址的控制。写控制模块是整个传输过程的核心,需要在地址匹配和时序方面特别注意,否则就会在调试过程中出现计算机死机或蓝屏。具体实现过程将在各模块的FPGA具体实现中做详细论述。

数据发送模块根据DMA写控制模块发送的包头信息和地址信息对每一包数据按PCIe协议规范进行组包,然后将组好的数据包发送至PCIe核,经过PCIe核传输至计算机进行存储。

2 PCIe接口各模块的FPGA实现

2. 1 数据接收模块

数据接收模块用来接收用户对无线电监测设备的配置信息及DMA传输机制的相关参数。用户在上位机上通过驱动程序设置无线电监测设备的参数,PCIe驱动同时发送DMA传输机制的相关配置参数,从而保证PCIe硬件逻辑与上位机驱动匹配。数据接收模块信号框图如图3所示。

数据接收模块在接收设备配置信息数据之前,需要与PCIe驱动程序配合,先接收驱动发送的复位信号对硬件进行复位,然后接收到前端发送的数据信息rx_data,根据PCIe字节命令规范对接收的数据包解包。常用的TLP包类型有存储器写请求0x40,存储器读请求0x00,带数据的完成报文0x4A,不带数据的完成报文0x0A。这里对数据接收模块接收到的数据解包,高8 bits为包头0x40时,表明接收到存储器写请求,就会生成PCIE存储器写信号pcie_reg_wr。根据协议解析包数据中的信息有基地址信息、传输包长度信息、传输包大小的设置信息等。信息还可以包括用户根据需求在上位机端输入的无线电监测设备的信号参数信息,例如信号带宽、频率和通道选择等信息。最终数据接收模块把从上位机接收到的相关参数信息rx_data和存储器写信号pcie_reg_wr发送至存储器控制模块中。

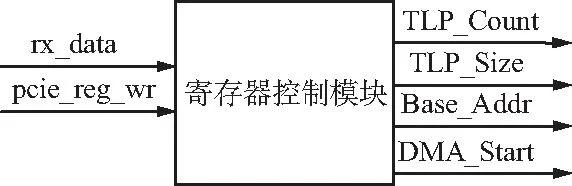

2. 2 寄存器控制模块

寄存器控制模块主要用来存储数据接收模块解析出的基地址信息、传输包长度信息、传输包大小信息及无线电监测设备的相关参数信息等。在DMA模式下的数据传输过程中,FPGA板卡通过PCIe驱动接收来自PC端发送的传输数据包的大小信息以及PC端分配的地址信息。寄存器控制模块对数据接收模块解析后的信息进行重新组包,并对数据写入地址进行控制。

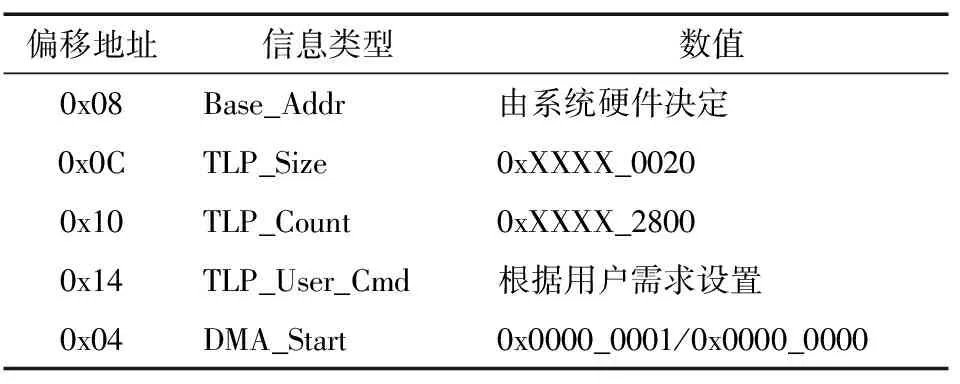

设计中涉及到的数据信息类型所对应的偏移地址及数值如表1所示。其中偏移地址由PCIe的FPGA控制部分与PCIe驱动部分的共同协商确定。

表1 寄存器控制分配表

偏移地址0x08中存储的信息类型为Base_Addr,表示系统分配的基地址信息,基地址的值由所使用的计算机系统硬件分配,在寄存器存储模块中把基地址信息存储到偏移地址0x08中。该偏移地址发送至DMA控制模块用于控制DMA数据传输的地址。

偏移地址0x0C中存储的信息类型为TLP_Size,表示DMA传输中每一个TLP包的数据大小,单位为Byte,它的值由所使用的计算机系统硬件决定,通常为128 Btyes和256 Bytes。设计中使用的计算机系统是Windows7 64位操作系统,TLP_Size被限定在0xXXXX_0020,低13位是有效位,即128 Bytes。

偏移地址0x10中存储的信息类型为TLP_Count,表示每一次DMA中断传输的TLP数据包数,该包数设置太大则调试会出现死机的情况,若设置太小,则会增加传输相同数量的数据产生中断的次数,根据反复测试和验证该参数最终设置为0xXXXX_2800,低16位为有效位,即10 240包数据,这个值能够使PCIe接口的传输性能达到较优的水平。

偏移地址0x14中存储的信息类型为TLP_User_Cmd,表示预留给用户自定义的信息数据。例如可以通过上位机设置用户所需要的无线电信号信息,包括信号带宽、频率和通道选择信息等。

偏移地址0x04中存储的信息类型为DMA_Start,表示DMA启动和停止信号,其中最低位是有效位,其值为0x0000_0001时启动DMA操作,启动DMA写传输后,FPGA板卡根据以上配置信息通过PCIe接口向PC传输相关数据。

寄存器控制模块信号框图如图4所示。在寄存器控制模块中,如果检测到存储器写信号pcie_reg_wr有效,并且接收到的数据为1,对应的地址偏移地址是0x01,这就意味着DMA写数据启动信号dma_en有效,并发送给DMA数据传输请求模块DMA_REQ。在DMA_REQ模块中,如果检测到dma_en有效,随即产生DMA写使能信号dma_wr_enable,并发送至DMA写数据控制模块DMA_WRITE模块。DMA_WRTTE模块中如果检测到dma_wr_enable信号有效,则在本模块中产生传输数据请求信号tpl_send_req,使得状态机跳转到SEND_TPL发送数据状态,到此状态后,生成DMA写请求信号dma_write_req,并发送至TX模块。在TX模块中,如果状态机处于初始状态,并且接收到了DMA写请求信号,就产生DMA写请求反馈信号dma_write_ack,再次发送给DMA_WRITE模块。

图4 寄存器控制模块信号框图

2. 3 DMA控制模块

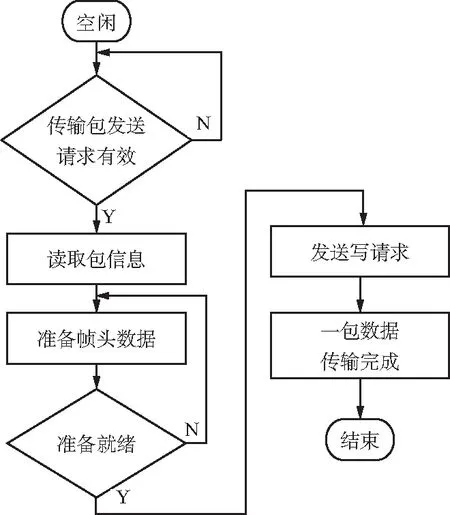

DMA写控制模块完成DMA写数据传输过程中数据包长度的控制和相应的DMA写偏移地址的控制。DMA写控制模块控制过程的流程图如图5所示。在空闲状态等待数据传输包请求信号,如果传输包发送请求有效信号,发出数据传输包发送请求信号,读取包信息。在该状态中,根据系统反馈的传输包可携带的最大数据长度信息TLP_Size,确定每一包数据携带的数据长度。目前,测试系统中每一包数据可携带的最大数据长度为32 DW。在PCIe协议中数据长度以DW为单位计数,每个DW等于4 Bytes。

图5 DMA写控制模块控制流程

读取包信息完毕后准备帧头数据,在该状态中对每一包数据的传输个数进行计数,一包数据为128 Bytes,每个数据为8 Bytes,即一包数据有16个64 bits数。根据寄存器控制模块中存储的基地址Base_Addr对传输数据对应的DMA写偏移地址进行控制。传输过程中每传输一包数据,在基地址基础上增加一包数据对应的偏移地址大小,DMA写偏移地址的增量等于实际传输的一包的数据的大小。目前的测试系统中,偏移地址每次递增0x80(128 Bytes)。

当每包数据都准备好后向数据发送模块发送DMA写请求信号dma_write_req,在数据发送模块处于初始状态,并且接收到了DMA写请求信号dma_write_req,就产生DMA写请求反馈信号dma_write_ack,再次发送给DMA写控制模块,如果在DMA写控制模块中接收到了DMA写请求反馈信号dma_write_ack,就会产生释放数据信号buf_rd_en给数据输入模块。在数据输入模块接收到buf_rd_en有效之后,就会输出待传输的数据buf_rd_data,发送给DMA写控制模块。DMA写控制模块把得到的数据dma_wr_data发送给数据发送模块。如果数据发送模块中状态机跳转到发送数据状态,就把dma_wr_data发送给数据发送接口trn_td,最后经过PCIe核传输给PC。每发送完成一包数据,则跳转至空闲状态等待下一次发送请求。

2. 4 数据发送模块

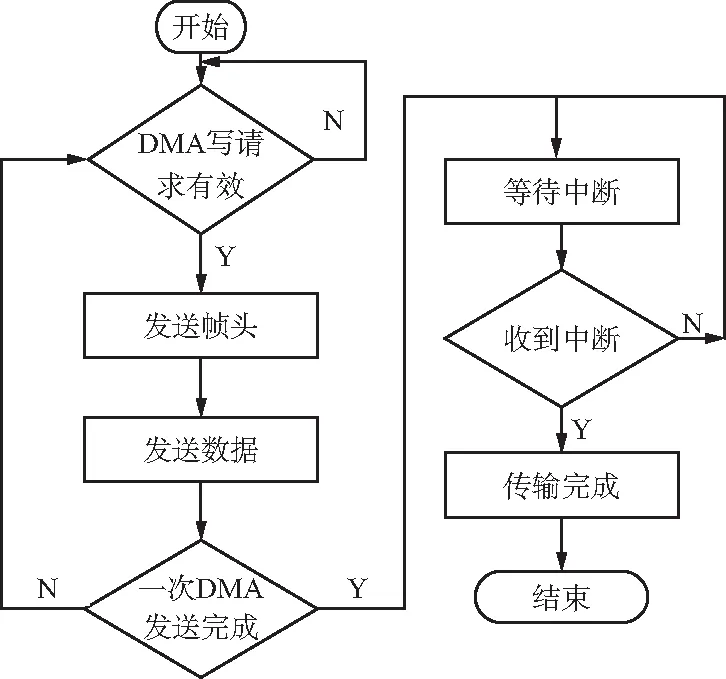

数据发送模块首先根据DMA写控制模块发送的包头信息和地址信息对每一包数据进行组包,然后将组好的数据包发送至PCIe核,经过PCIe核传输至计算机进行存储。为了避免数据传输过程中出现的丢包现象,在此采用状态机的方式根据PCIe协议的数据包格式将数据分状态发出。此外,为了解决因传输数据量过大而出现的计算机死机问题,在此采用MSI中断的方式进行处理。MSI中断机制是PCIe协议规范中的内部中断机制,当数据发送模块发起MSI中断时,停止数据传输,等待来自PC端的中断反馈信号[5,8]。如果数据发送模块收到了中断反馈信号,继续进行数据传输。这样就可以保证在PC机正常工作的情况下数据可以持续高速传输。数据发送模块工作流程如图6所示。

图6 数据发送模块工作流程

在数据传输过程中,需要对数据流量进行实时控制,主机系统会实时向FPGA反馈当前剩余的内存容量,只有内存充足时才能进行高速传输。在开始状态如果检测到当前的内存充足,并且接收到了DMA写请求信号,则将组好的数据帧头信息发送出去,第2个时钟周期传输第2个数据,其中包含数据和地址信息,第3个周期传输数据。

传输包数据的大小由TLP_Size决定,TLP_Size存储在寄存器控制模块的reg中。目前测试系统中TLP_Size为0x0000_0020,即128 Bytes,而每个数据大小是8 Bytes,所以每一个TLP包携带了16个数据。发送16个数据需要16个时钟周期,第16个数据发送完成时一包数据发送结束。在寄存器控制模块reg中存储了驱动设置的每次中断传输的数据包数TLP_Count,目前测试系统中TLP_Count为0x0000_2800,即10 240包数据,一次中断发送的包数未达到TLP_Count时状态机跳转至IDLE状态,继续发送数据包,当发送包数达到TLP_Count时,标志一次DMA发送完成,状态机跳转至中断响应状态MSI_trig。在MSI_trig状态FPGA向计算机端发送中断信号,等待系统的响应。如果收到了计算机端的中断反馈信号,则将发送至PCIe总线上的数据传输到计算机上,完成一次DMA数据传输。一次DMA数据传输结束后继续进行下一次DMA数据传输过程,直到上位机发起DMA停止指令结束DMA传输。

3 实验结果与测试

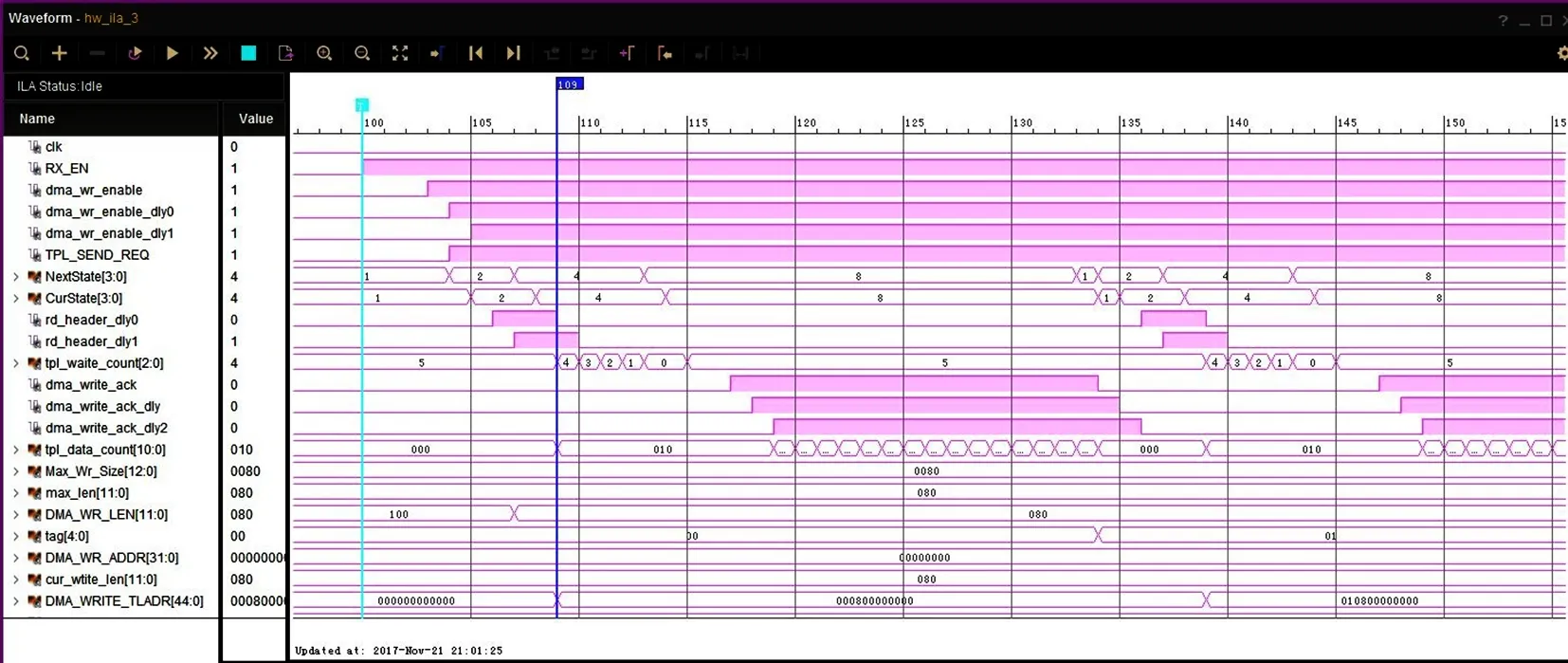

根据以上设计分析,在赛灵思FPGA开发平台Vivado2017. 1上实现了各个模块的逻辑程序编写。采用某型号数字接收机中的FPGA数字处理板卡和工控板作为硬件平台,其中FPGA型号为xc7k410tffg900芯片,工控板配置为Windows7 64位操作系统,i5处理器,128 G固态硬盘。PCIe总线为PCIe1. 0版本,数据链路×8通道,考虑物理层编码损耗,×8链路的理论传输速率16 Gbps。测试过程中采用Vivado开发软件提供的Debug IP核对各模块的主要信号波形进行捕捉。DMA写控制模块中的信号波形如图7所示。

DMA写控制模块波形中adc_buf_data信号为发送的数据信号,由波形图可以看出发送一包有效数据所占用的时间为30个时钟周期,每个时钟周期4 ns,每一包数据大小128 Bytes,由此可以估算出传输带宽为8. 5 Gbps。

图7 DMA写控制模块调试波形

4 结束语

文章采用Xilinx FPGA实现了PCIe高速总线上的数据传输,完成了DMA写控制各个模块的逻辑程序及调试。测试结果表明:在i5处理器、Windows7 64位操作系统、PCIe1. 0版本和数据链路为×8条件下DMA写数据传输带宽达到8. 5 Gbps。该设计已在具体项目中使用,且均能保证稳定可靠的传输速率。如果采用更高配置的操作系统,更高的PCIe协议版本,数据的传输存储速率会得到进一步提高。PCIe总线技术在未来的无线电监测领域中将会有更加广泛的应用。