基于Avalon总线的音频频谱分析系统设计与实现

姚梦茹,胡永兵,李 慧

(安徽大学 计算智能与信号处理教育部重点实验室,安徽 合肥 230601)

0 引 言

伴随电子与通信技术的发展,数字音频[1]广播、多媒体通信等这些数字音频处理技术在人们的生活中产生了深远影响,并且在社会中得到了广泛应用。所谓数字音频技术[2]是指把模拟声音信号通过采样、量化和编码过程转换成数字信号,然后再进行记录、传输以及其他加工处理;在重放时再将这些记录的数字音频信号还原为模拟信号,获得连续的声音。数字音频技术的应用领域包括消费电子类数字音响设备、乐器调音、广播节目制作系统、多媒体应用、广播电视数字化等。其中调音器的应用比较广泛。市面上的乐器声音识别调音器虽然小巧便携,但是实时性和准确性却不高,而且现有的调音器的种类比较少,比较常见的是吉他调音器。

为了提高识别准确率,使识别设备小型化,基于FPGA[3]中的Avalon总线[4]技术和快速傅里叶变换算法[5-6],设计实现了一种实时高效的音频频谱分析系统,实时完成各种音乐信号的采集与分析,克服传统调音器的限制。

1 系统总体方案

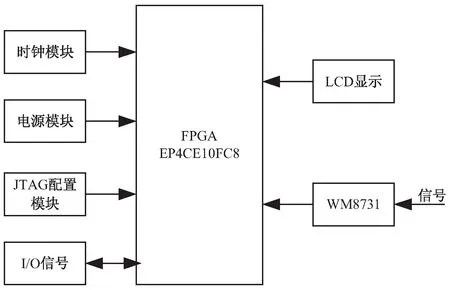

音频频谱显示系统是基于Nios II系统[7]实现的。整个系统硬件框图如图1所示,包括ADC模块、LCD模块、RAM模块、Nios II系统模块。其中Nios II是核心,与各外围电路形成完整的主控系统。

音频频谱显示系统的结构框图以及系统总体方案示意如图1所示。

图1 系统总体方案示意

2 系统硬件设计

整个系统硬件框图如图2所示。其中信号采集与信号转换模块主要由芯片WM8731实现,主要是对输入的音频信号进行A/D转换,输出数字信号到FPGA主芯片,以便对其进行快速傅里叶变换。时钟模块为系统各个模块的功能实现提供稳定的时钟信号。电源模块为系统的正常运行提供稳定的电源输入。JTAG配置模块为系统的代码测试提供帮助。LCD模块就是显示音乐信号经过处理后的音频频谱,能有直观清晰的频谱感受。

图2 系统硬件设计框图

系统使用的FPGA芯片是Cyclone IV E。Altera公司的新型Cyclone IV系列[8]FPGA设备在低成本和低功率FPGA市场上已经整合了Cyclone系列。Cyclone IV具有高容量性能,能够很好地应用于程序设计,使系统开发者在降低成本的同时,又能满足逐渐变大的带宽需求。FPGA外围电路设计主要包括:配置下载电路、时钟电路、A/D转换电路。文中设计采用了JTAG下载配置[9]方式。时钟模块使用的芯片是PCF8563,该模块结合PLL的IP核将板卡自带的50 MHz单端有源晶振倍频或分频成多个不同时钟,给各个模块使用。其中WM8731的I2C配置模块使用50 MHz时钟;WM8731的I2S转换模块使用18.38 MHz时钟;FFT计算IP使用18.38 MHz时钟;TFT_LCD显示软件则使用40 MHz时钟。A/D转换模块使用的是WM8731音频编解码芯片。WM8731带有麦克风输入,音频输入和音频输出端口,音频采样率从8 kHz到96 kHz可设置。该芯片使用I2S接口传输音频,使用I2C接口接受FPGA的控制。

3 FPGA程序设计

FPGA程序设计是系统的核心,该设计中使用Verilog HDL[10]语言采用自上而下的设计方法,顶层模块包含四个功能模块,分别是音频采集与编解码模块、FIFO缓存模块、FFT数据处理模块、TFT_LCD频谱显示模块。各功能模块在Altera公司的Quartus II 13.0软件下采用Verilog HDL语言设计完成,并在Modelsim软件下编写Testbentch进行仿真测试。

3.1 音频采集与编解码

该模块为通过两线制的时序写WM8731的寄存器,在该系统中,数据访问采用16位分辨率和I2S模式。在I2S模式下,ADC输出数据的时序如图3所示。有效数据在adclrc发生电平变化后的第二个bclk电平发生变化的位置。adclrc是校准时钟,用来表明是使用左声道数据还是右声道数据。当adclrc变成低电平时,输出的是左声道数据,反之,当adclrc为高电平时说明输出的是右声道数据。位时钟是bclk,在它的下降沿时会输出一个新数据,最先输出的是最高有效位。

图3 I2S模式下ADC/DAC数据时序

3.2 FFT数据处理模块

该系统使用了两种加窗算法[11-12],分别是矩形窗和汉宁窗。由于采样的时候,每次至少采样128个点,然后对12个点进行FFT处理,这相当于加入了矩形窗;汉宁窗的作用是能有效压低旁瓣。在程序中,对于采集过来的时域信号分别进行加窗,程序如下所示:

void win hanning(long int win[])

{

int i;

for(i=0;i<512;i++)

{

win[i]=(long int)win[i]*hcos[i]);

}

}

其中,hcos[]是加窗的系数数组,在初始化已经进行计算,程序如下:

for(i=0;i<512;i++)

{

hcos[i]=0.5-0.5*cos(0.012 271 85*i);

}

3.3 LCD显示模块

LCD控制器[13]是非常重要的外围片上设备,通过LCD控制器来完成处理器对显示驱动器的控制,最终完成LCD屏的点亮操作。因为LCD显示驱动器仅仅是一个被动系统,所以还需要有一个控制电路来提供驱动系统所需要的扫描时序信号以及显示数据。通过对LCD控制器进行操作,处理器完成对LCD显示设置扫描时序和写入显示数据,从而实现对LCD的显示。

4 NIOS II系统的搭建

该课题的核心是在FPGA芯片上设计一个基于Nios II的音频频谱分析系统,利用Qsys[14-15]将处理器、存储器以及其他外设模块连接起来构成一个完整的系统。在该系统中,使用了已有的外设IP核模块,也构造了自己的IP核模块。该系统由Nios II处理器、onchip_memory、jtag_uart、fifo、fft等模块组成,如图4所示。

使用MegaWizard插件管理器来创建和修改含有定制IP核的设计文件,并且在设计文件中例化IP核。可以利用MegaWizard插件管理器来创建、定制与例化IP核、参数化模型库(LPM)模块,并且可以在Quartus II软件、EDA设计的入口和综合工具中使用IP核。该系统配置了PLL、FIFO、RAM、FFT的IP核,从而搭建出了Nios II系统。

5 系统测试

针对系统中的核心模块——音频编解码模块进行测试。当把系统程序下载到电路板上之后,用Quartus II软件自带的SignalTap逻辑分析仪对WM8731的数据接口模块进行逻辑分析,抓捕信号,结果如图5所示。观察波形可知,当16位的输入数据信号DATA_In开始传输16位的数据时,输出数据信号DATA_In随即也开始输出16位的数据,可知该模块能完成信号的转化,并能正常输出数据信号。

图4 Nios II系统的搭建

图5 WM8731模块的时序

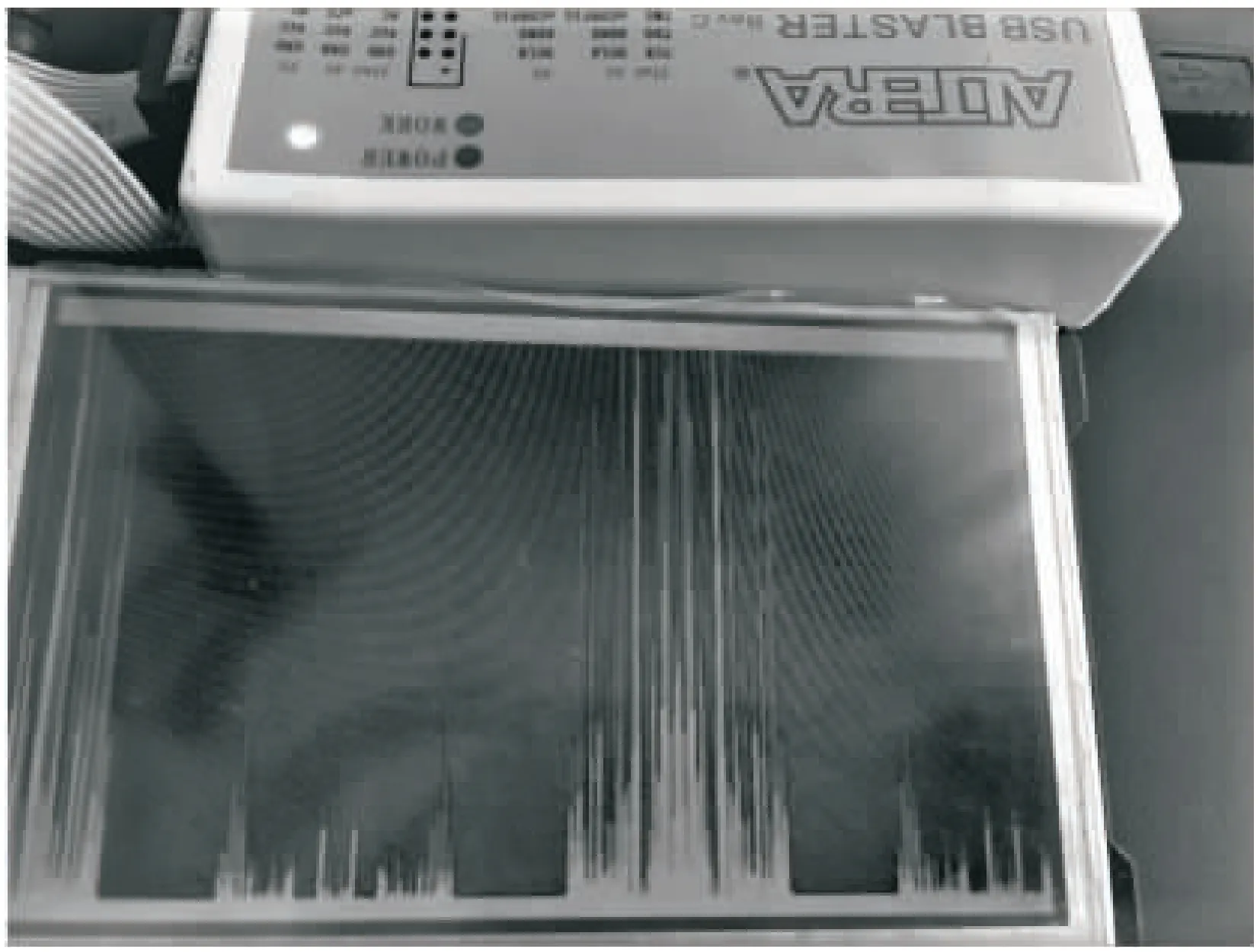

实物显示频谱图如图6所示。可以看到输入不同的音乐信号,频谱图显示有明显不同,达到了预期效果。

图6 实物显示

由图6可以看出,输入的音乐信号的音调发生变化,屏幕上显示的音频频谱随之实时变化,达到了预设效果。

6 结束语

基于FPGA中的Avalon总线技术和快速傅里叶变换算法,设计实现了一种实时高效的音频频谱分析系统。该系统可以实时完成各种音乐信号的识别与分析,克服了传统的调音器的限制,可以对多种乐器进行调音,大大提高了乐器的音准并克服了一种调音器只能调节一种乐器的限制,提高了调音器的使用率,具有实际应用价值。系统测试运行工作稳定,实现了预期设计的功能。