一种可容软错误的稳定性检测器

汪海

摘要:随着现代技术的大力发展,集成电路的可靠性日益严重。负偏置温度不稳定性引起的电路老化,高能粒子轰击组合逻辑电路产生软错误,是影响可靠性的两个重要因数。基于上述两個问题,设计了一种稳定性检测器,该稳定性检测器用于老化预测传感器中,用来检测集成电路老化情况。并且结构自身可以容软错误。

关键词:集成电路; 负偏置温度不稳定性; 老化预测; 软错误

中图分类号:TN407 文献标识码:A 文章编号:1009-3044(2019)02-0266-02

A Stability Checker With Soft Error Tolerance

WANG Hai

(School of Electrical and Information Engineering, Anhui University of Science and Technology, Huainan 232000, China)

Abstract: With the rapid development of modern technology, the reliability of integrated circuits is becoming more and more serious. The circuit aging caused by negative bias temperature instability and soft errors caused by high energy particle bombardment are two important factors affecting reliability. Based on the above two issues, a stability check is designed, the stability check used in aging prediction sensors, used to detect integrated circuit aging. And the structure can resist soft errors.

Key words: Integrated circuit; Negative bias temperature instability; Aging prediction; Soft error

1 引言

老化和软错误是影响电路可靠性的两个重要因数。研究表明产生老化的主要原因为负偏置温度不稳定性[1-4](NBTI:Negative Bias Temperature Instability)。由于NBTI本身的特性,我们可以通过老化预测传感器对NBTI引起的老化进行提前预测[5]。软错误是一种由辐射、电压电流变化等引起的一种瞬态过程[6-7]。单粒子瞬态SET(Single Event Transition)是软错误的一种[8-10],SET通常在组合逻辑电路产生,当电路中发生了SET,那么SET就会通过组合逻辑电路,依次影响各个结构的工作状态,导致错误发生。

2 稳定性检测器

2.1 老化预测传感器框架结构

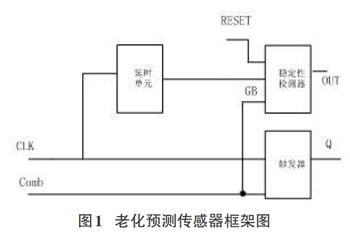

老化预测传感器框架图如图1所示,时钟信号CLK通过延迟单元输出保护带信号GB,组合逻辑输入信号Comb和保护带信号GB通过稳定检测器,得到稳定检测器输出信号OUT,判断是否发生了老化。

本文的结构用于传感器的检测阶段,其用来检测组合逻辑输入信号,并判断电路是否发生老化。

2.2 容软错误的稳定性检测器设计

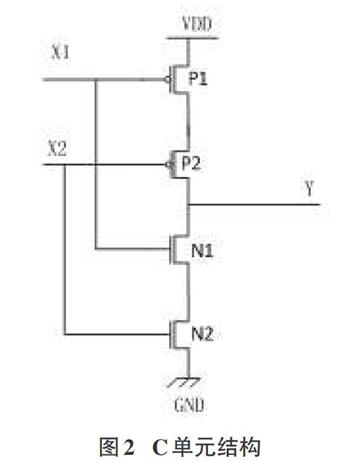

本文提出了一种可容软错误的稳定检测器。该结构利用了C单元对结构进行防护。因此下文介绍C单元结构,C单元结构图如图2所示,其工作原理为X1、X2输入相同,那么反向输出Y,X1、X2输入不同,那么保持之前的输出,输出为高阻态。

C单元工作过程:当X1、X2输出为高电平1,那么P1、P2关断,N1、N2管导通,Y输出0。当X1、X2输出为0时,那么P1、P2导通,N1、N2关断,Y输出1。若此时X1点输出由0变为1,N1导通,P1关断,P2导通,N1关断,Y节点既不接高电平,又不接地,输出为高阻态,保持之前的输出1。因此C单元可以用来稳定电路。

容软错误的稳定性检测器如图3所示, RESET为该结构的复位开关,用来控制结构的正常工作(正常工作时RESET控制P1为关断状态)。GB为延时单元输出的保护带信号,Co和CoB为组合逻辑输入信号以及其反向信号。OUT为检测结果,并用来控制P2、N4、N5、N6,当组合逻辑电路未发生老化,OUT输出为0,此时P2导通,N4、N5、N6 关断,稳定性检测器可以持续对组合逻辑输入进行检测。当检测到组合逻辑电路老化时,OUT输出为1,P2关断,此时结构的上拉网络关断,N4、N5、N6导通,下拉网络导通,OUT输出为1,从而锁存检测结果。

当检测完成后稳定性检测器发生软错误,假设X点受到高能粒子轰击,发生软错误,由于X,Y节点逻辑输出值在未发生错误时为0,当X点发生软错误并由0跳变到1,此时Y点仍然为0,故X,Y逻辑值相反,通过C单元输出高阻态,OUT输出为1。由于未改变结构OUT输出值,此时N4、N5、N6导通,下拉网络导通,纠正X点值,使得结构进入恢复为稳定状态。

3 结论

本文提出了一种可容软错误的稳定性检测器,该检测器可以预防锁存期间结构因高能粒子轰击而产生的锁存错误,并且通过反馈使节点保持强0状态,提高了稳定性检测器的抗干扰能力。

参考文献:

[1] Ding D, Zhang Y, Wang P, et al. Design a delay amplified digital aging sensor circuit in 65nm CMOS[C]// IEEE International Conference on Solid-State and Integrated Circuit Technology[J]. IEEE, 2017:1449-1451.

[2] 徐輝, 李丹青, 应健锋, 等. 基于关键路径与改进遗传算法的最佳占空比求解[J]. 传感器与微系统, 2017, 36(10):124-128.

[3] Khan S, Hamdioui S. Modeling and mitigating NBTI in nanoscale circuits[C]// On-Line Testing Symposium. IEEE, 2011:1-6.

[4] 徐辉, 何洋, 李丹青, 等. 考虑路径相关性的TG-based缓解电路老化[J]. 电子测量与仪器学报, 2018(4).

[5] Agarwal M, Paul B C, Zhang M, et al. Circuit Failure Prediction and Its Application to Transistor Aging[C]// IEEE Vlsi Test Symmposium. IEEE Computer Society, 2007.

[6] Mehrara M , Attariyan M , Shyam S , et al. Low-cost protection for SER upsets and silicon defects[C]// Design, Automation & Test in Europe Conference & Exhibition. IEEE, 2007.

[7] Xu H , Zhu J , Lu X , et al. An advanced SEU tolerant latch based on error detection[J]. Journal of Semiconductors, 2018(5).

[8] Ahlbin J R . Characterization of the mechanisms affecting single-event transients in sub-100 nm technologies[C]// Vanderbilt University, 2013.

[9] Baumann R . Soft Errors in Advanced Computer Systems[J]. IEEE Design & Test of Computers, 2005, 22(3):258-266.

[10] Atkinson N M , Ahlbin J R , Witulski A F , et al. Effect of Transistor Density and Charge Sharing on Single-Event Transients in 90-nm Bulk CMOS[J]. IEEE Transactions on Nuclear Science, 2011, 58(6):2578-2584.