I2C总线技术在舰船能量管理系统I/O端口扩展中的应用

许智豪,李维波,华逸飞,徐聪,范磊

武汉理工大学自动化学院,湖北武汉430070

0 引 言

舰船能量管理系统适用于发电自动化、系统监测报警、输配电监控保护以及用电设备的监控管理,是综合电力舰船的核心控制部分之一。在能量管理系统中,底层控制器的数量很多,并且需要采集、发送大量的I/O指令信号和状态信号。如果将底层控制器的各个部件、外围设备、I/O端口都分别采用独立的线路与微处理器直接连接,那么连线将会错综复杂,甚至难以实现。所以,有必要采用总线技术并借助I/O端口扩展处理芯片,从而最大限度地集成化处理数量庞大的数字量信号。

目前,I2C(Inter Integrated Circuit,I2C)总线主要应用于各类传感器、模数转换器、存储芯片、实时时钟芯片等数据处理芯片中。相较于其他总线接口,其结构简单、扩展性强,故可广泛应用于各种数据采集系统,例如云服务器中的智能家居控制系统[1],以及在移动智能终端领域中利用I2C总线集中处理智能终端的多种传感器[2]。

I2C总线具备良好的可移植性,可以利用软件模拟I2C时序,并摆脱了处理器中I2C控制器的引脚范围限制。但同时,I2C也增加了软件处理的过程,降低了处理器效率,存在可靠性不高的缺点,可能会在数据传输过程中丢失或改变数据。为了提高I2C信号传输的可靠性,本文将增加I2C驱动芯片和专用隔离芯片,以保证其波形的稳定性。将介绍通过I2C总线采集控制大容量数据的方法,即CPU仅依靠串行数据线(Serial Data,SDA)和串行时钟线(Serial Clock,SCL)来实现与多个外围器件之间的全双工数据传输。I2C总线系统为串行接口,传输速率快且结构简单,一条I2C总线上可以连接多个具有I2C接口的设备。通过硬件外围电路即可确定各个器件的地址,再利用软件寻址即可方便地扩展多型设备。本文将基于单片机的普通I/O端口和软件编程来模拟I2C总线,从而实现高级精简指令集机器(Advanced RISC Machine,ARM)与 I2C接口器件之间的可靠通信[3-4]。

1 能量管理系统的硬件架构

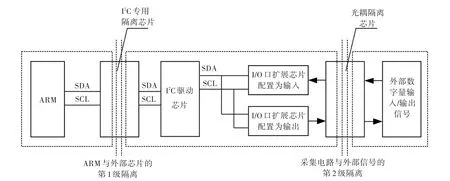

为了保证舰船能量管理系统的正常运行,需要采集多路数字量来获取当前电站的运行状态,并根据读入的数字量和集控台下达的指令来输出相应的数字量信号,用以控制各底层设备。图1所示为基于ARM控制器的能量管理系统的硬件架构,其主要由顶层集控台、数字量信号处理模块及底层各个电站的开关量信号组成。首先,由具备光耦隔离功能的数字量采集模块获取各个舰船电站的出口断路器状态信号、反馈量信号和配电板输入指令信号等;然后,通过I2C总线将所有的数字量输入电平信号传输至信号处理控制器,随即进行信号处理;最后,通过CAN总线和以太网与集控台进行数据交互。同时,当集控台发出指令操作数字量控制器时,信号处理控制器可以根据所采集的信号来控制参考电压,从而选择接触器、电源出口断路器分合闸、配电板指示灯等被控对象并完成相应的逻辑互锁等判断工作,用以避免底层器件的误操作情况。

图1 基于ARM控制器的能量管理系统的硬件架构Fig.1 Hardware architecture of the energy manage system based on ARM controller

2 数字量信号处理硬件的拓扑结构

信号处理的硬件部分主要由CPU最小系统、I2C专用隔离芯片、I2C驱动芯片、基于I2C总线的I/O端口扩展芯片及光耦隔离芯片组成,基本结构如图2所示。首先,ARM输出的信号通过I2C专用隔离芯片构成第1级隔离,以保证ARM读取数据的抗干扰能力;然后,通过I2C驱动芯片使隔离后的I2C信号能够对多路I/O端口扩展芯片进行操作;最后,经由光耦隔离芯片构成的第2级隔离,I/O端口扩展芯片接收或控制外部数字量信号,用以防止外部干扰影响系统内部的处理电路。

其中,I/O端口扩展芯片可以配置为输入模式或输出模式。当CPU将其配置为输入模式时,芯片将读取外扩的8路输入信号的电平状态并将其转换为I2C信号,在时钟信号的配合下,可将数据信号经由驱动芯片和隔离芯片传输至CPU;当CPU将其配置为输出模式时,芯片将读取经由隔离芯片和驱动芯片放大的I2C数据,并在时钟信号的配合下由扩展芯片转换为电平信号,用以驱动光耦隔离芯片输出数字量[5-6]。

图2 数字量信号处理硬件的拓扑结构Fig.2 Topology of the digital signal processing hardware

2.1 I/O端口扩展芯片

本文将选用TI公司的PCA9554/54A系列芯片,该芯片可以提供8位通用并行输入/输出端口(General Purpose Input Output,GPIO)的扩展功能,其内部结构如图3所示,主要由I2C总线控制器、移位寄存器、中断控制器等模块组成。通过I2C总线控制器与移位寄存器的配合,PCA9554/54A可将其读取的I2C数据转换为8路输出信号,或在读取8路输入状态后通过I2C总线将数据传输至控制器处理。其中,上电复位模块可将所有寄存器设置为默认值并将器件状态初始化。

图3 PCA9554芯片的内部结构示意图Fig.3 Schematic diagram of internal structure of PCA9554 chip

PCA9554/54A设置了 3个管脚(A0,A1,A2)来确定芯片的地址,最多可允许8个器件共用一条I2C总线。PCA9554与PCA9554A的唯一区别在于固定I2C的地址不同,理论上最多可以允许16个器件(9554和9554A各8个)连接到同一条I2C总线上。

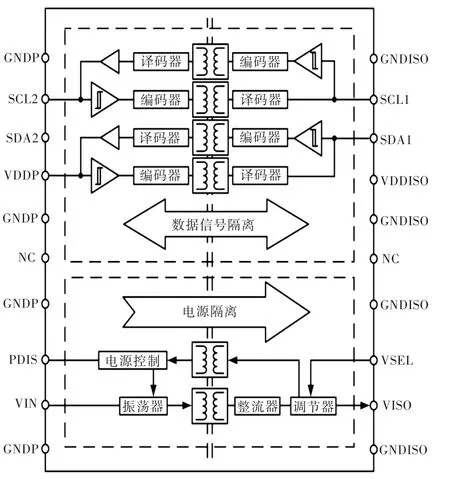

2.2 I2C专用隔离芯片

本文将选用ADI公司的ADM3260产品作为I2C隔离芯片,其内部结构如图4所示。该芯片集成了数据信号隔离模块和电源隔离模块,可以有效减小外部的共模干扰信号。芯片可以在高达1 MHz的通信频率下处理双向I2C通道信号,从而满足本文对数字信号控制的响应速度要求。

图4 隔离芯片的内部结构示意图Fig.4 Schematic diagram of internal structure of isolated chip

2.3 I2C驱动芯片

本文将选用TI公司的PCA9517芯片作为I2C信号的驱动芯片,其内部结构如图5所示。由图5可知,该驱动芯片采用了开漏机制,故器件本身只能输出低电平而无法主动输出高电平,除非通过外部上拉电阻将信号拉至高电平,因此必须在I2C总线上设置上拉电阻。由于PCA9517芯片引脚的最大灌电流为6 mA,故对于5 V的上拉电平而言,上拉电阻不宜低于1 kΩ,以免损坏芯片端口或导致输出低电平的幅值增加。

图5 I2C驱动芯片的内部结构示意图Fig.5 Schematic diagram of internal structure of I2C drive chip

3 I2C总线扩展I/O端口的实现方法

3.1 I2C总线的原理

I2C总线由一条SDA和一条SCL组成,从设备将在SCL时钟信号的控制下读取主设备传输的数据信号。当时钟信号为高时,读取数据线的电平信号;时钟信号为低时,允许改变数据线的电平信号。根据选用的从设备通信协议,可以对从设备进行寻址和数据传输。

启动I2C总线后,主机即可对从设备进行寻址操作。I2C从设备的地址为1个字节,即需要8个时间周期来完成寻址操作,若某个从设备的地址对应主机发送的地址,该从设备便在下一个时钟周期反馈一个应答信号,之后即可读取从设备的数据信息或对该从设备进行写操作。分析了I2C的读取时序之后,即可利用普通I/O端口模拟I2C时序[7-9]。

当SCL为高时,SDA由高到低的跳变定义为启动信号;当SCL为低时,SDA由低到高的跳变定义为停止信号。

发送设备每发送1个字节,就在下一个时钟周期内开始读取应答信号状态,由此来判断接收设备是否正确收到了该字节。当应答信号为低电平时,表示接收设备已成功接收该字节,即为有效应答信号(Acknowledgment,ACK);当应答信号为高电平时,一般表示接收设备未成功接收该字节,即为非应答信号(Negative Acknowledgment,NACK)。

由于需要在时钟信号为高时读取数据,所以当从设备为发送设备、主设备为接收设备时,ACK波形应在时钟信号为高时保持为低。如果主设备为发送设备,则当其收到1个字节后即发送1个NACK信号,用以通知被控发送器结束数据发送,并产生一个停止信号,由此结束I2C总线的本轮操作。

在I2C总线上传送的每一位数据都有一个时钟脉冲与之对应(或同步控制),即在SCL串行时钟的配合下,在SDA上逐位串行传送每一位数据。

3.2 I/O端口扩展的方法

图6所示为I2C总线启、停信号的软件模拟方法。首先,根据I2C总线的启动信号和停止信号波形将时钟信号保持为高电平,延时4 μs后,将数据信号电平由高设置为低;然后,发出启动信号,再将时钟信号设置为低电平,准备发送或接收数据;最后,在发送停止时将时钟信号保持为高电平,延时4 μs后,将数据信号电平由低设置为高。

图6 I2C总线启、停信号的软件实现方法Fig.6 Software implementation method of I2C bus start and stop signal

发送启动信号后,将由控制器发送芯片的地址。芯片地址实际上由硬件电路决定,地址长度为1个字节,其中前7位为地址,第8位为数据方向位,这个方向位也决定了下一个操作是接收还是发送。当主机收到该数据的应答后,将写入1个字节的控制指令,0x00表示PCA9554之后的输入端口寄存器,0x01表示输出端口寄存器,0x03则表示输入/输出模式配置。若0x03设置为输入模式,则依次读取扩展的8路输入信号;若0x03设置为输出模式,则发送1个字节以控制扩展的8路输出信号。I/O端口扩展芯片PCA9554的写数据和读数据的时序如图7所示,其中n为端口数据量。

图7 I/O端口扩展芯片PCA9554的写数据和读数据时序图Fig.7 Timing diagram of writing data and reading data for I/O port extension chip PCA9554

4 工程应用示例

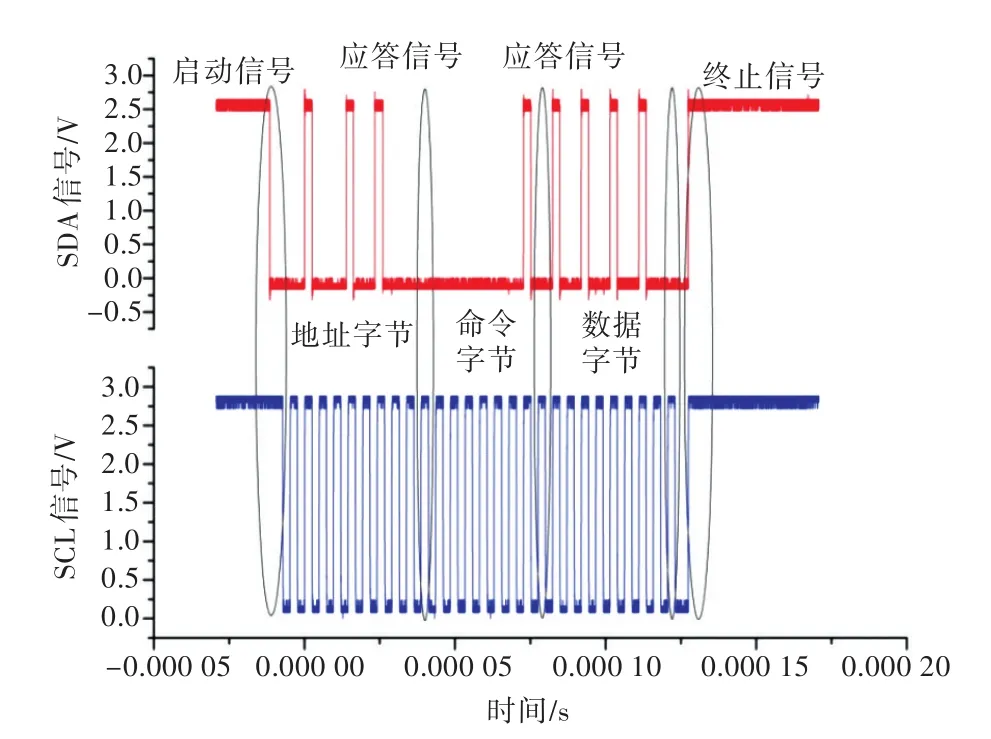

本数字量处理模块的主要应用目标为控制舰船能量管理系统的各个电站开关量,为了验证工程应用效果,本文设计了一块含有64路拨码开关(数字量输入)与64路LED发光二极管(数字量输出)的工装板。当拨通某一路输入开关时,相应的LED灯便会发光,以验证数字量采集、处理、输出整个环节的可靠性。通过I2C总线向PCA9554写入字节的波形如图8所示。

在CPU发出启动信号后的8个周期内,SDA将发出1个字节的地址信号0x4A,对应于输出板的第5块芯片。收到应答信号后,即可认为CPU与该芯片通信正常。

在本轮操作之后的8个周期内,SDA将发出1个字节的控制命令0x01,即将该芯片配置为输出模式。收到应答信号后,CPU将控制该芯片输出设定的数据字节0xAA,而工装板上的输出状态也为0xAA。

图8 通过I2C总线向PCA9554写入字节的波形图Fig.8 The waveform of bytes is written to PCA9554 via the I2C bus

由图8可知,模拟I2C总线时序可以有效控制I/O端口扩展芯片,从而实现I/O端口的扩展工作。

目前,本文提出的舰船能量管理系统的数字量处理模块已完成电磁干扰试验和环境试验,并已进行实船安装且运行状态良好。

若从设备存在问题,则将会出现如图9所示的情况[5]。即接受1个字节数据后,从设备向CPU发出1帧非应答信号,随后CPU将直接发送停止信号,并不再对该芯片进行操作。

图9 非应答信号的处理波形Fig.9 The processing waveform of negative acknowledgment

5 结 语

本文采用软件编程模拟I2C总线的方法,利用2个GPIO端口实现了对I2C总线接口器件的访问,扩大了串行扩展总线I2C器件的应用范围。通过采用PCA9554/54A芯片,可以最多扩展128个I/O端口,有效节约了芯片的引脚资源,简化了系统结构,并使得多个数字量的采集与控制工作不再受单片机自身I/O端口不足的限制。通过专用芯片ADM3260,可以将I2C信号进行隔离,并适当增加I2C信号的电平延时时间,从而大为提高系统的可靠性。该系统易于移植到其他单片机系统上,在工业控制领域具备一定的推广与参考价值。

然而,采用软件模拟I2C波形时,虽然精简了硬件资源,但也占用了较多的CPU资源,故其数据处理时间比直接引脚访问增加了100倍以上。因此,在设计系统时需要统筹考虑,应在满足时序需求的情况下尽量减少硬件资源的占用。