从7nm到3nm,从SoC到SoIC 台积电生产工艺展望

半导体工艺是集成电路发展的核心技术之一,近日,在日本举行的2019年VLSI研讨会和之前召开的SEMOCONWeSt 2019两大研讨会上,台积电公布了大量有关自家7nm后的生产工艺,以及最新的SOIC堆叠封装技术发展的相关资料,国外媒体WikiChip FUSE也對此进行了详细介绍。本刊特别对这篇文章进行了专业的翻译,以让读者了解未来数年半导体工业的发展趋势,那么我们什么时候能用上5nm,甚至3nm工艺的处理器?未来除了闪存芯片,其他芯片也会走上垂直堆叠的道路吗?

台积电是全球最大的半导体代工企业,其工艺制程的发展对全球未来数年半导体产业和集成电路发展都有着重要的影响。一直以来,台积电都在先进工艺和技术上不断投入巨资,大力加强研发,随着时间推移,台积电也逐渐占据了先进制程的领先地位,2018年更是推出了全新的7nm以及更先进的工艺。那么,台积电在2019年乃至以后的工艺和技术演进应该如何发展呢?根据台积电在业内研讨会上公布的一些资料,台积电不但布局了7nm、5nm的技术和工艺,还在未来的3nm以及更先进制程上做出了一定的研究。

7nm时代:多种工艺齐上阵

台积电目前最先进的工艺节点被称作N7,也就是商业化宣传中的7nm节点。台积电认为N7是目前最先进的逻辑工艺。对台积电的技术路线图而言,7nm节点是16nm节点之后一个重要的全新节点,它的进步是全方位的。之前的10nm节点属于一个半代节点,甚至主要用于为7nm节点研发技术。横向对比来看,台积电的7nm节点在很大程度上可以和英特尔的10nm节点,以及三星的7nm节点相媲美。和台积电自己的16nm技术相比的话,7nm节点的工艺大约在相同功耗下提升了35%-40%的速度或者在相同性能下带来了只有原工艺65%的功耗表现。

台积电7nm工艺概述

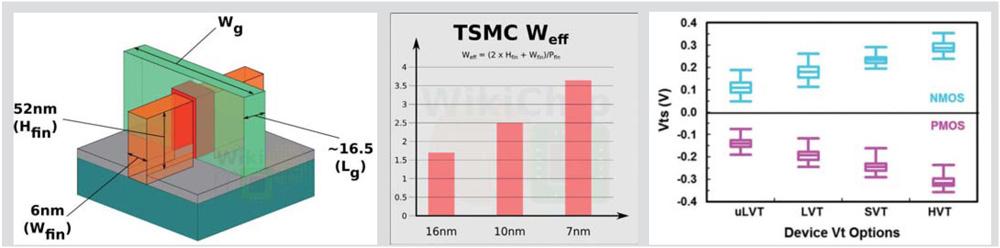

台积电的7nm工艺节点拥有大量的新技术,包括第四代FinFET,第五代高K金属门、3.3倍的路由门电路密度,金属钴的使用以及关键层采用的SADP技术。此外,采用后栅极和双栅极氧化工艺也是7nm工艺节点的特征。

在制程方面,台积电7nm工艺继续使用了深紫外DUv 193nm ArF沉浸式光刻技术。实际上,这项技术在7nm制造的应用中已经带来了一些局限,并影响了制造过程,同时也带来了一些独特的设计规格。根据台积电的数据,7nm工艺下栅极间距已经缩小至57nm,互联间距则固定在40nm以便在SADP点处保持较高的光刻投影图形品质。

此外,台积电的7nm工艺在晶体管轮廓方面也进行了增强。和英特尔一样,台积电在沟槽的触点上引入了新的金属钻进行填充,取代了之前的钨金属。钻是一种比较脆和硬的金属,稳定性也比较出色。在这里使用钴可以降低50%的电阻,从而降低无谓的能量消耗。

在具体的工艺实现上,新的7nm工艺通过调整鳍片间距和高度之间的比例,使得晶体管体积变小,自然使得最终芯片面积变得更小,并更节约成本。当然,继续缩小鳍片宽度可能会带来更窄的通道,这需要同时提高鳍片高度以保持门接触面的实际有效宽度,同时也能够改善短沟道特性和亚阈值斜率(即Ieff/Ceff),并降低整体电容寄生效应。总体而言CV/I类型的器件延迟依旧更为出色,因为诸如Cgate和Cov这样的固有电容依旧和Ieff成比例存在。

台积电在7nm工艺上采用的另外一种缩放方案是调整了有效宽度,这个数值被称为Weff。从图中可以看到,7nm工艺节点的有效宽度Weff值为3.5,远高于16nm的1.7左右。此外7nm工艺还带来了一些多电压特征值的器件,其Vt范围为200mV。

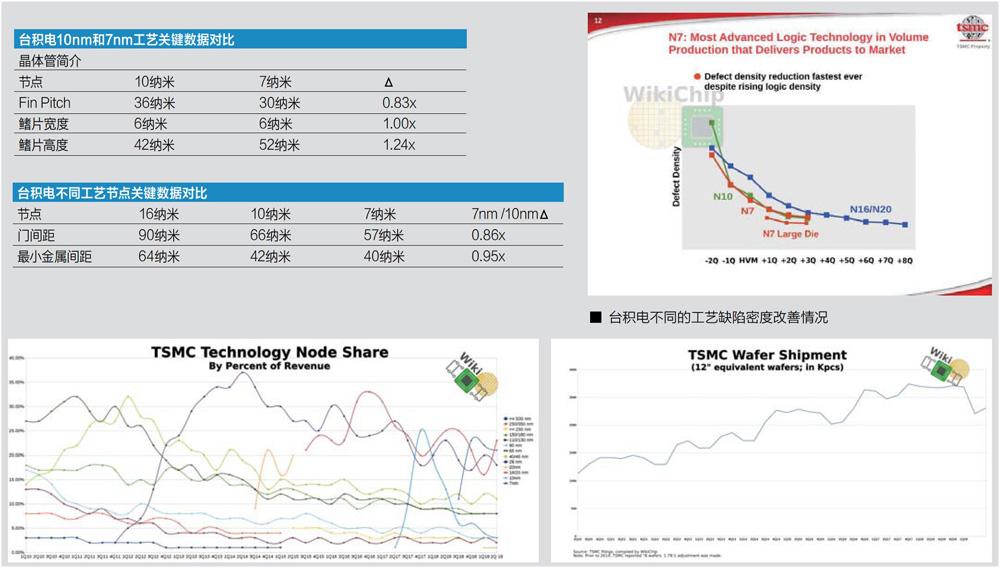

台积电还提到了旗下7nm工艺的一个重要特性,那就是它的缺陷密度改善情况。一般来说,工艺在使用早期,由于技术熟练程度、应用规律掌握情况甚至材料配比等问题,总会在最终完成的晶圆上出现这样那样的缺陷,用于衡量缺陷出现频率的参数,被称为缺陷密度。缺陷密度是影响最终半导体产品良率的最直接原因之一。高缺陷密度肯定会导致低良率,从而带来较高的生产成本。因此,降低缺陷密度提高良率是半导体在不断发展和演进中非常重要的课题。

根据台积电的数据,以N16/N20也就是16nm和20nm的相关工艺为例,缺陷密度在早期较高,在大规模量产时(HVM),也处于中高水平,但是已经有明显下降。之后随着量产时间不断延长,台积电不断改进制造的各个方面,经过多个季度的调整后,缺陷密度随之下降至可接受水平并保持在低水平状态。另外,台积电的数据还显示,10nm工艺在大规模量产时间节点之前的第二个季度,其缺陷密度甚至可能高达80%以上,基本无法提供满意的良率,但是这个数据随后大幅度降低并在大规模量产时降低至35%左右。

台积电感到尤为满意的则是7nm工艺的缺陷密度数据。7nm工艺在移动客户的较小芯片上使用时,大规模量产期间的缺陷密度甚至低于10nm工艺的同期数据,并最终改善至和10nm、16nm同期工艺相当甚至更低的数值,同时数值还在进一步降低。对HPC客户而言,当芯片尺寸大于250平方毫米时,这种被称为“大核心”的产品使用7nm工艺时缺陷密度表现甚至更为出色,已经远低于16nm工艺在同时期的水平,令人惊讶。

最后台积电还介绍了相关财务情况。由于7nm工艺昂贵的成本,因此台积电的财务数据显示,7nm工艺的需求在过去半年中略有下降,下降幅度大约为1%,台积电绝大部分收入依旧来自成熟的16nm节点。不过,今年第二季度的晶圆出货量略有增长,可能会带动7nm等工艺进一步提升产量,台积电认为7nm将会在全年带来25%的收入。

增强版7nm工艺:N7P工艺

台积电在7nm工艺上不断地推出新的产品。在台积电的描述中,上文所介绍的目前已经投入生产的7nm工艺被称为N7,台积电接下来将推出一种新的N7P工艺,全称是N7Performance-enhanced,也就是N7性能增强版工艺。N7P工艺还有其他的一些名称,比如第二代7nm工艺,或者“7nm year 2”。但是,N7P和N7+工艺是完全不同的两种工艺,最好不要将其混淆。

根据台积电的说明,N7P工艺本质上是N7工艺的加强版,依旧采用DUV深紫外沉浸式光刻技术,其IP和N7完全兼容,并使用完全相同的设计规则。不过N7P引入了FEOL和MOL优化,能够在相同功率下提高7%的性能,或者在相同的性能下带来10%的功耗优势。所谓FEOL,是指Front-End ofLine生产前道工序优化,MOL是指生产中间工序优化,其中前者和器件性能有关,后者和互联等性能有关。通过这些工艺上的细微优化,新的N7P能够带来更好的表现。

引入EUV:N7+工艺

EUV极紫外光刻是目前先进半导体制造工艺的重中之重。不过受制于EUV在产能和良率方面的困扰,在目前EUV难以在芯片光刻的整个过程中使用。台积电在7nm上也规划了使用EUV技术的版本,那就是N7+。

N7+工艺的特点在于,在八个关键层上,台积电使用了EUV光刻,而其他普通层则依旧使用DUV光刻完成,这有助于降低成本和提高效能。台积电宣称,N7+工艺已经在今年第二季度进入了量产阶段,目前产量和N7工艺相当。和N7工艺相比,一些数据显示N7+工艺的密度达到了前者的1.2倍,并且在相同功率下能够提供高出10%的性能,或者在同等性能下能够降低15%的功耗。雖然纸面数据显示N7+的效能要略好于N7P,但是考虑到N7+采用了EUV后需要重做芯片的整个物理实施部分,包括全新的EUV掩膜等,那么N7+的性价比可能需要进一步衡量。

改进EUV:N6工艺

N6工艺是全新的工艺名称,其技术架构和N7完全兼容,不过商品名可能会改成6nm以方便宣传并展示差异。从技术角度来看,N6工艺相当于全面采用EUV技术的N7工艺,它计划比N7+工艺多使用一个EUV层。在设计规则方面,N6和N7是完全兼容的,这将吸引大量的客户迁移至N6工艺。

N6工艺的发布时间要比更先进的全代工艺N5(后文有介绍)甚至更晚一些,因此引入了很多N7+和N5工艺的经验,比如比N7更快的EDA参考流程、填充算法等。N7设计人员还可以直接使用N6的标准单元库来重新流片,并且加入了新的PODE聚扩散边以及CNOD连续扩散等技术,带来最多18%的晶体管密度改善。N6工艺还引入了一个独特的MO路由,这个新的MO路由可以用作局部互联,用于连接多Fin器件的源极或者漏极节点,并且在单元内连通部分通用的nFET和pFET节点。

N6工艺在2020年第一季度开始风险试产,并在2020年底之前开始大规模生产。台积电留下了比较充足的时间用于制程调校和良率提升。目前看来,从DUV迁移到EUV,N6工艺在竞争力和性能上应该是独具一格的。

5nm和3nm时代:靠近极限,突破极限

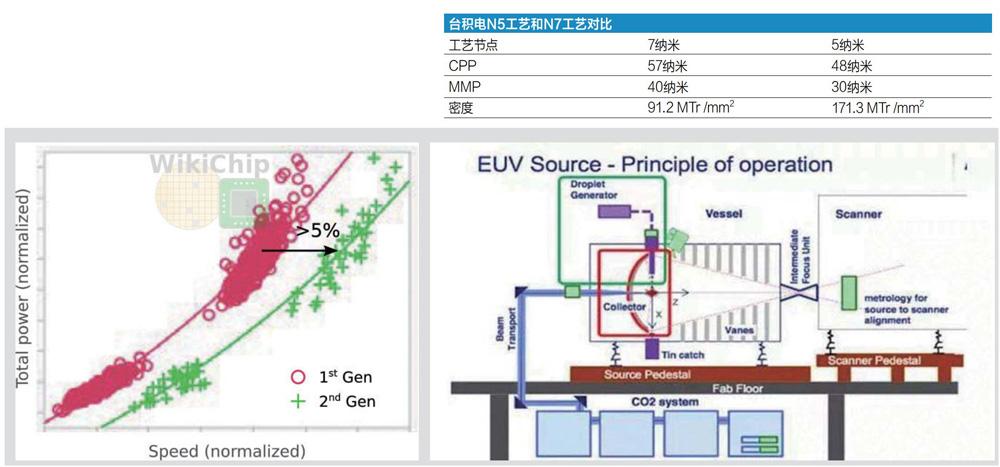

5nm节点是7nm节点之后的一个全代节点,台积电在5nm节点上动作很快,已经在2019年第一季度进入了风险试产,可能在2020年上半年将发布可以进入大规模量产阶段的工艺。台积电称这项新的工艺为N5,并且表示N5将在更多层上广泛使用EUV技术,产量上也能得到保证。

和N7工艺相比,台积电的N5工艺可以提供最高1.8倍的逻辑密度。性能方面,相比N7,N5可以在相同功率下提高15%的性能,或者在相同的性能下降低30%的功耗。和N7一样,N5工艺将有2个版本,分别面向移动处理器(N5)和高性能处理器(N5P)。面向高性能产品(HPC)的N5P工艺将提供额外的选项,和N7相比,高性能版本的N5工艺将提升最多25%的性能。和N5相比,高性能的N5P在同等功率下将提高7%的性能,或者同等性能下降低15%功耗。不过时间上N5P要晚一些,大约在N5之后一年才能提交客户进行生产,也就是2020年底或者2021年初。

另外一些资料显示,台积电在N5工艺上使用了新的两倍密度低K介电材料金属反应离子蚀刻,用于取代目前采用铜金属的类似工艺,实现金属间距小于30um,降低铜互连的电阻率。另外,台积电还带来了局部NIN电容改进,有助于解决由于较高的栅极密度而增加的电流等。

在N5之后,台积电还在积极研发3nm工艺。预计在2022年左右推出,代号N3。虽然之前包括英特尔、台积电、三星等厂商都在考虑使用诸如GAA等新的工艺形态解决更小尺度晶体管的性能和制造问题,但是也有一些证据表明目前的FinFET依旧存在潜力可挖。根据目前的情况来看,台积电在3nm阶段还是会使用FinFET,后续工艺才会考虑诸如GAA等新的制造方法。

在3nm之后,台积电暂时没有给出详细的规划。不过在新的Hotchips大会上,台积电展望了未来的工艺技术发展。在3nm乃至未来的技术发展中,包括碳纳米管(1.2nm尺度)、二维层状材料等都有助于使得晶体管更小、更快。此外,相变内存、旋转力矩转移、随机存取内存等技术可以和处理器一起封装,加快数据传递的速度等。台积电宣称在2050年,晶体管制造工艺将来到0.1nm级别,也就是氢原子尺度。

更高的集成度、更强的性能下一代封装技术

无论是制造工艺的发展,还是封装技术的发展,都源自对芯片级解决方案需求的不断增长。由于成本限制和良率等原因,目前的芯片级解决方案发展已经逐渐向着分化的方向迈进。目前产品的芯片制造需求往往有以下三个方面:首先是出于良率和分级的目的,一个大型的芯片解决方案将被分解为多个小芯片方案;其次,利用较老的工艺和模拟工艺来实现SoC的其他节点制造,以节约成本;第三则是通过HBM等组件完成更高的系统集成。

面对这样的市场和技术需求,台积电也提供了一系列解决方案。其中,晶圆级系统集成WLSI平台将面对移动SoC到高性能计算的所有产品。另一种“芯片-晶圆-基板”(CoWoS)技术则是面向人工智能、网络处理器以及高性能计算产品。第三种也就是集成扇出封装(InFo)将面向网络和移动应用、HPC等不同场合。

面向5G时代——InFo遍地开花

台积电的InFo封装是其通用扇出品圆级封装FOWLP的解决方案之一,根据不同场合还有不同的方案可供选择。InFo使用密集的重布线层RDL和Fine Pitch穿过晶圆上的过孔,并配合集成扇出衬底(InFo_OS)、内存封装衬底(FnFo_HS)以及InFo超高密度(InFo_UHD),实现对高性能移动设备、网络芯片以及高性能计算等不同应用的兼容和适配。对于5G移动平台,台积电也拿出了不同的方案,比如InFo POP用于移动计算处理器,使用InFo_AiP用于针对RF前端模块也就是FEM。针对基带调制解调器,台积电也准备了多堆栈方案也就是Nulti-stack(MUST)。

更高带宽的3D-MIM封装

虽然目前InFo封装以其针对性和便利性逐渐成为封装选择的主流,但是在一些场合InFo依旧存在问题。比如InFO_POP封装技术,最早是应用于苹果的A10处理器(之前的处理器采用的是传统的POP封装)。但是,受制于面积、引脚数量、通孔等问题,InFO_POP封装后,产品的内存带宽难以进一步提升。

在苹果A10时代,内存带宽问题可能沒有那么突出,但是在即将到来的5G和AI、边缘计算、移动计算时代,内存带宽成了根本需求,因为这些技术本质上就要求更高的内存带宽。为了解决这个问题,台积电宣布了InFo技术的更新版本也就是3D-MUST-in-MUST封装技术,简称为3D-MiM。3D-MiM和InFo存在一些技术上的共通之处,两者都是通过高密度的重布线层RDL和更小间距的Rne Pitch TIVs(InFoWLS),实现了多个垂直堆叠的存储芯片的集成。在这种封装中,I/O部分暴露在芯片的边缘侧,存储芯片通过层叠的方式连接至SoC,形成一个比较宽大的I/O区域,能够带来更大的传输带宽。

台积电给出了一些3D-MiM封装的案例。在这些例子中,一个长宽分别为15毫米、高度为5毫米的芯片内,集成了16颗存储芯片和对应的SoC,与传统采用倒装式封装的工艺相比,3D-MiM能够在高度一半的情况下带来2倍的存储带宽。此外,由于没有衬底、没有凸块,因此存储器从I/O到SoC的距离短了很多,从而带来了更好的电气性能并且能够提供更好的散热表现。

台积电还宣称3D-MiM并不仅仅适用于单个SoC,实际上台积电已经提及了多个SoC以及大量存储芯片的封装情况,比如具有2个SoC搭配32颗存储芯片的方案,这样可以创建具有更高带宽和更低功率的HPC处理器。作为当前的一些2.5D封装也就是HBM的替代技术,3D-MiM的一个重要优势是存储器芯片可以直接连接至SoC而不需要基本的逻辑芯片转接。

网络和HPC的新选择——CoWoS和InFo

台积电还提供了对网络和高性能应用的新封装方案,目前已经可以在存储器和基板上开始应用CoWos和InFo技术。台积电的CoWoS技术现在已经可以扩展至2个标线,线间距的行列分別都是0.4um。CoWoS实际上是一个非常成熟的技术,台积电在过去五年中已经提供了超过15个使用CoWoS技术的流片方案。目前CoWos被广泛使用在GPU上,另一个重要的应用是网络处理器。目前,CoWoS最大可以支持6个HBM2模块,提供高达1.5TB/s带宽。台积电宣称还可以提供更高带宽的方案以及超过三个掩膜版的更大芯片面积。

对网络应用处理器而言,台积电提供了InFo技术。这个技术的一些技术参数包括:多芯片封装时间距大约为2um,最小的I/O引脚距离为40um,最小铜触点间距为130um。这项技术已经在2018年第二季度开始正式应用。目前台积电正在努力实现2个以上的芯片封装以及最大1.5倍掩膜版尺寸的芯片面积。

终极方案——集成系统芯片方案SoIC

上文洋洋洒洒写了这么多的新技术,但综合来看,上述所有的内容实际上都是为SoIC服务的。

台积电宣称SoIC是“真正的”下一代3D封装技术。SoIC是一种片上芯片(CoW)堆叠的方法,允许将很多不同的类型、功能和形态的芯片封装甚至混合在一起——即使这些芯片在尺寸和工艺节点上存在很大差异。经过SoIC封装后,芯片在外观上和其他任何标准芯片没有任何不同,并目可以将SolC和任何现有技术比如InFo、CoWoS或者倒装封装等技术结合在一起。和上文介绍的InFo_UHD一样,SoIC也追求封装的高密度,目前其封装密度高达每平方毫米10000个接触点,台积电认为,随着SoIC+的推出,未来最终可以达到每平方毫米100万个接触点的密度,再度提高100倍密度。

写在最后

制造工艺和封装工艺的发展,在很大程度上主导了半导体产业发展的脉络。举例来说,AMD CEO苏姿丰就坦言,在处理器的性能提升方面,新工艺和封装技术带来的性能增长大约有40%,其余的60%才是架构设计,软硬件配合的原因。

今天,伴随着AI、边缘计算、5G等创新技术的兴起,人们对工艺和封装技术的发展愈加重视。台积电本次公布了大量未来工艺和封装技术的信息:3nm以及更先进制程、封装技术的到来,又将容纳更多的晶体管,输出更多的计算能量。不过,现有的半导体制造和整体架构设计经过多年的发展,已经像一个快被榨干汁的柠檬,人们还在尽量地加大压力,希望榨出最后几滴汁水。在未来的数年乃至数十年中,希望半导体技术能够有全新、革命性的突破,只有这样才能实现人们对计算和数据的无尽渴求,满足一个个计算的梦想。