CNN加速器中卷积计算单元的硬件设计

杨博文 杨海涛 高浩浩

摘要:卷积神经网络(CNN)所有子层中卷积层的计算是整个网络计算中最耗费计算资源的问题,本文提出了一种对卷积神经网络的卷积层并行化实现方案。首先对系统的整体处理结构进行分析,然后对计算核的结构进行详细讨论,最后将卷积层中卷积运算并行映射到阵列处理器上。实验结果表明,在250Mhz的工作频率下,该结构可使FPGA(Field Programmable Gate Array,FPGA)提高峰值运算速度。

关键词:卷积神经网络;现场可编程门阵列;卷积层

中图分类号:TP391.4 文献标识码:A 文章编号:1007-9416(2019)10-0136-02

CNN是著名的深度学习架构,从人工神经网络扩展而来,它已经大量用于不同应用,包括视频监控,移动机器人视觉,数据中心的图像搜索引擎等[1-2]。由于CNN的特殊计算模式,通用处理器实现CNN并不高效,所以很难满足性能需求[4]。于是,基于FPGA,GPU甚至ASIC的不同加速器被相继提出以提升CNN设计性能[5-6]。卷积神经网络加速器主要由卷积、池化、数据选择、输入输出缓存等单元组成,其中卷积模块根据多个一定的权重(即卷积核),对一个块的像素进行内积运算,它的输出就是提取的特征之一,但因为卷积核的大小一般小于输入图像的大小,因此卷积提取出的特征更多的关注的是局部信息[3]。卷积计算单元是计算核的主要模块,主要的功能是对输入数据进行特征提取,其内部包含多个卷积核,组成卷积核的每个元素都对应一个权重系数和一个偏差量。

1 卷积计算模块设计

卷积运算是两个卷积核大小的矩阵的内积运算,即相同位置的数字相乘再相加求和。通常情况下,靠近输入的卷积层,譬如第一层卷积层,会找出一些共性的特征,如手写数字识别中第一层一般是找出诸如“横线”、“竖线”、“斜线”等共同特征,称之为基本特征,经过池化操作后,在第二层卷积层,可以找出一些相对复杂的特征,如“横折”、“左半圆”、“右半圆”等特征,越往后,卷积核设定的数目越多,体现出的特征越细致。

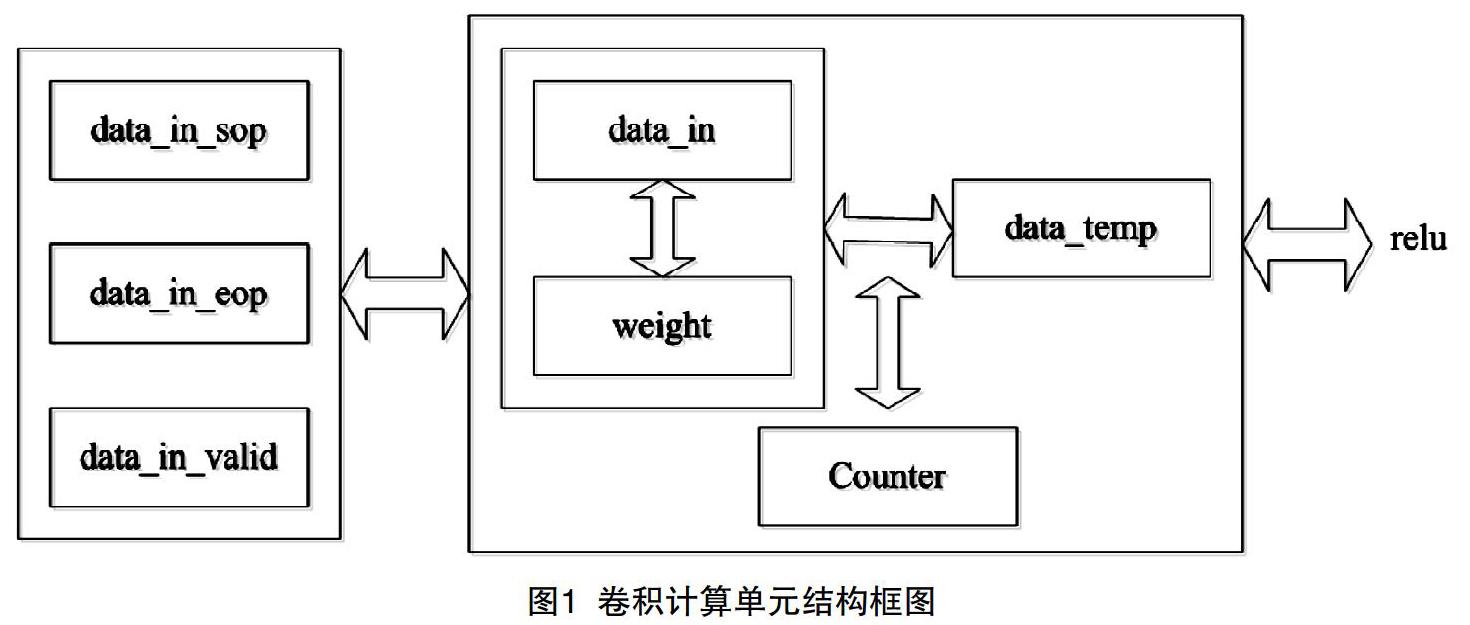

卷积计算单元的结构框图如图1所示,主要由数据输入信号data_in和权重输入信号weight_in进行卷积计算,当信号data_in_sop为1时,则判断信号data_in_valid为高,即输入数据有效,当data_in_eop信号为1时,则数据有效信号为低,读入数据结束。当复位信号为低时,输入原始数据的中间寄存器data_in_temp和weight_in_temp为0,当复位信号拉高时,中间寄存器data_in_temp和weight_in_temp分别等于输入的信号data_in和weight_in。因为网络中存在不同大小的卷积操作,通过全局控制器counter_control信号对网络的计算进行控制,当counter_control为0时,表示网络的第一层计算,则控制不同大小计算的寄存器max为121,支持网络中的11×11块大小的卷积运算;当counter_control大于1小于105时,表示网络的第二层计算,则控制不同大小计算的寄存器max为25,支持网络中的5×5块大小的卷积运算;当counter_control大于106小于419时,表示网络的第三、四、五层计算,则控制不同大小计算的寄存器max为9,支持网络中的3×3块大小的卷积运算。在计算卷积操作之前,定义寄存器counter用于计数,当data_in_valid为高,counter等于max时,则计数器归1,重新开始计数;当counter不等于max时,则计数器counter自加1,否则为0,依次循环。

执行卷积操作时,当计算器counter等于1时,中间结果信号data_temp等于输入原始数据和权重乘积;当计算器counter大于2小于max时,中间结果信号data_temp等于输入原始数据和权重乘积加前面的中间结果。当counter等于max时,执行ReLU操作,对得到的最终结果进行判断,当data_temp大于等于0,则输出信号data_out等于data_temp,否则置为0。其中,当data_in_valid为高且counter与max相等,则输出有效信号data_out_valid为1,否则为0;当data_in_valid为高且counter_sop与max相等,则输出开始信號为1,否则为0;数据输出结束信号data_out_eop比输入结束信号延两拍。

2 实验结果

在Zynq-7000 XC7Z045-2FFG900CFPGA上电路综合成功后生成的全局时序报告,工作频率为250Mhz。如表1所示芯片资源利用率情况,开发板上的资源足够充足,可以满足工程实现需要的资源,符合设计的要求。

参考文献

[1] 雷杰,高鑫,宋杰,etal.深度网络模型压缩综述[J].软件学报,2018,29(2):251-266.

[2] 王磊,赵英海,杨国顺,etal.面向嵌入式应用的深度神经网络模型压缩技术综述[J].北京交通大学学报:自然科学版,2017,41(06):34-41.

[3] 蹇强,张培勇,王雪洁.一种可配置的CNN协加速器的FPGA实现方法[J].电子学报,2019,47(7):1525-1531.

[4] 赵彤,乔庐峰,陈庆华.一种基于FPGA的CNN加速器设计[J].通信技术,2019(5):1242-1248.

[5] 赵博然.FPGA实现的可编程神经网络处理器[D].西安电子科技大学,2018.

[6] 周飞燕,金林鹏,董军.卷积神经网络研究综述[J].计算机学报,2017,40(6):1229-1251.