基于FPGA可变速率快速位同步的实现

,,

(1.东北电力大学,自动化工程学院,吉林 吉林 132012;2.海南热带海洋学院,电子通信 工程学院,海南 海口 570100;3.上海微小卫星工程中心,上海 200000)

1 引言

同步技术是数字通信中重要的环节,是通信系统的核心,也是最难的实现的地方,它决定着数据解调的成与败[1]。调制的信号经上变频后变成2.2~2.4G的射频信号[2]发射出去,在接收端接收该信号进行下变频,对其进行数据还原,只有当接收端产生相干载波的频率和相位与发送端保持一致[3-4],才能得到源数据。这就决定收发两端工作不在一起,为使接收端确定每一个码元的起止时刻,接收机的时钟应与输入信号的符号时钟同步[5],才能准确采样接收的信号。在早期的模拟解调调节器中,典型的同步方法是通过反馈环调整本地采样时钟的相位来实现[6],通常是每个符号周期提取一个采样点,从中恢复出数据,从而在数据流中分离出每一个独立的码元,同时误码率很低[7]。只有确定每一个码元的起始时刻[8],才能对数字信息做出正确的判决,位同步它起着为接收信号提供基准的作用。一个数字通信系统需要经过很多的同步才能完成数据的通信,而位同步就是其中之一。位同步的数字化实现优点是在原有硬件电路的条件下,仅仅通过对代码的改写,下载到FPGA配置芯片中,配置各个功能模块以达到适应不同条件,实现技术要求。位同步(即码元同步)[9]常采用的方法有外同步法和自同步法两种[10]实现方案。外同步法是发送信号中插入同步信息,在接收端利用窄带滤波器分离出来,这就需要占用一定的带宽,多消耗一部分发送功率。自同步法又分开环同步法和闭环同步法[11]两种,其中闭环同步法克服了开环同步法同步跟踪误差大的缺点,所以此方法得到广泛应用。闭环同步法采用常见的超前-滞后数字锁相环提取位同步信息,也在工程中得到普遍的应用。这类方法同步速率要求更高的场合,位同步依旧比较慢,仍需一个较长时间建立同步。笔者依据实际工程项目,针对上述不足,对超前-滞后数字锁相环[12-13]方法进行改进。工程实践表明,改进后的位同步时间大大缩短,且设计成本低廉,可广泛应用在数字通信系统中。

2 数字锁相环的工作原理

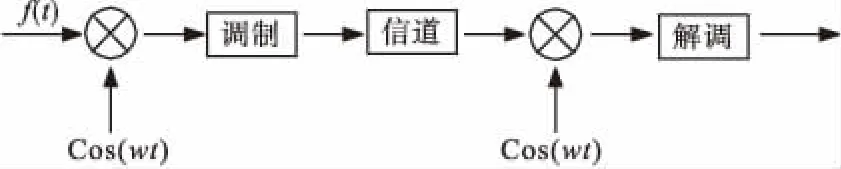

位同步是数字信号处理中最为核心也是技术要求最高的地方。调制解调的大体流程图如图1所示。

图1 调制解调流程

(1)

由式(1)知,信号解调最终由0.5f(t)和0.5cos(2ωt)f(t)两部分组成,其中0.5f(t)为解调出的原函数(也是工程所要的),仅幅值变为原来的一半。如果我们想要还原原函数,则0.5cos(2ωt)f(t)部分通过低通滤波器滤掉即可。如果解调端相位不能与调制端相位同步,则解调端数据很难还原出来。笔者在原超前-滞后数字锁相环方法基础上对该方法进行改进,能够适应更快的码元速度,降低锁相误差。改进数字锁相环原理方框图如图2所示。

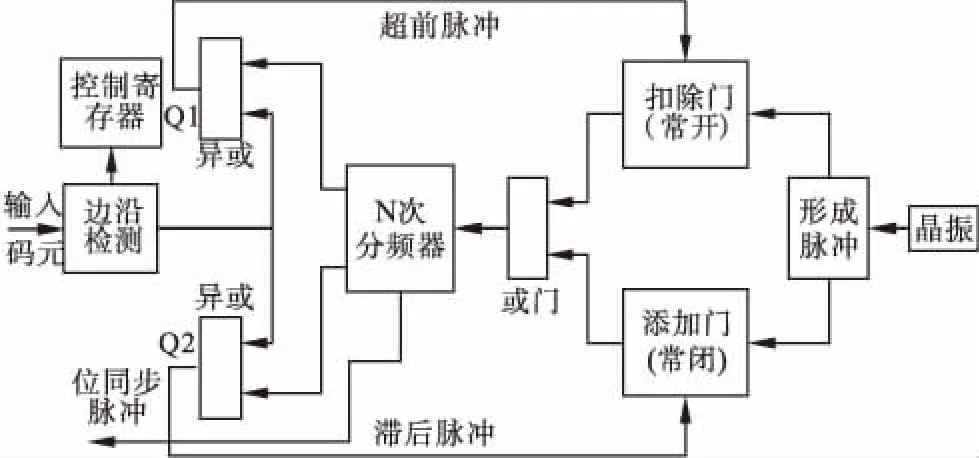

数字锁相环DLL由晶振、常开扣除门、常闭添加门、N次分频器、边沿检测器组成。改进了添加、扣除门的控制方式,把边沿检测时钟与分频器的时钟值进行异或,并把此值作为控制双门的脉冲量,相位调整在极短的时间内完成,在降低误差的前提下提高锁定速度。在该步,检测码元的边沿跳变恢复出一个与码元信号同步的时钟信号,设其频率为f,该环路中本地晶振产生频率为Nf,分别送入扣除门和添加门,经过两者“相或”输入N分频器。当信号相位超前时,Q1=′1′、 Q2=′0′,扣除门开启,控制分频器减少计数,添加门关闭,反之相反。随着码元信号的不断输入,该模块经过不断调整最终完成相位同步,即使输入码元和环路输出信号相位差π,锁相环做N/2次相位调整最终锁住相位。恢复时钟信号与分频器输出的时钟信号之间的相位差,可以理解为分频器的计数值与1的比值。当N值确定后即最佳接收时刻[14],对码元进行抽样判决恢复信号。在边沿检测模块基带信号提取时钟的同时添加了控制寄存器,通过对该寄存器的控制,使同步系统适应可变速率的码元[15]。

图2 数字锁相环原理方框图

3 位同步的FPGA实现方案

笔者采用VHDL语言,在ISE14.7开发平台上编程仿真,下载到Xilinx公司Kintex-7系列FPGA芯片实现数字锁相环设计。代码完全自主开发,以下是对各主要模块进行介绍。

3.1 形成脉冲模块

Clk200为本地时钟,输出clk_d1和clk_d2两路相位差为π的双相时钟,位同步环路中的系统时钟频率为数据采样频率的4倍,产生双相时钟信号的时钟频率不能小于双相时钟的4倍,从这段程序可以看出双相时钟clk_d1、clk_d2的周期为码元的采样周期,双相时钟相位相差一个clk200时钟周期,产生周期为码速率的8倍(采样速率),占空比为1∶3的双相时钟。

ENTITY clktrans IS

PORT(

rst:IN std_logic;

clk200:IN std_logic;

clk_d1:OUT std_logic;

clk_d2:OUT std_logic);

END clktrans;

ARCHITECTURE translated OF clktrans is

Signal c:std_logic_vector(1 downto 0);

Signal clkd1:std_logic;

Signal clkd2:std_logic;

Signal clk_d1_xhdl1:std_logic;

Signal clk_d2_xhdl2:std_logic;

BEGIN

clk_d1 <= clk_d1_xhdl1;

clk_d2 <= clk_d2_xhdl2;

PROCESS

BEGIN

Wait until(clk200′event and clk200 = ′1′)or(rst′event and rst = ′1′);

IF(rst = ′1′)THEN

C <= "00";

clkd1 <= ′0′;

clkd2 <= ′0′;

ELSE

c <= c + "01";

IF(c = "00")THEN

clkd1 <= ′1′;

clkd2 <= ′0′;

ELSE

IF(c = "10")THEN

clkd1 <= ′0′;

clkd2 <= ′1′;

ELSE

clkd1 <= ′0′;

clkd2 <= ′0′;

END IF;

END IF;

END IF;

END PROCESS;

clk_d1_xhdl1 <= clkd1;

利用向量空间模型计算文本相关度是一种常用的计算相关性的方法,在本文中,实现了该算法。问题集特征项的权值计算公式为

clk_d2_xhdl2 <= clkd2;

END translated;

3.2 扣除添加门控制量模块

计算超前-滞后值,输入信号微分整流,检测输入信号跳变沿后,产生一个clk200时钟周期的高电平脉冲,取输入数据的符号位为码元起始相位,仿真结果如图4~图6所示。

ENTITY differpd IS

PORT(

rst:IN std_logic;

--复位信号,高电平有效

clk200:IN std_logic;

--FPGA系统时钟:200MHz

--输入数据

clk_i:IN std_logic;

--由控制分频模块送来的同相同步脉冲信号(占空比为1:1)

clk_q:IN std_logic;

--由控制分频模块送来的正交同步脉冲信号(占空比为1:1) pd_bef:OUT std_logic;

--输出的超前脉冲信号

pd_aft:out std_logic);

--输出的滞后脉冲信号

END differpd;

ARCHITECTURE translated OF differpd IS

Signal pdbef:std_logic;

Signal pdaft:std_logic;

Signal pd_bef_xhdl1:std_logic;

Signal pd_aft_xhdl2:std_logic;

begin

pd_bef <= pd_bef_xhdl1;

pd_aft <= pd_aft_xhdl2;

din <= datain(5);

Process

begin

wait until(clk200′event and clk200 = ′1′)

or(rst′ event and rst = ′1′);

IF(rst = ′1′)THEN

pdbef <= ′0′;

pdaft <= ′0′;

ELSE

pdbef <= din_edge AND clk_i;

pdaft <= din_edge AND clk_q;

END IF;

END PROCESS;

--完成鉴相功能

pd_bef_xhdl1 <= pdbef;

pd_aft_xhdl2 <= pdaft;

END translated;

3.3 N分频器

对gate_open及gate_close相“或”后,作为分频器的驱动时钟,该时钟经过N分频后作为位同步信号。

ENTITY controldivfreq IS

PORT(

rst:IN std_logic;

clk200:IN std_logic;

clk_d1:IN std_logic;

clk_d2:IN std_logic;

pd_before:IN bit;

pd_after:IN std_logic;

clk_i:OUT std_logic;

clk_q:OUT std_logic);

END controldivfreq;

Architecture translated OF controldivfreq Is

Signal gate_open:std_logic;

Signal gate_close:std_logic;

Signal clk_in:std_logic;

Signal clki:std_logic;

Signal clkq:std_logic;

Signal c:std_logic_vector(2 downtown 0);

Signal clk_i_xhdl1:std_logic;

Signal clk_q_xhdl2:std_logic;

BEGIN

clk_i <= clk_i_xhdl1;

clk_q <= clk_q_xhdl2;

gate_open <=(NOT pd_before)and clk_d1;

gate_close <= pd_after AND clk_d2;

clk_in <= gate_open OR gate_close;

--对gate_open及gate_close相“或”

后,作为分频器的驱动时钟

PROCESS

BEGIN

wait until(clk200′event and clk200= ′1′)or(rst′ event and rst=′1′);

IF(rst=′1′)THEN

c<="000";

clki<=′0′;

clkq<=′0′;

ELSE

IF(clk_in=′1′)THEN

c<=c + "001";

END IF;clki<= NOT c(2);

clkq<=c(2);

END IF;

END PROCESS;

clk_i_xhdl1<=clki;

clk_q_xhdl2<=clkq;

END translated;

3.4 NCO模块

实例化NCO核,ISE提供的NCO核输出数据最小位宽为10比特,根据环路设计需求,只取高8比特参与后续运算,在该模块对输出的正弦波信号进行处理使得输出的数据与《数字通信同步技术的MATLAB与FPGA实现》(Xilinx/VHDL版)中的数据完全一致,以便比较仿真结果,同时计算寄存器“carrier”值,为可变速率设置变量,开始时默认速度为1Mbps。

ENTITY DinProduce is

Port(

rst:IN std_logic;

clk200:IN std_logic;

cosine:IN std_logic_vector(5 downto 0));

Architecture translated of DinProduce IS

Signal clk8:std_logic;

Signal c:std_logic_vector(1 downto 0);

Signal reset_n:std_logic;

Signal out_valid:std_logic;

Signal clken:std_logic;

Signal carrier:std_logic_vector(29 downto 0);

Signal cos:std_logic_vector(9 downto 0);

Begin

reset_n <= !rst;

clken <= 1′b1;

carrier <= 30′d67108864;

--0.5MHz正弦波,1MHz码元速率,该数值变化随着后续寄存器所给值,最大为20M。

u0:cos u0

port map(

phi_inc_i => carrier;

clk => clk8;

reset_n => reset_n;

clken =>clken;

fsin_o => cos;

out_valid =>out_valid);

PROCESS

BEGIN

wait until(clk200′ event and clk200 = ′1′)or(rst′ event and rst = ′1′);

IF(rst = ′1′)THEN

c<="00";

clk8 <= 0;

ELSE

c<=c+"01";

clk8<= c[1];

END IF;

END PROCESS;

--该过程对输出的正弦波信号进行处理

Process

Begin

wait until(clk200′ event and clk200 = ′1′)

if(cose==-6′d13)cost = -6′d12;

else if(cose==6′d13)cost = 6′d12;

else if(cose==6′d22)cost = 6′d23;

else if(cose==6′d29)cost = 6′d30;

else cost = cose;

end if;

end process;

end translated;

4 设计仿真

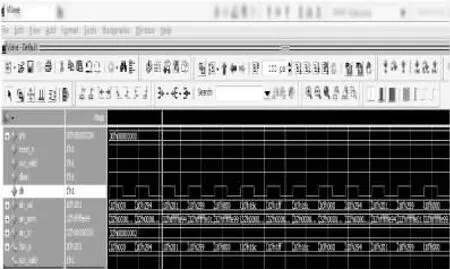

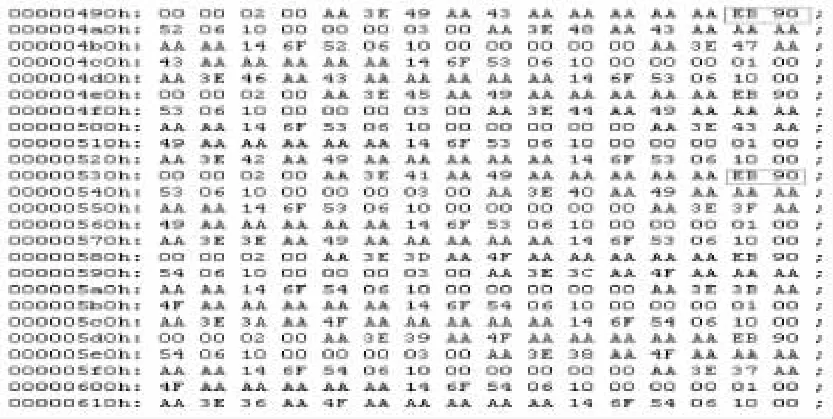

Modelsim仿真波形图如图3~图5所示,其中图3为锁相环自由状态,该状态“out_valid”处于拉低状态,等待基带信号输入。图4为相位同步准备,从波形图中可以看到,当基带信号进来时(余弦函数数据),经过不到半个周期的检测准备,如图中黄线标识,在时钟上升沿数据对齐,位同步时间为一个码元周期。图5锁相环相位同步成功,图6为常规数字锁相环在码元速率接近4M时开始出现失锁现象,稍后数据便完全恢复不出。经改进后位同步支持1Kbps~20Mbps,步长以0.5Kbps变化的可变速率。从仿真结果得到,改进后的数字锁相环,同步建立时间短。设计选用Xilinx公司推出的Kintex-7系列的XC7K325T来设计位同步的信号提取电路,该FPGA设计在28nm节点,同时提供高DSP率并支持PCIe(为后续上位机设计提供接口),逻辑单元为162240,即使在无外部DDR辅助条件下,对整个项目工程代码存储依旧游刃有余,同时可靠性高等优点。笔者在后面给出位同步后解调成功的实际工程结果,以供参考。

图3 锁相环自由状态

图4 相位同步准备

图5 锁相环相位同步成功

图6 常规锁相环失锁

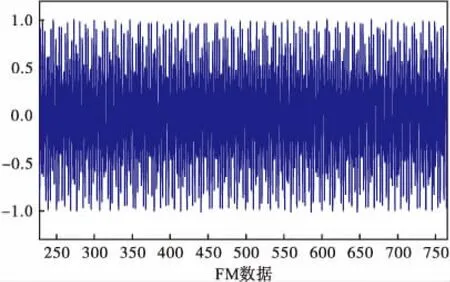

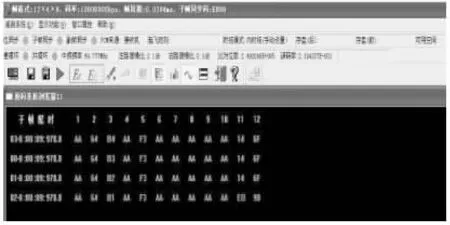

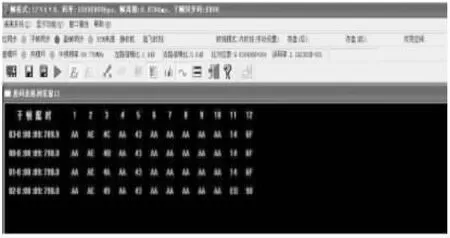

为保证位同步的成功、达到预期的同步速度并且大大降低解调的误码率之前,笔者首先对该数据源调制结果的正确性也进行了验证,将调制的数据源分别进行MATLAB仿真和实际工程中通过chipscope对数据进行抓取,保证实验的严谨性和正确性。图7为调制数据的MATLAB仿真结果。

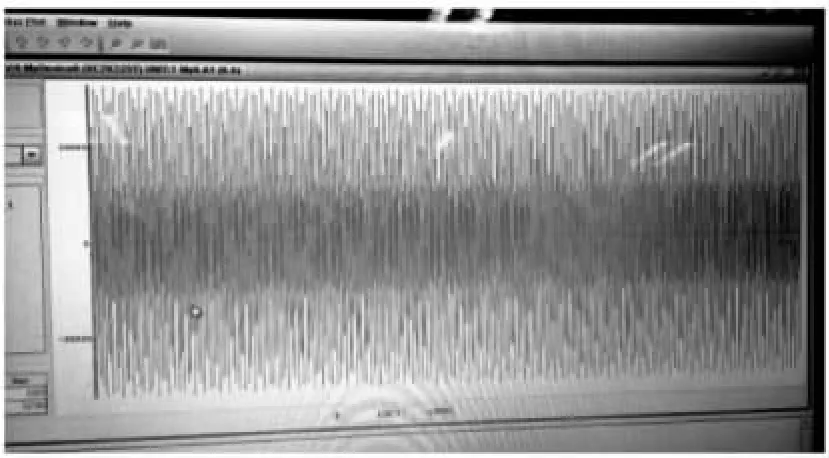

在与仿真具有相同数据源前提下,图8为Chipscop抓取实际工程数据。

图7 调制MATLAB仿真结果

图8 调制工程实际结果

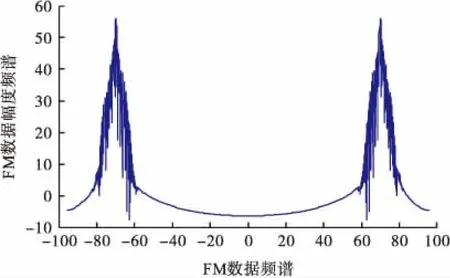

通过chipscop导出实际工程结果的“.prn”文件画其频谱图,图9为调制数据频谱,由图可以看出数据的频谱是落在70M与实际工程结果相一致。经判定调制数据正确。

图9 调制数据频谱

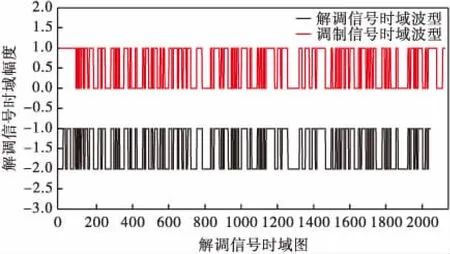

图10为MATLAB仿真解调后的数据与原数据源结果对比值,如图中标识所示红色为调制之前即原数据源,蓝色为位同步解调后数据,二者数据吻合位同步成功。

图11为实际工程中接收端解调的部分数据,从图中可以找到数据的帧头为“EB90”。数据源格式是严格依据国军标的要求设计,为验证接收端数据接收正确,位同步成功,在该数据源中,加入常值、锯齿波和正弦波三种形式的数据。

图10 解调结果与原数据源对比时域结果

图11 接收端解调数据

对比图12、图13可知,该数据子帧格式为4行12列,第一列和第4列为常数,在图14中黄线为1、4两列的常数值,因为相同数值,波形重合所以只能看到4一条数据线。第三列为锯齿波数据,观察图12、图13,以“4C4B4A49”和“B4B3B2B1”为例,数据一直变小然后往复变化。

图12 接收端数据1

图14波形为正弦波,数据随发送端数据源在每一时刻都在变化,图12、图13两个时刻数值“F3”变到“43”在下一时刻数值根据正弦波规律,再变化到另一数值,其他同理,在此不再一一赘述。

图13 接收端数据2

图14 接收端数据波形

5 结论

笔者对超前-滞后型数字锁相环方法改进,进行了可变速率快速位同步整体仿真。仿真码元采用1Kbps20Mbps可变速率码元,变化步长为0.5Kbps,基带信号快速达到位同步,锁定相位时间快、误差小。该方法在Xilinx 公司Kintex-7系列XC7K325T芯片下得到验证,并成功应用到某项目中。