基于MAX9259/MAX9260的CameraLink图像数据光纤传输技术

陈洋君,吴志勇,崔 明,张维达,范日召

(1.中国科学院 长春光学精密机械与物理研究所,吉林 长春 130033; 2.中国科学院大学,北京 100049)

1 引 言

随着数字图像[1]数据量的急剧增加,传输速率的不断提高[2],以及为了满足数据处理相关性高,长距离传输等需求,对传输系统的要求越来越高。本文采用一种基于SerDes芯片组MAX9259/9260的串行/解串行技术,并将其应用到base型Cameralink光纤传输系统的串并转换模块中。即CameraLink接口作为相机和图像采集卡间的通信接口,以FPGA为核心实现了数据的采集和预处理,以MAX9259/9260作为系统的串行收发器,经光纤传输后,最终实现了图像数据的远程无失真传输。

作为工业数字相机的主要图像输出接口之一的Cameralink接口,采用并串结合的方式实现大数据量的传输,该接口具有实时性好和抗干扰能力强的优点。同时光纤通信[3]具有抗噪声干扰性强、抗电磁干扰、通信容量大、保密性强,适于远距离传输等优点,可以提高图像传输的速率和可靠性。传统系统中,串并转换模块大多采用TLK2711[4]等,由于不能提供足够的并行总线,需要通过内部实现时分复用/解复用以及图像重组,同时还存在图像数据时钟域的匹配问题等,大大增加了开发难度。与传统的光纤传输系统相比,本系统选取了功能强大,应用广泛的SerDes芯片组MAX9259/X9260作为串行收发器,其与传统的串行收发器TLK2711等相比,省去了时分复用/解复用和时钟域匹配操作,大大降低了CameraLink光纤通信的开发难度,同时提高了系统的适应性。

2 基于CameraLink接口的光纤传输技术

2.1 关于CameraLink接口

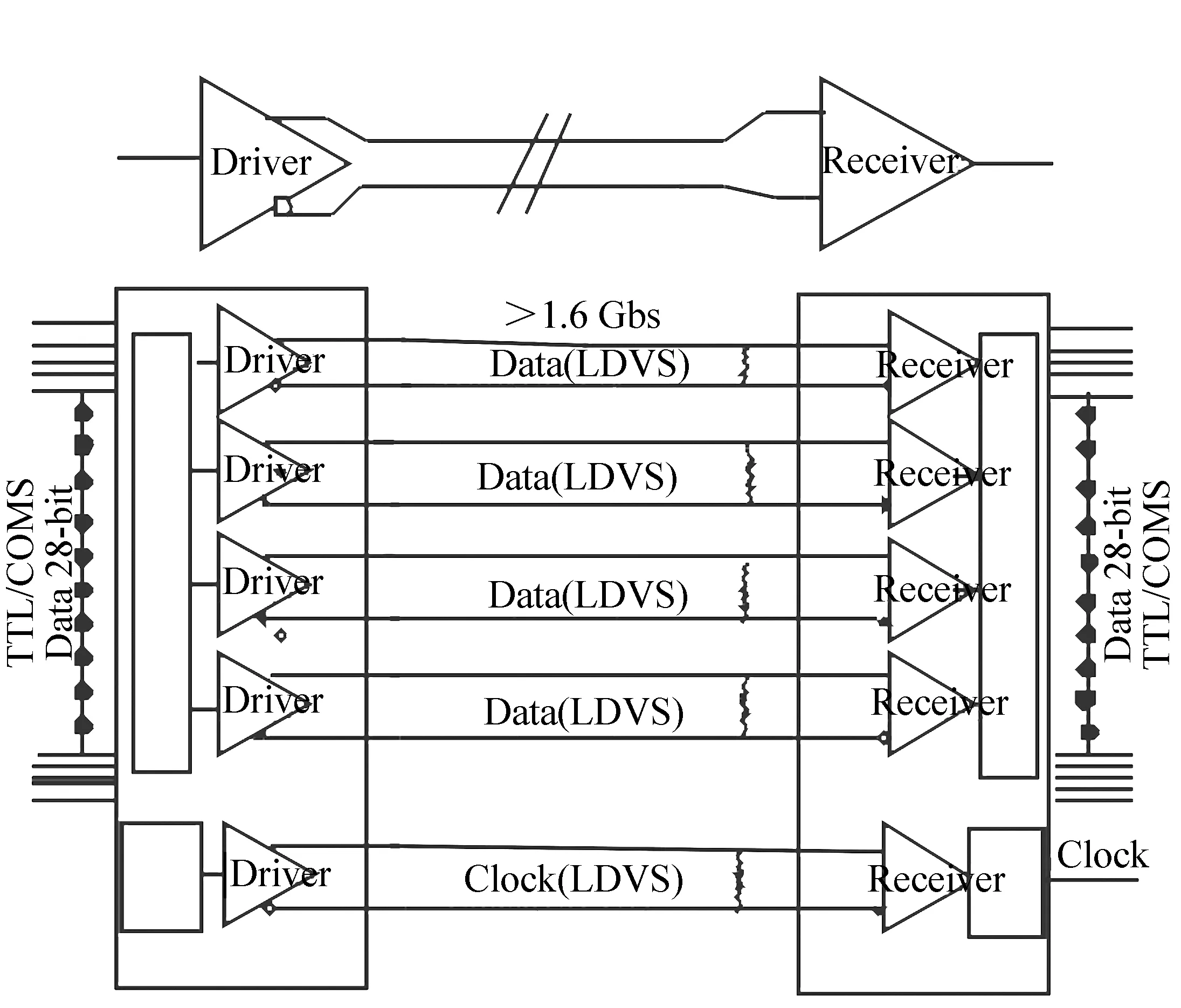

CameraLink接口是一种视频应用的通用接口,是ChannelLink技术的扩展[5],它为相机和图像采集卡提供了一种标准连接。CameraLink接口采用了多路低电压差分信号(Low Voltage Differential Signal,LVDS)进行通信,其传输速率可达到2.38 Gb/s。CameraLink接口由一个驱动器和一个接收器组成,驱动器接收一路clock信号以及28路并行数据信号[6-8]。数据信号以7∶ 1形式分成4对数据流,加上clock信号流,一共有5对低电压差分信号。接收端用于接收这5对信号。转换原理如图1所示。

图1 CameraLink转换原理图 Fig.1 Block diagram of cameraLink conversion

CameraLink接口相机定义3种输出信号:相机控制信号、相机配置串行通信信号和视频传输信号。核心部分是视频传输信号,其中包括了X0-~X0+、X1-~X1+、X2-~X2+、X3-~X3+、Xclk-~Xclk+这5对低压差分信号;相机控制包括4对差分信号,即CCl-~CCl+、CC2-~CC2+、CC3-~CC3+、CC4-~CC4+;串行通信部分包括2对差分信号,即SerTC-~SerTC+和SerTFG-~SerTFG+。

CameraLink接口相机具有Base型、Medium型和Full型3种模式[9-10]。本系统是在Base模式下进行研究的,数据信号共有28位,其中包括A、B、C三个8位的数据端口,以及FVAL(帧有效)、LVAL(行有效)、DVAL(数据有效)、SPARE(空)4个视频控制信号。

在整个过程中相机的驱动信号、全部的数据信号、以及控制信号都与经CameraLink转换后的时钟信号同步。

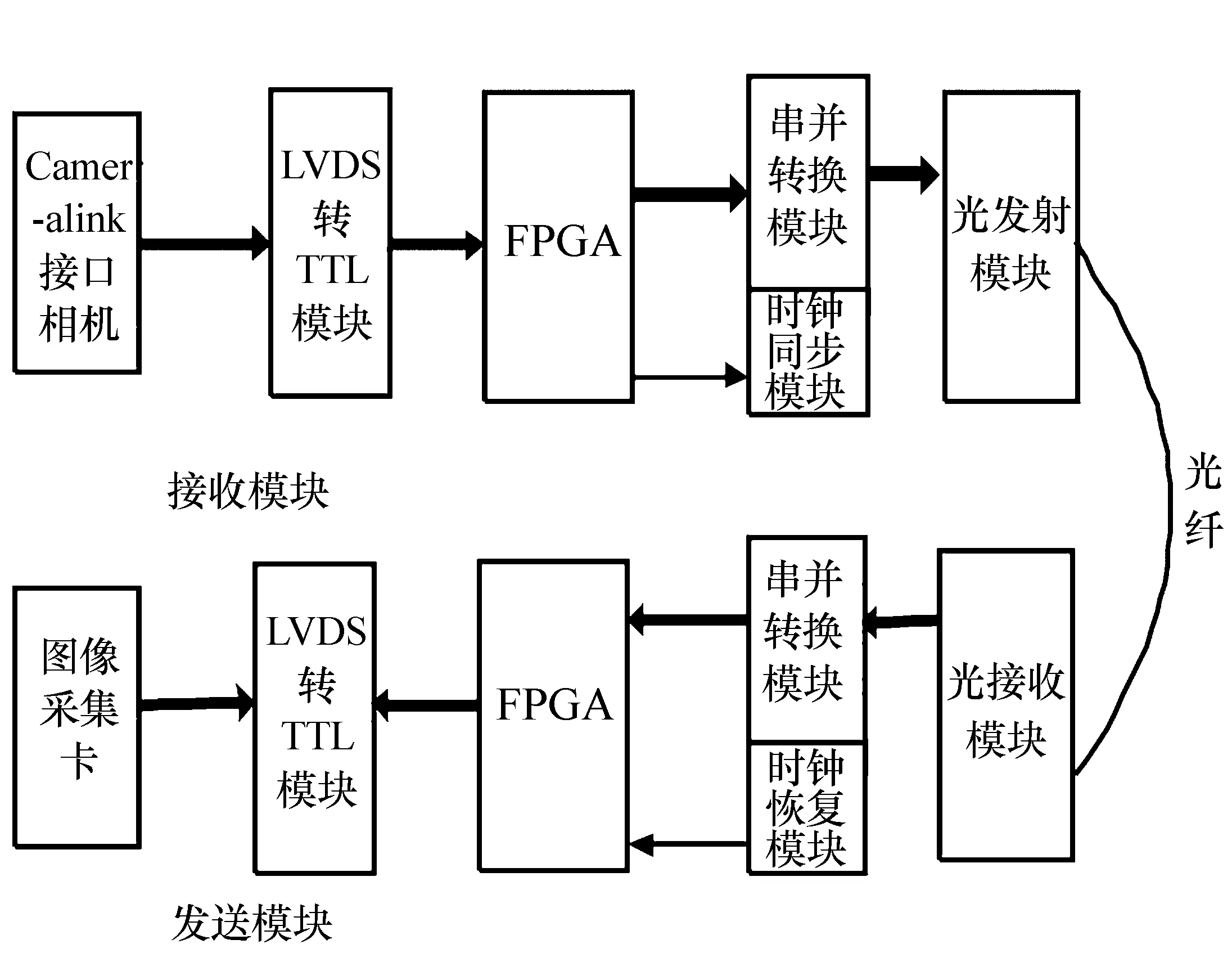

2.2 基于CameraLink接口的光纤传输系统

图2为基于CameraLink接口的光纤传输系统[11]的结构框图,整个系统的工作流程如下:首先由LVDS转TTL模块将相机输出的LVDS信号转换成TTL信号并直接送入FPGA[12],在相机同步信号的控制下,由FPGA完成对数据的采集以及预处理;然后,经串并转换模块处理后,为光发射模块传输提供所有信号。光接收部分同理。整个系统主要由以下几个单元模块组成,即:CameraLink接口模块、FPGA图像采集和预处理模块、串并转换模块、时钟同步模块、光电转换模块。

图2 系统硬件结构框图 Fig.2 Block diagram of system hardware

3 基于SerDes芯片组MAX9259/MAX9260具体方案设计

SerDes(Serializer/Deserializer)是目前主流的一种点对点(P2P),时分多路复用(TDM)的串行通信技术,即在发送端多路低速并行信号被转换成高速串行信号,经过传输媒体(光缆或铜线)后,在接收端高速串行信号重新转换成低速并行信号。

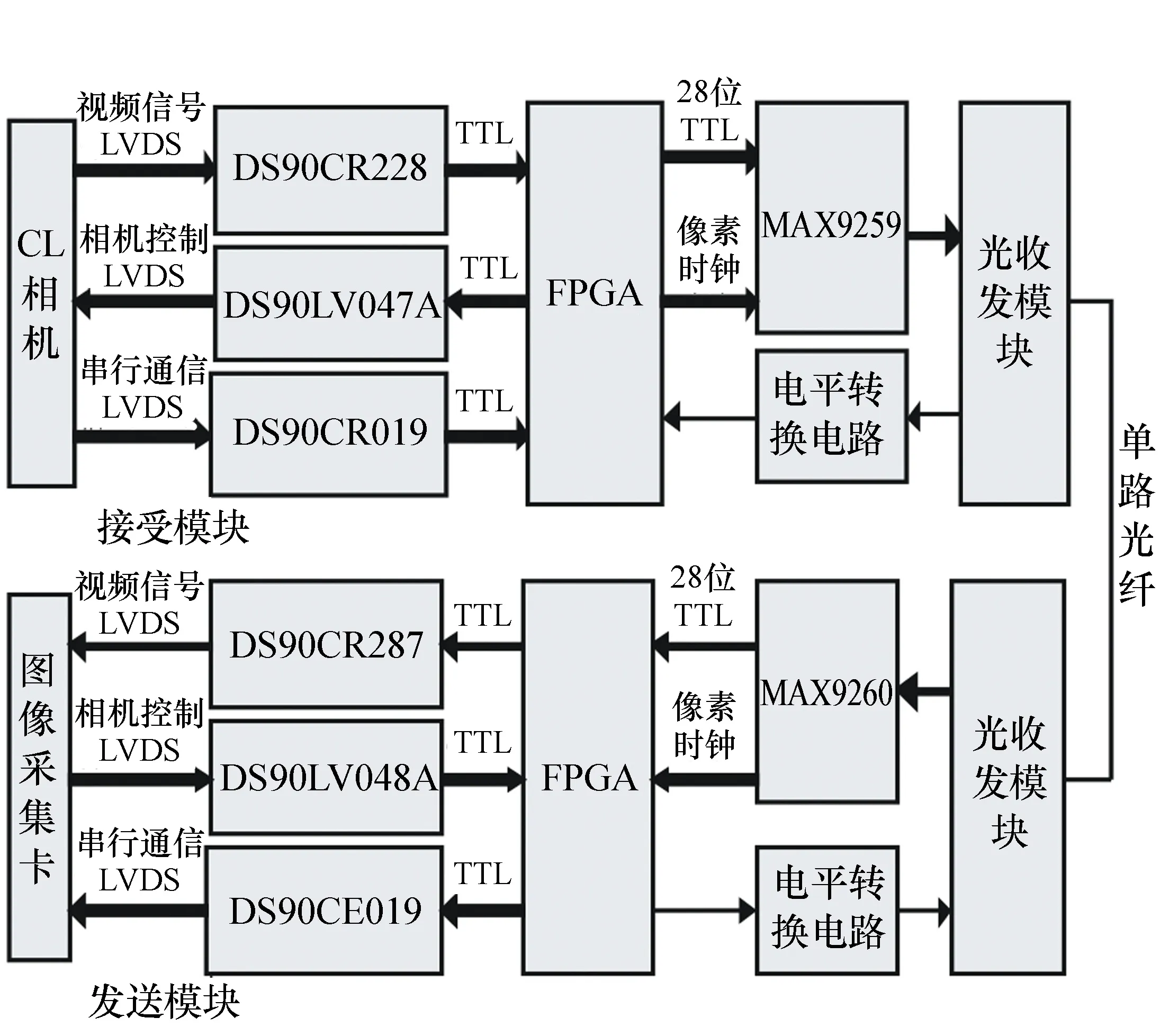

图3为本文设计的光纤传输系统设计方案。具体工作过程如下:在接收模块,像素时钟作为同步时钟,经DS90CR288解码以及FPGA预处理后,直接把1路异步串行通信数据以及28位并行数据输出到串并转换收模块。在发送模块,像素时钟及时恢复到同步状态,同时又作为 FPGA 的系统时钟,此时串并转换发模块从输入的高速串行数据中提取帧信号后被FPGA送到DS90CR287中进行编码。其中,电平转换电路用于对FPGA与光收发模块之间进行电平转换,完成了相机与图像采集卡两者间的通信。

图3 系统实现框图 Fig.3 Specific system implementation block

3.1 串并转换收发模块

串并转换模块用于对信号进行串并转换,使光模块高速传输所有信号。目前,在Cameralink光纤传输领域,应用最广泛的是基于TLK2711,DS90UR241的串并转换模块。鉴于TLK2711和DS90UR241分别只能提供16位和24位并行数据,给任务实现带来了一定的难度,具体体现在以下两个方面:数据时钟的匹配性问题,即像素时钟与光纤通信同步时钟的匹配问题。它需要通过采用FIFO技术进行数据缓存调整;数据的位数问题,CameraLink接收模块输出的是30位并行TTL信号,这时候需要在核心芯片FPGA中采取分时复用/解复用的方法进行重组图像信号[15]。虽然这些问题都可以通过相应办法解决,但是它对系统硬件提出了更高的要求,同时加大了FPGA的开发难度。

针对串行/解串行芯片TLK2711[16]和DS90UR241传输方式存在的问题,本系统采用SerDes芯片组MAX9259/MAX9260[15]作为串并转换模块的核心芯片。该芯片组基于吉比特(千兆 )多媒体串行链路(GMSL)的原理,由串化器芯片MAX9259配合解串器MAX9260组成数字串行链,共同传输高速数据。其最大串行数据速率达到了2.5 Gb/s,同时具有两种模式,即24/32位并行总线模式。其中32位模式下的最大总线时钟达78 MHz;24位模式下的总线时钟则可高104 MHz。

本系统的串行/解串行芯片设置为32位模式,当像素时钟要求小于78 MHz,可直接完成29位数据(28位TTL并行数据和1路异步通信数据)的串行数据转换。

在这一过程中,纵使相机像素时钟发生了改变,串并转换发模块的时钟也能实时改变,同时在整个传输过程中,光纤通信的同步时钟以及FPGA的系统时钟也都是由像素时钟决定的,从而保证了整个系统图像数据传输的同步性。

3.2 接口模块

接口电路主要用于完成数字图像信号的传输以及相机与采集卡之间的串行通信与控制等。以发送部分为例:系统采用应用较广的DS90CR288作为CameraLink接收芯片,它的主要功能是将4路LVDS数据信号和一路LVDS时钟信号转换成TTL电平标准的图像信号和时钟信号,并输入到FPGA中。

在控制信号的电平转换电路设计上,根据CameraLink协议要求,采用DS90LV047芯片对相机的控制信号进行电平转换,相机控制信号包括CC1、CC2、CC3、CC4。具体工作过程为:FPGA发出控制相机的命令(为TTL电平信号),经过DS90LV047将FPGA发出的TTL电平信号转换为LVDS信号再传给相机,从而实现对相机的控制。

在相机串行通信信号电平转换电路设计上,选用具有差分发送和差分接收功能的DS90LV019芯片完成串行通信(其中包括2对差分信号SerTFG、SerTC),即通过将两对LVDS差分信号与TTL信号之间的相互转换,实现相机端和数据处理端的通信。

3.3 光模块

光模块[14]也称为光收发一体模块。它的组成部分包括光电子器件、功能电路和光接口等,光电子器件又由发射和接收两部分构成。

发射部分的工作原理是:输入的电信号经过驱动芯片后,由发光二极管或半导体激光发射相应的调制光信号。同时利用光功率控制电路自动稳定输出光信号功率。接收部分的工作原理是:输入的光信号经过光探测二极管后,转换成相应的电信号,相应的电信号由前置放大器输出。10G光模块主要包括光/电转换、时钟提取和同步、复用/解复用、64B/66B编解码、WIS、8B/10B编解码等子功能模块[17],有300pin、Xenpak、Xpak、X2和XFP等封装形式。

本文采用的是收发一体、单模双向的XFP封装形式,来完成光电信号之间的转换。采用波分复用技术实现两种光信号共用一个信道,从而完成双向通信功能。在发送端的发送单元光波长为1 310 nm,接收端的光发射单元光波长为1 550 nm,该光模块结构小巧,价格相对廉价,使用方便灵活。

4 实验结果分析

实验首先采用模拟相机数据源[18]测试了系统设计的正确性,以及传输通路中存在的问题。采用Verilog HDL硬件描述语言进行时序设计,完成了分辨率为320 pixel×256 pixel,像素时钟为40 MHZ,帧频为100 Hz,像素深度为14位的相机模拟源,然后将程序下载到FPGA进行验证。

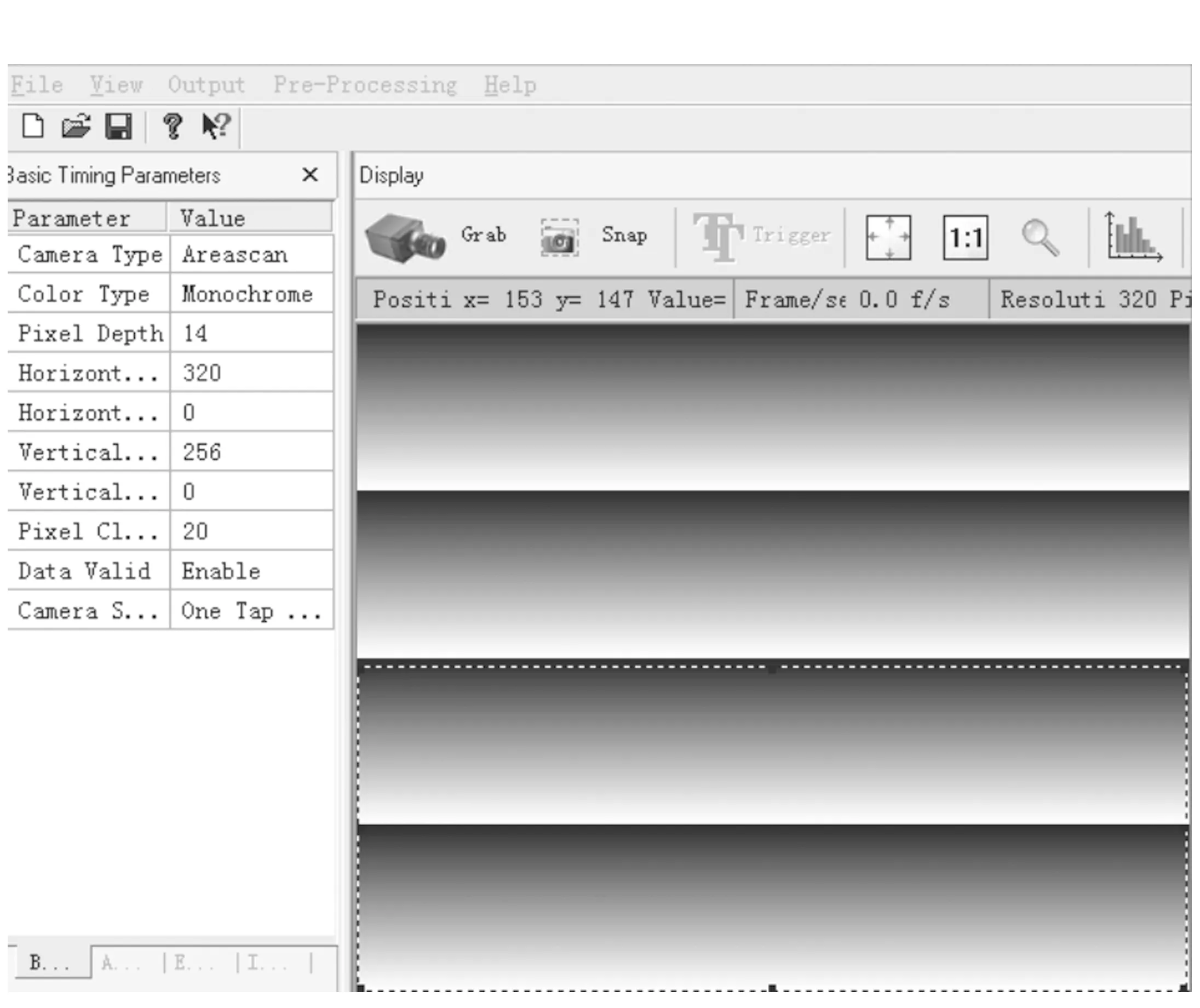

当FVAL、LVAL、DVAL时为高电平时,才能输出数据,每14 bit为一个数据,从0开始,每一行的各像素点数值相同,行与行之间数据值加64。采集卡采集到的渐变条图像如图4所示。从采集到的渐变条图像中截取了有代表部分(图4虚线框部分所示)的像素值,如图5所示。像素值的变化符合模拟图像源的设计要求,验证了系统的正确性。

图4 数据合成采集卡渐变条显示图 Fig.4 Gradient bar graph for data synthesis acquisition card

接着,实现了型号为MC1362(像素时钟最高工作在80 MHz)的MIKROTRON可见相机的CameraLink数字图像的光纤传输验证实验。相机工作模式设置为2×8 bit,相机的帧频为100 Hz,分辨率为1 024 pixel×1 024 pixel,将相机输出的Base接口连接到系统的图像发送端,图像采集卡采集到的数字图像如图6所示。

与其他同类技术相比较,整个系统的优势在于:通过采用相机的像素时钟,避免了多个时钟域匹配带来的麻烦。另外,由于SerDes芯片组MAX9259/MAX9260,其本身就提供了足够位数的并行总线,因此FPGA不需要进行时分复用等工作,只需要执行简单的数据分配即可。从而使其设计简单,效率更高。

5 结 论

本文提出一种系统,其采用了一种新的串行/解串行技术,基于Base型CameraLink标准信号的远距离传输,实现了数字图像的光纤传输。本文设计的核心为利用SerDes芯片组MAX9259/MAX9260串行收发器代替光纤传输系统常用的串并转换模块(基于TLK2711和DS90UR241等)。该方法省去了数据通道的时分复用、异步FIFO数据缓存的繁琐开发过程,大大简化了设计的复杂度。实验结果表明,图像数据光纤传输系统工作性能稳定,传输图像效果较好,传输带宽达到2.5 Gb/s(相机时钟要求小于78 MHz)。接下来将致力于如何提高传输信息正确性的研究,以及解决噪声干扰等问题。