采样率变换及在基带信号发生器中的应用

李增红 周时建 左永峰

【摘 要】采样率变换方法在数字信号处理中得到日益广泛的应用。本文在比较了半带滤波器、级联积分梳状滤波器和多相滤波器等典型采样率变换滤波器结构的基础上,重点分析了采样率变换的原理,结合实际应用要求提出了一种新的法罗滤波器结构实现方式。并阐述了此种结构在FPGA内部的具体设计方法。本文最后给出的此方法在实际基带信号发生器中的测试结果,证明了其有效性。

【关键词】采样率变换;法罗滤波器;基带信号发生器

中图分类号: TN2 文献标识码: A 文章编号: 2095-2457(2018)23-0107-002

DOI:10.19694/j.cnki.issn2095-2457.2018.23.047

【Abstract】The method of sample rate conversion is widely used in digital signal processing.In this paper,a comparison of a series of typical filters with the sample rate conversion structure,such as halfband filter,cascade integrator comb filter and poly-phase filter is provided.Then based on an analysis of the sample rate conversion principle,a novel implementation model of Farrow filter is proposed.A design method of the proposed model is illustrated in FPGA. Finally a group of test results achieved in a baseband signal generator are given to prove the validity of the proposed method.

【Key words】Sample Rate Conversion;Farrow filter;Baseband signal generator

0 引言

基带信号发生器是矢量信号发生器中的主要核心部件之一[1],主要负责为矢量调制器提供ASK、FSK、PSK、QAM等各种通用的数字调制及任意波调制信号,最终实现对射频或微波信号调制。在早期,一般都是通过改变基带信号发生器中DAC的采样率,配合后端多种重构滤波器,来满足用户的不同带宽的测试需求。随着数字信号处理技术的发展,现在基带信号发生器都通过数字处理的方法来采样率变换,以满足用户不同带宽的要求。这种方法可以避免了原有的时钟合成电路,同时DA后端的重构滤波器也得到了简化。其基本流程如下:基带信号发生器中数模转换器(DAC)的采样率都固定在较高的频率上,后端重构滤波器都按照40%的奈奎斯特带宽进行设计。当需要小带宽信号的时候,通过采样率变换(SDR)[2]技术来将低速数据通过内插变换到固定采样率上。采样率变换一般在数字域上通过数字滤波器实现,常用的变换结构有级联积分梳状滤波器(Cascade Integrator Comb Filter,CIC)、半带滤波器、多相滤波器、法罗滤波器等。这几种滤波器通常用于整数倍的采样率转换或者通过先升采样I倍再降采样D倍完成I/D倍的小数采样率转换[4],但是I、D都不能太大,否则滤波器的复杂度会急剧增加,计算效率会降低。Farrow[3]滤波器结构可以克服半带滤波器、CIC滤波器和多相滤波器的缺点,可以实现任意倍的采样率变换,而且它的滤波器系数是非时变的[7],整个过程中唯一改变的是数字延时,只要通过调整数字延时就可以实现任意分数的采样率转换,是一种可实现任意采样率转换的高效硬件结构。

1 采样率变换原理及法罗滤波器结构

采样率变换原理可以通过下图1所示的信号重构后重采样模型来描述[4]:

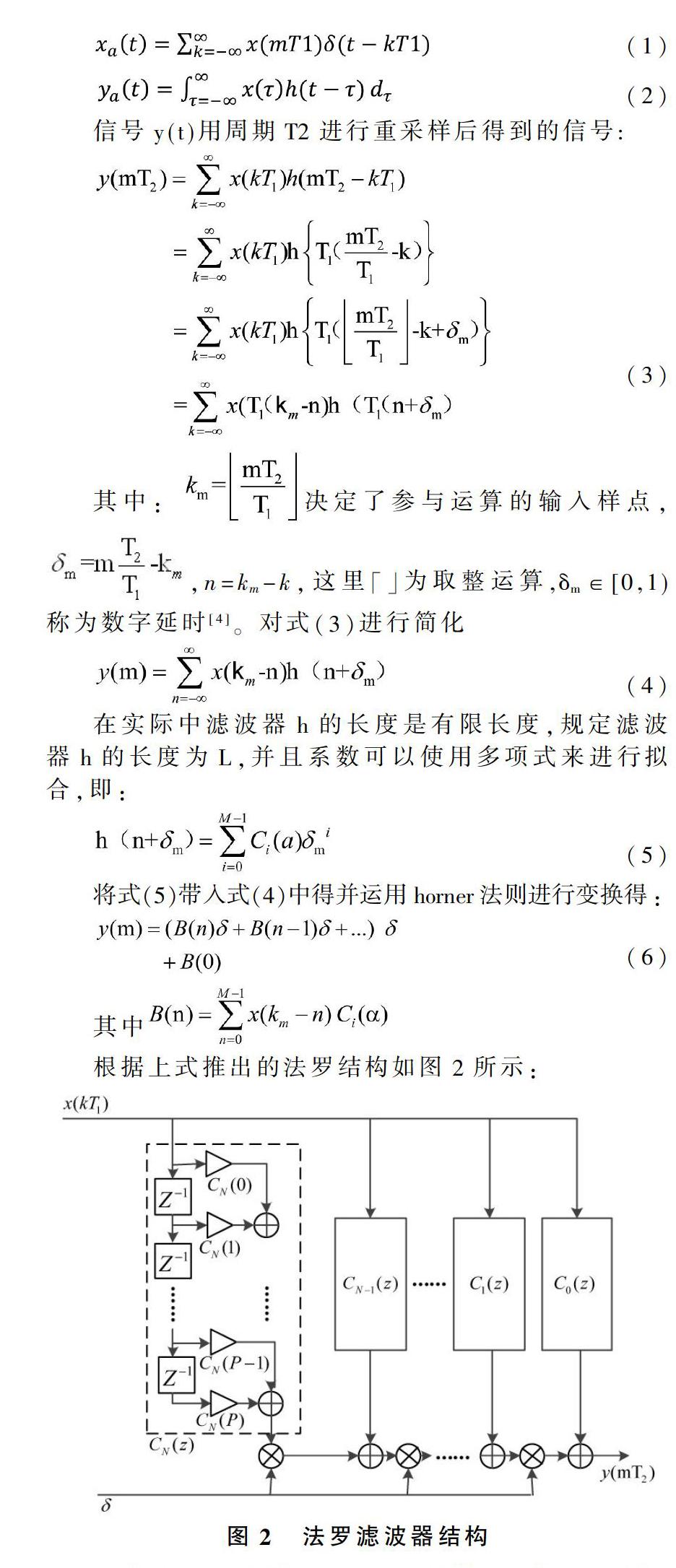

根据上式推出的法罗结构如图2所示:

整个采样率变换的过程中,滤波器的系数是固定的,只有数字延时δ是随时间改变的。在插值情况下,数字延时δ表示当前输出与之前最近的输入之间的距离,并对输入周期进行归一化[12]。从法罗滤波器[13]实现结构图中可以看出,每一个输出都由N个输入计算而得,这一组输入先通过几组子滤波器,得到B(i),i=0,1,2…….n,再将B(i)与δ作一系列乘加运算得到最终输出Y。

2 法罗滤波器的应用及FPGA实现

在某型基带信号发生器的设计中,要求基带最大带宽80MHz,码元速率在1Hz~100MHz连续可变,分辨率要求1Hz。根据奈奎斯特定理,采用200MHz的采样率的16位DA转换芯片。脉冲成形滤波器采用了2或4倍的内插。后端经过采样率变换后内插到200MHz固定频率上。通过以上描述可以看出,该款基带信号发生器对后端的输出采样率变换部分要求非常高:1)内插倍数的变化范围大,分辨率高。可以算出要求采样率变换的内插的倍数在1~50x之间连续可变。根据要求的分辨率,可以算出采样率变换的分辨率在0.0001以上;2)對带外抑制比较高。在采样率变换过程中,必然会出现信号频谱扩展,这一部分信号对基带信号发生器来说就是有害的杂散信号。在仪器里面一般要求杂散信号小于60dBc;3)对带内的频响要求高。因为基带信号发器产生的信号为宽带信号,信号的带内频响将会影响基带信号发生器输出的矢量调制误差(EVM)。模拟电路不可避免会导致频响恶化。为了避免矢量调制误差的进一步恶化,一步都会尽量提高数字处理部分的频响指标。。通过以上对采样率变换部分要求描述可以看出,如果采用常规的半带滤波器或CIC滤波器等来实现内插,则分辨率无法满足要求,而且占用的资源将非常大,程序非常复杂。为此我们将多项滤波器和法罗结构的滤波器进行结合,来实现的采样率变换功能。在设计中我们设计了32倍内插低通滤波器,将滤波器系数设计为256阶。在matlab中调用firpm函数生成滤波器系数,并将滤波器系数排列成32X8的系数组,每组有32个系数,通过调用polyfit函数,采用4节多项式逼近32个系数,系数最大误差小于1.0X10-5,满足16位分辨率的要求。最终在FPGA内部8组系数,每组系数有5个多项式系数组成。在工作时,计算机将需要的内插值送入FPGA内部的累加器中,累加器每次溢出,输入数据更新一次。累加器的其它数据作为差值,送入乘法器,进行其它计算,最终FPGA内部实现的滤波器的结构框图如图3所示,主要接口有IQ两路16位的数据数据,内插比输入,时钟信号输入及内插后的IQ两路16位输出接口。考虑到多项式系数固定,可以通过查找表来实现乘法运算,占用FPGA资源主要乘法器8个,最高运行速度可以达到250MHz。

表1给出了不同码元速率下对应的内插下测试的矢量幅度误差结果。成形滤波器为根升余弦滤波器,滤波因子为0.35,在码元输入小于50MSPS时,成形滤波器的内插倍数为4倍,其它情况下,成形滤波器的内插倍数为2倍。码元IQ数据经过成形滤波后,采样率提高了4倍或两倍,在经过法罗内插滤波器进行采样率变换到200MHz。从测试结果上来看,当码元速率为1kSPS,内插50000倍时,矢量误差幅度(EVM)为0.3%。当码元速率在100M SPS、内插倍数为1倍时,矢量误差幅度(EVM)为0.61%。在内插倍数有50000减少到1时,矢量误差幅度(EVM)有0.3%恶化到0.6%,表明设计的采样率变换滤波器的效果较好,满足实际要求。

4 结束语

本文介绍了采样率变换原理及法罗滤波器[14]的结构,并根据理论结合实际要求,设计了一种基于法罗结构的采样率变换电路并成功的应用于基带信号发生器中,满足了基带信号发生器对大内插比、高分辨率及高精度的采样率变换[15]的要求,取得较好的效果。

【参考文献】

[1]薛晓男、李增红200MHz宽带基带信号发生器的设计与实现[J].国外电子测量技术,2017年10月第36卷第10期 69~73.

[2]叶淦华、FPGA嵌入式应用系统开发典型实例[M].北京 中国电力出版社.

[3]弗雷德里克·J·哈里斯,王霞等译,通信系统中多采样率信号处理[M].西安:西安交通大学出版社,2008.

[4]陈采莲、于宏毅等.采样率转换中Farrow滤波器实现结构研究[J].信息工程大学学报,2009年9月第10卷第3期 329~332.