用硬件实现SoC系统中的多路事件捕捉器

,,,

(中国兵器工业第214研究所,苏州 215163)

引 言

随着大规模集成电路和SoC系统的发展,SoC系统内部集成多个微处理器核,能够实现大数据计算量和快速准确的实时信息处理。而设计的事件捕捉器可用于记录外部输入高速信号发生的时间以及状态信息,时间基准可由通过内部寄存器配置选择SoC系统内部的多路定时器的某一路定时器提供。设计的多路事件捕捉器可作为一个通用IP模块集成在SoC系统中,借助于SoC系统内部集成的定时器和微处理器核对中断的处理功能,可以实现实时捕获外部事件,可以通过进一步计算实现对信号的测距、测频等。多路事件捕捉器对输入的事件信息信号进行采样,具有高实时性、高精度的特点。

1 多DSP核的SoC系统设计

复位管理电路为SoC片上系统提供复位结构和层次、启动流程和复位结果的电路模块,主要支持的复位类型有冷复位、暖复位、调试复位、软件复位等。

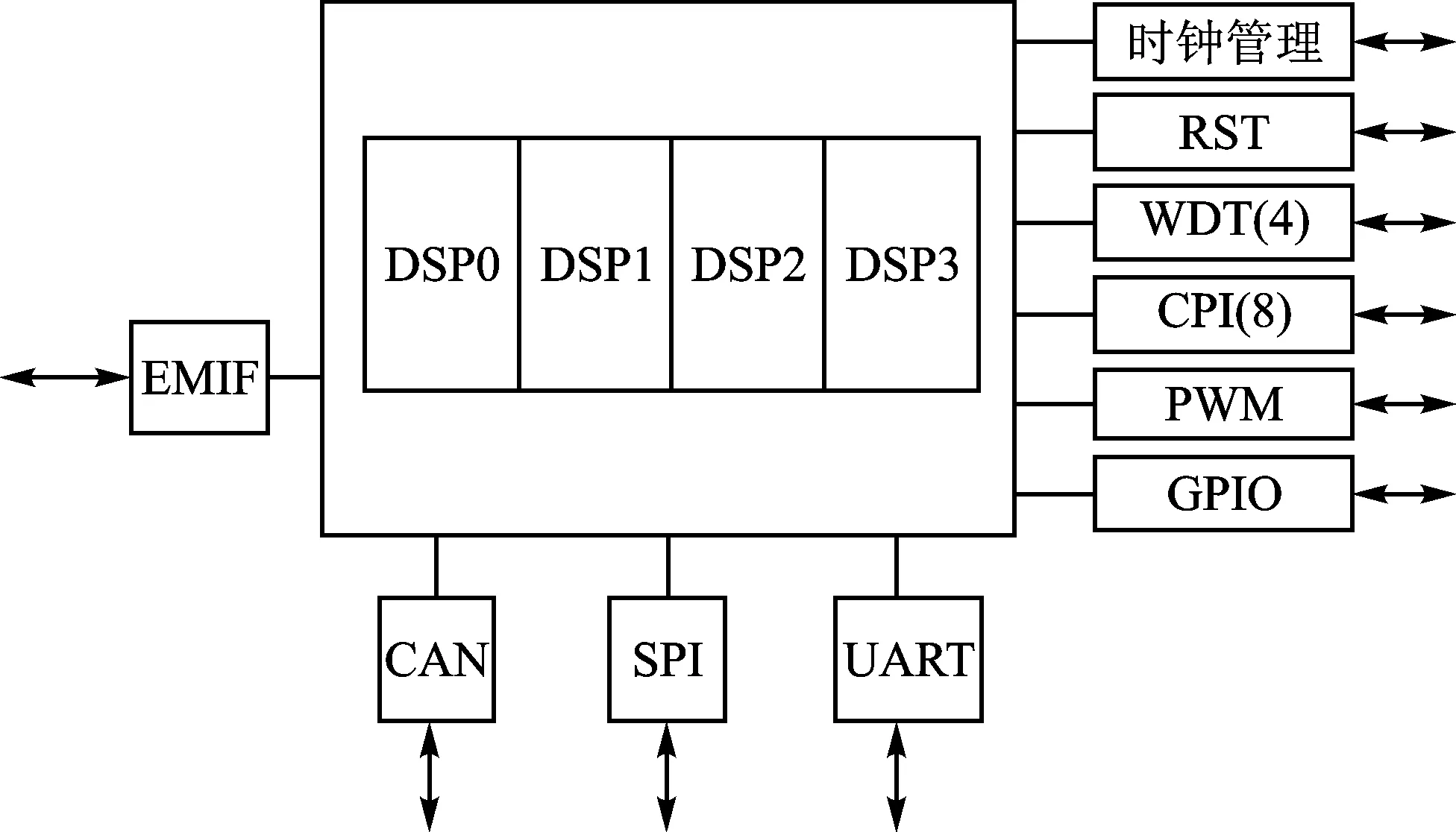

设计的多核SoC系统(结构简图如图1所示)主要包括内嵌的4个DSP微处理器核、AMBA总线和一些外设IP模块等。外设IP模块主要有时钟管理、复位管理(RST)、8路事件捕捉器(CPI)、外设接口(MIF)、GPIO等。

图1 多核SoC系统结构简图

2 多路事件捕捉器电路设计

设计的多路事件捕捉器主要对外部输入的8路高速输入信号进行捕捉,具有高实时性、高精度的特点。对每个外部输入信号捕捉都通过内部寄存器配置有三种捕捉方式可供选择:上升沿捕捉、下降沿捕捉、双沿捕捉。由于设计的多核SoC系统内部每个处理器核内部都有2个定时器工作,多路事件捕捉器通过配置可选择捕捉计时的定时器基准,时间信息基准可从内嵌的4个DSP核中的8路定时器中选择,发生事件捕捉后,会产生相应的中断信号。

2.1 事件捕捉器框图

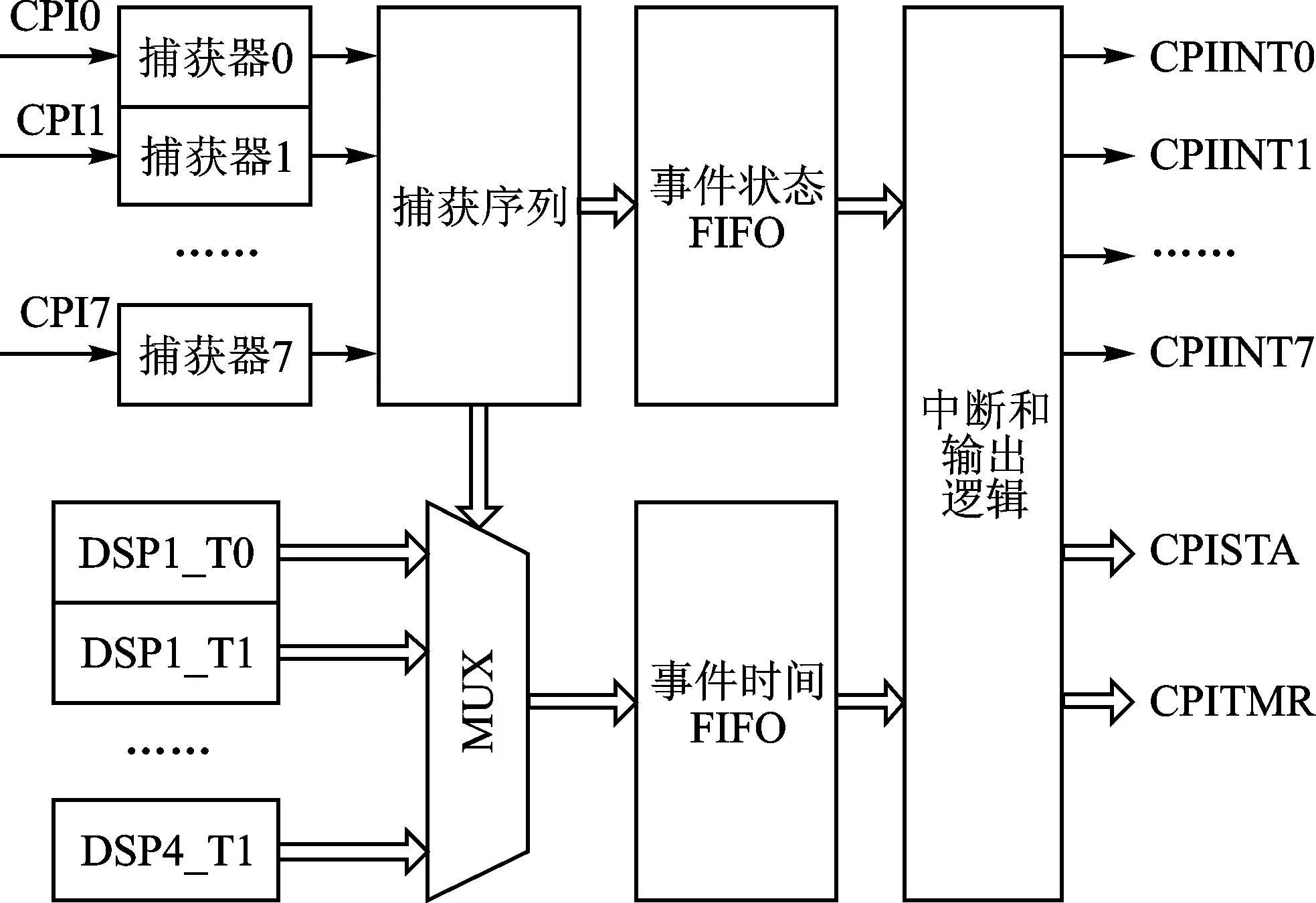

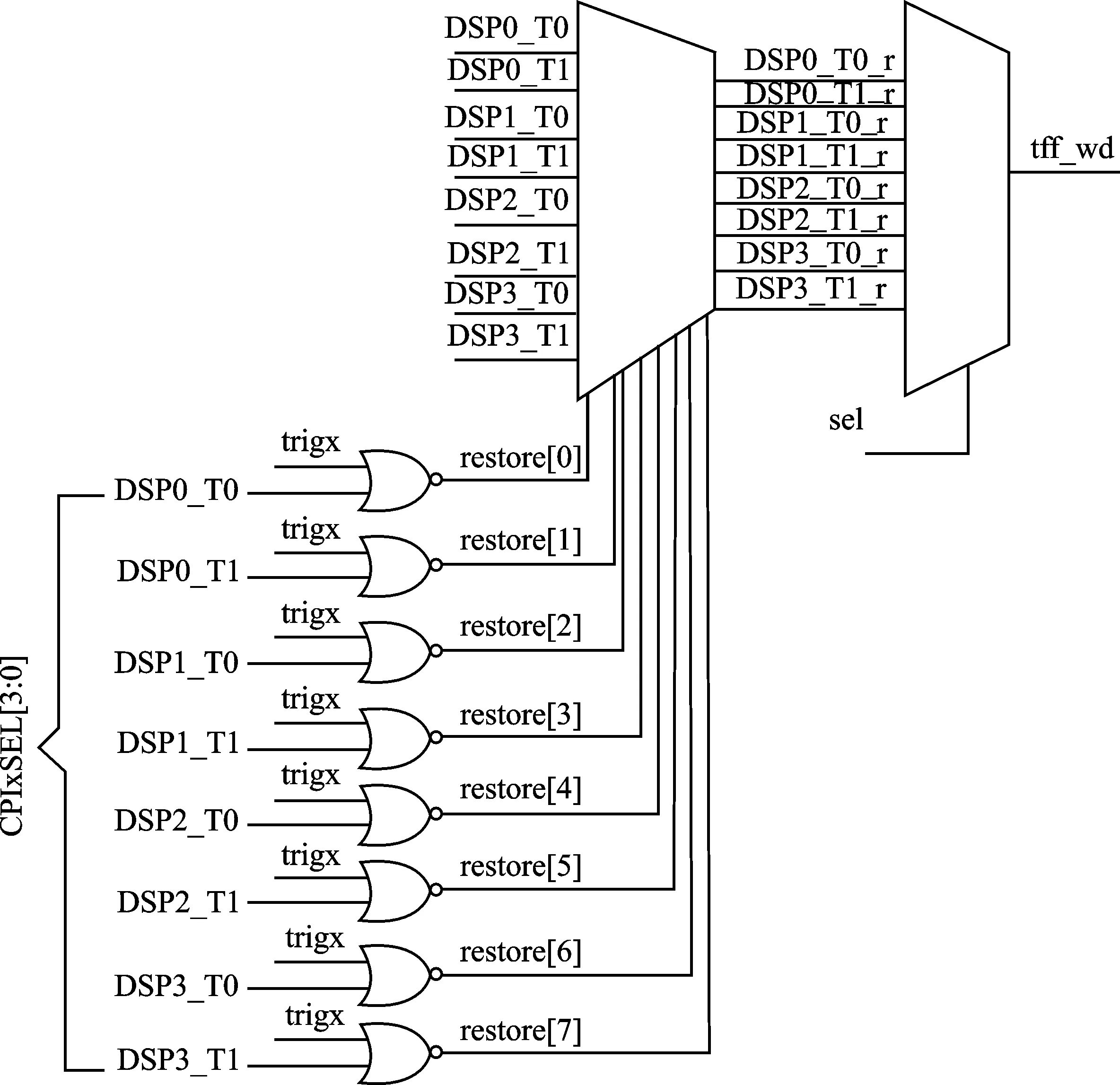

SoC中事件捕获器的具体功能描述如下:事件捕获器主要依赖DSP核中的定时器对输入端口的相关事件进行捕获,并在事件发生时保存相关定时器的当前值,同时产生中断信号。相关事件包括输入端口的上升沿、下降沿、正负双沿,事件发生之后的捕获值包括4个DSP的Timer0或Timer1,通过4个DSP核的事件捕获分配寄存器分别产生中断送给对应的DSP核。捕获模块结构图如图2所示。

图2 8路事件捕捉器结构图

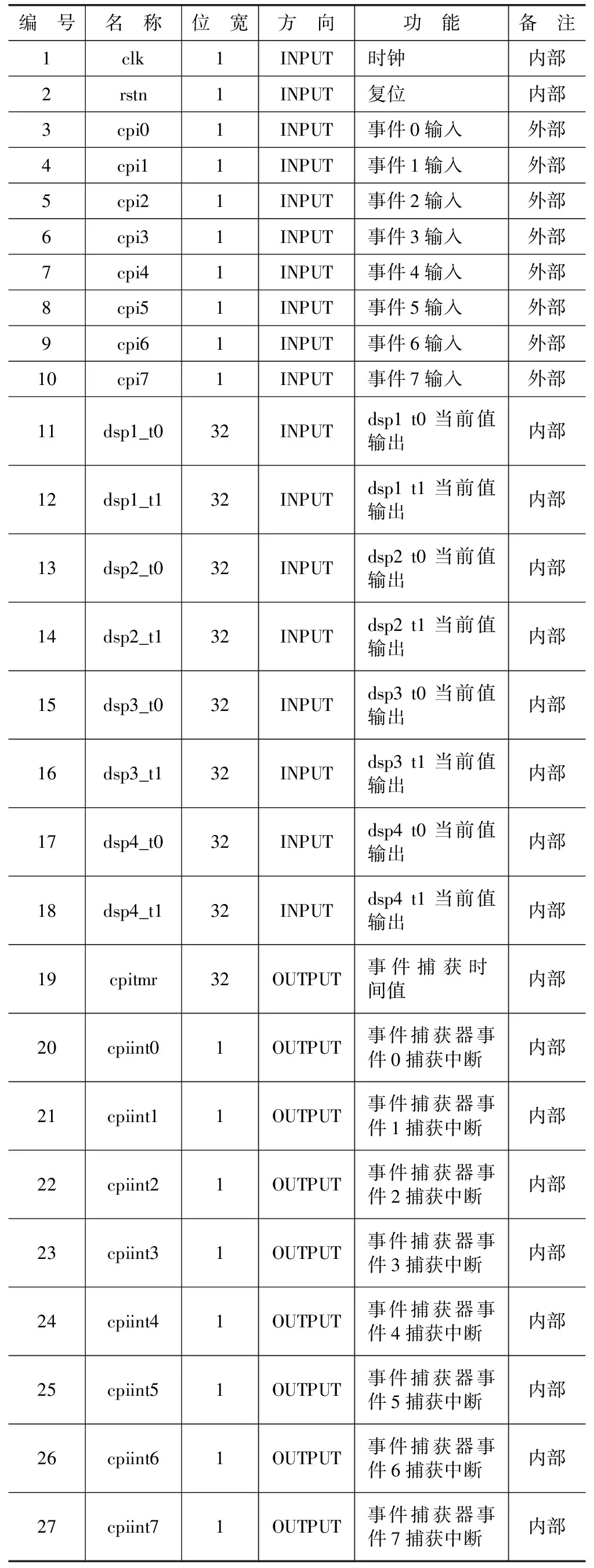

从结构框图中,可以看出多路事件捕捉器电路的输入、输出信号。具体的事件捕捉器信号如表1所列。除了控制事件捕捉器工作的时钟、复位信号外,8路事件捕捉器外部输入端有8路控制信号CPI0~CPI7,对应8路事件输入;而dsp1_t0~dsp4_t1作为8路事件捕捉器的计时时间基准,分别控制CPU的8个定时器;电路输出端有8路对应的捕获中断CPIINT0~CPIINT7。另外还有两个32位寄存器CPISTA和CPITMR,CPISTA是事件捕获状态寄存器,指示8路捕获中断相对应的状态,CPITMR是事件捕获器时间寄存器,用于保存捕获有效沿时刻相应定时器的值。

表1 捕获模块接口信号

当外部有事件输入时,立刻捕获当前的定时器值和捕捉事件沿信息状态后,存储在FIFO中,并产生中断信号。对于同一路事件捕获输入,有效事件输入间隔要求大于事件捕捉器内部工作时钟的8个时钟周期,否则将只响应第一次。另外,对同一个事件来说,事件捕获器储存的事件状态寄存器与时间寄存器是相对应的,事件捕获器每一个状态周期对事件采样一次,要求引脚上事件的高电平和低电平持续时间各不小于一个状态周期。

2.2 多路事件捕捉器内部寄存器

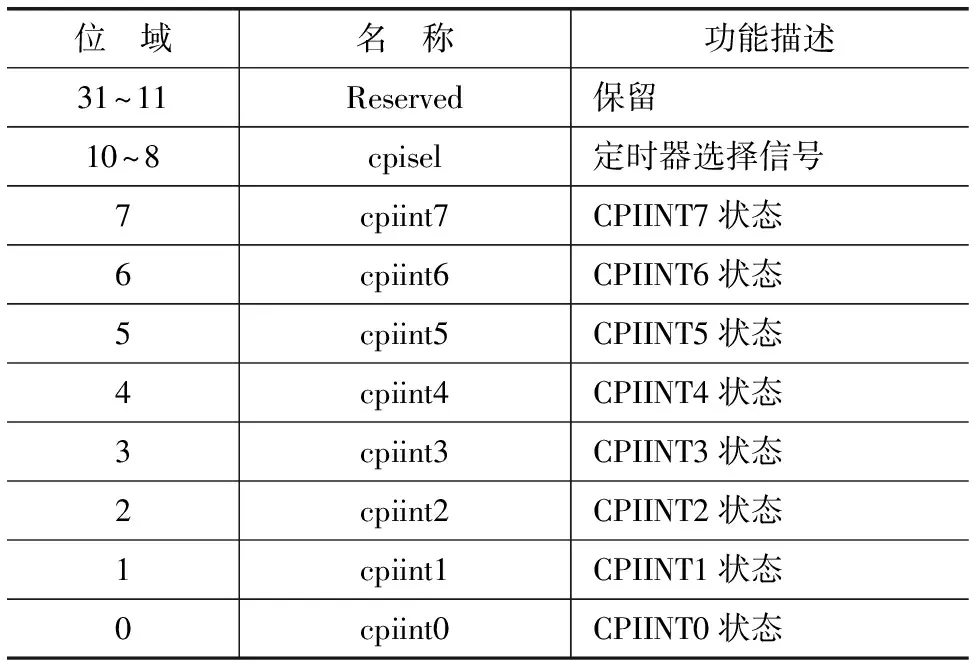

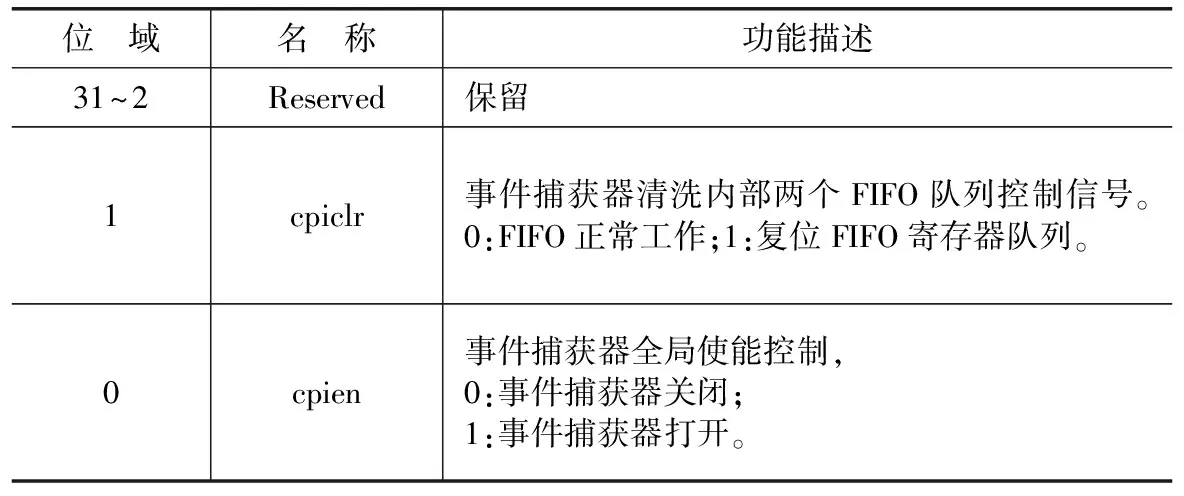

多路事件捕捉器内部主要包括CPISTA事件捕获器状态寄存器、CPICTL事件捕获器全局控制寄存器、CPIxCTL事件0捕获控制寄存器~事件7捕获控制寄存器、 CPITMR事件时间寄存器、CPIFR即FIFO状态寄存器等一些寄存器,通过配置这些寄存器可控制多路事件捕捉器。这些寄存器具体功能特性如表2~表4所列。

表2 CPISTA的功能表

表3 CPICTL的功能表

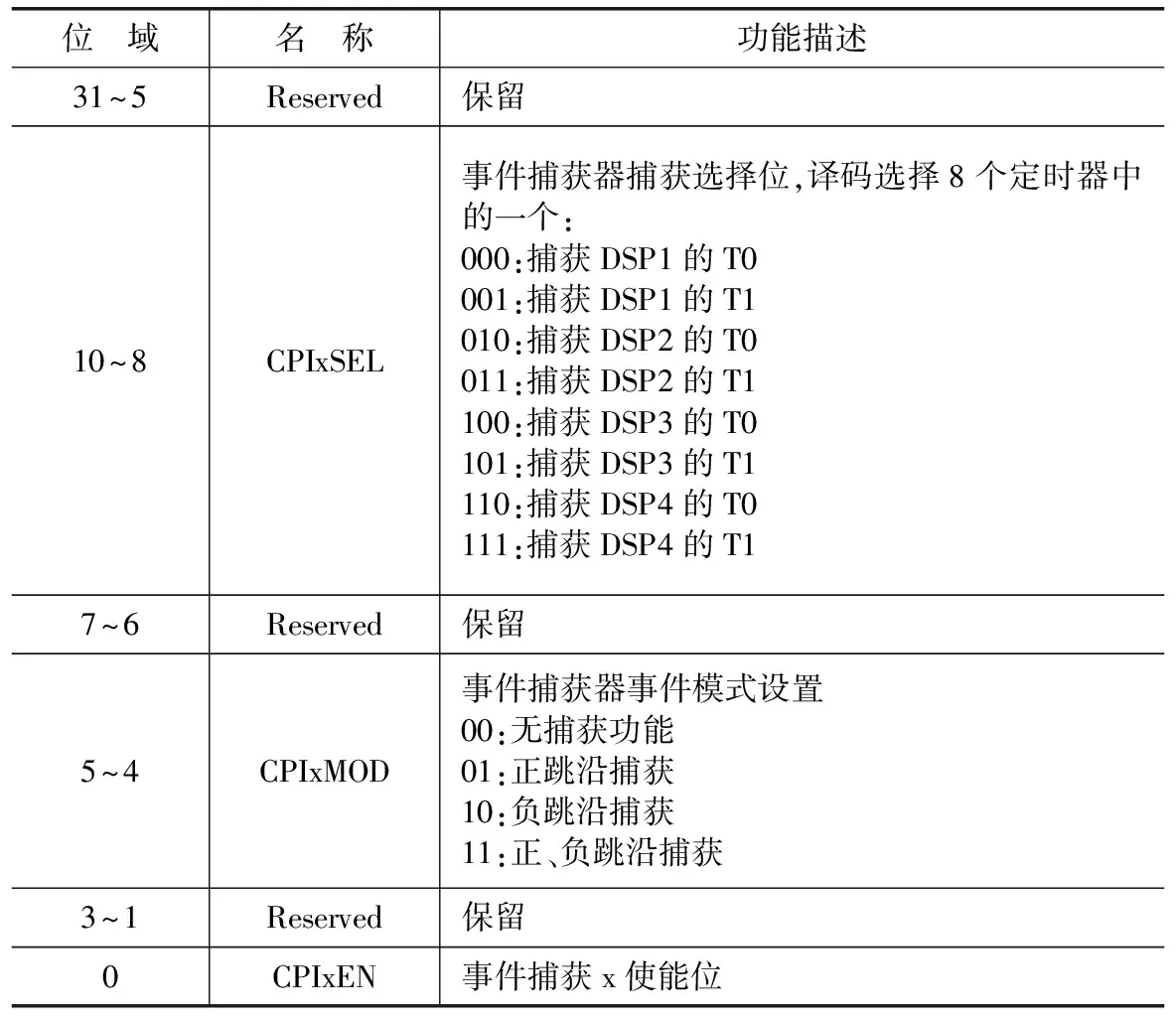

事件捕获器事件x捕获控制寄存器具体指CPI0CTL~CPI7CTL,由于8路捕获控制寄存器结构相同,唯一区别为对应地捕获外部不同8路事件信号。

CPITMR事件捕获器事件时间寄存器用于保存捕获有效沿时刻相应定时器的值。

CPIFR事件捕获器FIFO状态寄存器、事件捕获器内部包含了两个32×32的先进先出队列寄存器FIFO,用于存储事件发生时的信息。其中一个FIFO用于存储事件发生时的时间,另一个FIFO用于记录事件状态。因此事件捕获器在不读取信息的情况下最多可以记录32个事件,若记满FIFO,在读取信息前,进一步发生的事件不再记录。通过FIFO的空满标志,可以证实FIFO中数据的有效性。FIFO空满状态寄存器属性如表5所列。

表4 CPIxCTL的功能表

表5 FIFO空满状态寄存器

2.3 事件捕捉器内部硬件电路设计

设计的多路事件捕捉器内部主要包括事件检测器、时间存储及管理模块、事件状态FIFO模块和事件时间FIFO模块、中断设置等。

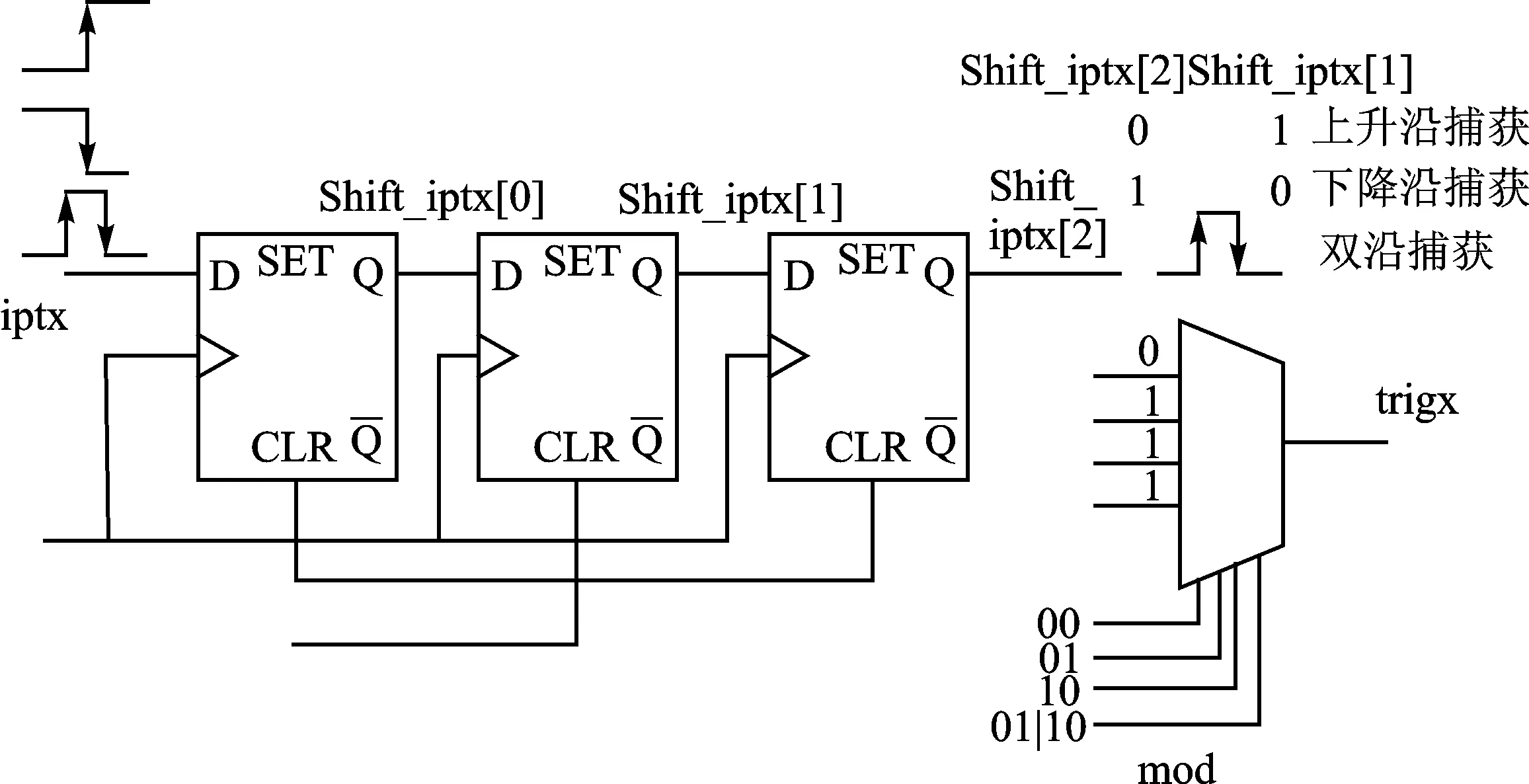

2.3.1 事件检测器模块

事件检测器每个状态周期对外部状态采样,如发生变化,会检测到外部事件。用户可通过配置CPIxCTL事件捕获器,选择对事件的跳变可检测:无捕获功能、正跳沿捕获、负跳沿捕获、正和负跳沿都捕获。产生触发信号传送给其他模块,事件检测器模块如图3所示。

图3 事件检测器模块

2.3.2 时间存储及管理模块

事件检测器检测到事件发生时,根据CPIxSEL选择捕获的Timer,把相应DSP的Timer0或Timer1存储到相应时间寄存器中,时间存储及管理模块如图4所示。

图4 时间存储及管理模块

2.3.3 事件状态FIFO模块和事件时间FIFO模块

事件检测器检测到相应的跳变沿后,把事件发生引起的中断状态及时间信息同时存入事件状态FIFO队列和事件时间FIFO队列。如事件状态寄存器和事件时间寄存器是空的,当读取寄存器信息时,FIFO队列记载的信息被推入寄存器内,并根据读取操作,FIFO队列记载信息一次前进一步。

2.3.4 中断设置

事件捕获器输出8个中断信号,分别对应8路事件输入,8路中断信号参与外设的中断分配,和外设一起最终产生不同的中断信号分别送入4个DSP核。DSP核在收到中断信号之后,通过访问相应寄存器,获知具体的中断信息,来决定后续的操作。

3 仿真与测试

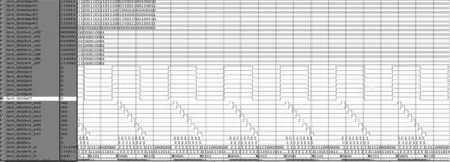

通过仿真激励编写跳变的输入信号CPI0~CPI7在仿真图中对应为ipt0~ipt7,为事件0~事件7输入,设置捕获事件的捕捉模式和配置内部相关的寄存器,使多路事件捕捉器工作。CPIINT0~CPIINT7对应仿真图中的evt_int0~evt_int7,为事件捕获器事件0~事件7产生的中断信号。图5中事件0~事件7八路事件同时发生,读取状态寄存器对应仿真图中的evt_sr及时间寄存器对应图中evt_tr的值,以及中断发生后处理中断的情况。

图5 8路事件捕捉器仿真图

为了测试事件捕捉器电路功能特性,在CCS界面编写DSP程序,配置2路CPI工作,并配置中断服务程序,当发生CPI中断后,处理器核每次进入中断程序,在中断服务程序中,配置GPIO引脚输出发出翻转的方波,并读取CPI事件捕捉器的CPISTA事件捕获器状态寄存器和CPIMR事件捕获器时间寄存器。测试CPI输入信号,并与对应处理器核响应中断后GPIO发出的波形。设置的主要程序如下:

#define REGex1 *((int *)(0x40006010))

//中断状态寄存器,低8位代表CPI0~CPI7的中断状态

#define REGex2 *((int *)(0x40005000))

//事件捕获器状态寄存器地址

#define REGex3 *((int *)(0x40005080))

//事件捕获器时间寄存器地址

*(int *)0x40005004 = 0x00000001;

//CPICTL,Enable CPI

*(int *)0x40005010 = 0x00000011;

//捕获DSP0的T0,捕获正跳沿,使能打开

*(int *)0x40005014 = 0x00000031;

//捕获DSP0的T0,捕获正、负双跳沿,使能打开

中断服务程序如下:

c_int4(void){

IER&=~(1<<4);

reg_data1 = (REGex1 & 0x000000ff);

if(reg_data1 == 0x1){

reg_data2 = REGex2;

reg_data3 = REGex3;

GPVAL&=~(1<<11);

for(Tj=1;Tj<0x00000fff;Tj++);

GPVAL|=1<<11;}

if(reg_data1 == 0x4){

reg_data2 = REGex2;

reg_data3 = REGex3;

GPVAL&=~(1<<13);

for(Tj=1;Tj<0x00000fff;Tj++);

GPVAL|=1<<13;}

IER|=1<<4;

return;}

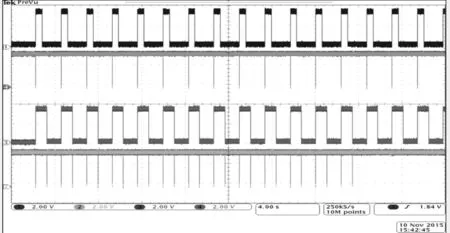

通过示波器进行GPIO波和CPI的输入端口的测试,测试结果如图6所示。图中1通道代表其中1路CPI波输入,内部配置捕捉事件的上升沿变化,4通道代表设置事件捕获上升沿后发出中断,并且DSP进行响应进入中断服务程序,在DSP响应中断时使GPIO11引脚发出方波波形。图中,3通道代表其中另一路CPI输入波,2通道波形是代表设置事件捕获在输入的上升和下降沿双沿时发出中断,并使GPIO13引脚在DSP响应中断时发出方波波形,并且每次进入中断服务程序,DSP都能正确读取事件捕捉器内部的寄存器值,测试结果表明,设计的事件捕捉器能够正常捕捉和响应外部输入事件,并存储事件发生时刻的时间和状态信息,并发出中断信号,在DSP处理器核响应中断信号后,进入下一个事件中断信息的处理。

图6 CPI输入和GPIO发出波形

结 语