1mW多通道12位逐次逼近型(SAR A/D)转换器

刘红兵

(湖南铁道职业技术学院,湖南株洲,412001)

1 体系架构

所提到的SAR ADC由一个MUX、一个采样保持电路、一个比较器、一个数模转换器(DAC)、SAR和控制逻辑电路。MUX由SEL [3:0]信号控制以灵活选择8个通道的输入信号。单位增益缓冲器紧随其后以保证输入信号足够增益和电流驱动力。

1.1 最佳电源电压

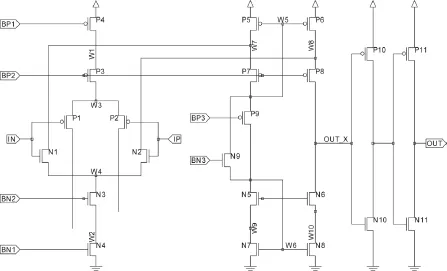

图1 (a)ADC体系结构

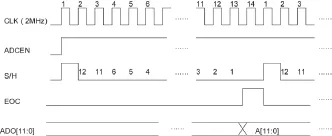

图1 (b)转换波形

对于减小数字电路的功耗来说,降低供电电压是一个有效的策略。然而在噪声、错配、有限开关电阻和失真存在条件下,模拟电路的功耗随着减小的供电电压倾向于增加。合计最宜供电电压出现在800 mV时。但是在加偏压时,堆叠的pMOS和nMOS二级管结构频繁出现。很难保持所有的MOS运行在饱和区域。类似的,模拟传输开关的电导系数在低电压供电时大幅减少并引起信号失真。

考虑到上述所有因数,1.8V电压被选择作为SAR ADC的电源供应以保证线路可靠性并降低ADC的功耗。

1.2 转换计划

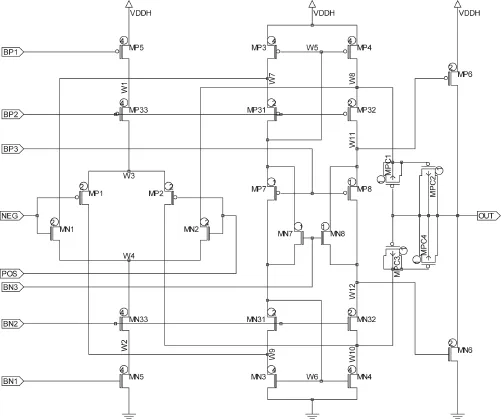

图2 运算放大器

单通道12位ADC的转换计划如1(b)所示。1个转换需要14个时钟周期。ADCEN启用后,ADC开始在第一个时钟周期采样。采样过程中,一个单位增益缓冲器被用来给CHOLD电容器充电。采样后,充电线路关闭,电荷被CHOLD保持以用于转换。ADC在第2时钟周期到第13时钟周期内将模拟信号转换为数字信号。在第14时钟周期内,转换结束(EOC)信号频率很高,转换后的数据被发送到锁存器。系统可以根据EOC信号阅读转换结果。在第15个时钟周期时,ADC进入另外一个转换。

2 电路设计与分析

2.1 运算放大器

为采样到全范围输入信号,一个带有轨到轨输入电压范围的运算放大器(OP)被用来作为单位增益缓冲器。其能通过配置一个N-channel和一个P-channel的平行差分输入对来取得。一个带有AB输出级别的折叠级联放大器紧随其后以得到高增益和大电流驱动力。米勒补偿在折叠级联放大器和AB类输出级之间被采用以保持足够的相位裕度。

2.2 比较器

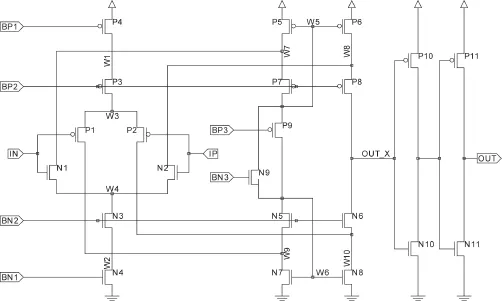

对于逐次逼近型ADC的设计,高性能的比较器是其中一个关键组件。比较器对将LSB电压附近的微小输入解析为完全的数字值负责。在这一角色中其有着巨大的增益、速度和敏感度的要求。比较器由三级放大器组成。为维持ADC一个高的输入信号摆幅范围,一个轨对轨运算放大器被用在比较器的第一级。一个对称折叠级联放大器被用在第二级来保证比较器的高增益(>74 dB)和高速度(< 100 ns)。比较器的第三级是两个用来将模拟波性整流成数字信号的逆变器。该结构有着更高的增益、更低的设计难度,并且提高了ADC的性能。

2.3 DAC电路

从简单到复杂的,存在有多种多样的DAC体系架构,每一种均有其优点。电压分压、电流导引以至于电荷缩比均能用来将数字值描绘为模拟量。其必须仔细筛选因为采样率和分辨率受限于在反馈环中DAC的采样率和分辨率。一个带有串联电阻插入的电压分压电路被使用。 尽在整个电压分压中多晶硅电阻器才被使用。该结构有很好的匹配特性并能保证线性关系。即使是多晶硅电阻器在制造时电阻改变,非线性问题也不会出现。同时,带有串联电阻插入的DAC非常适合低电压和高分辨率应用。

3 实现与结果

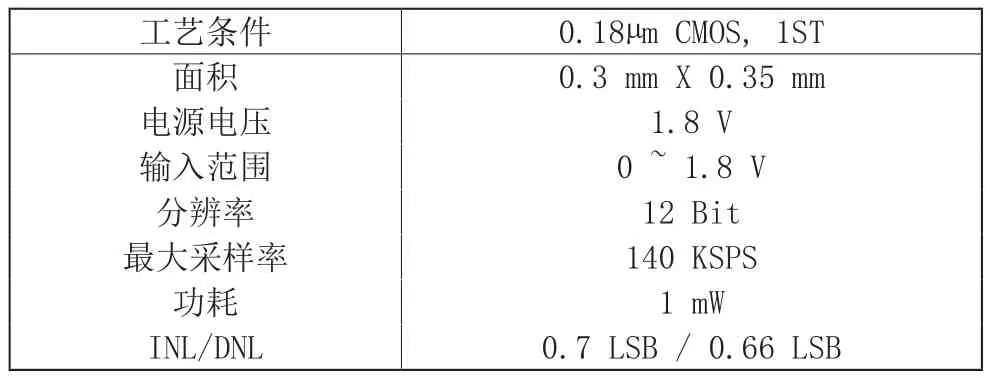

针对所提到的SAR ADC的功能及规范要求,严格的仿真测试已由HSPICE完成。ADC按照0.18 µm 2P4M CMOS工艺制造。有效电路尺寸为0.3 mm×0.35 mm。所制造的ADC性能如表1所示。可见其有着良好的性能表现并且适合低压和低成本设备。

图3 比较器原理图

表1 A/D转换器性能参数

4 结论

用第一次0.18μm 2P4M CMOS工艺制造的8通道12位SAR A/D转换器(ADC)已如上所示。ADC占有面积为0.3 mm×0.35 mm。其最大采样率为140KSPS。低电压显著减小了ADC的总功耗。串联电阻器的插入杠杆性的使其获得了良好的匹配特性和线性关系,其适用于低电压低成本应用。