基于Artix?7FPGA的异步高速串行通信IP设计

王蕾 韩立峰

摘 要: 设计一种基于Artix?7 FPGA的异步高速串行通信IP核,包含协议解析和抗干扰设计、跨时钟域缓冲区设计、用户接口和物理层接口设计,实现最小硬件系统。该IP核可结合高速串口驱动芯片简单对接至主流处理器,如DSP,ARM,PowerPC等,以扩展处理器的异步串行通信接口数量和通信速率。其中,通信速率最高可至30 Mb/s,扩展数量视FPGA内部资源而定,理论上无上限。在机载和地面设备中可广泛应用。

关键词: 高速率通信; 异步串行通信; DSP; ARM; Artix?7; 处理器

中图分类号: TN919.6?34 文献标识码: A 文章编号: 1004?373X(2018)19?0006?05

Abstract: An asynchronous high?speed serial communication IP core based on Artix?7 FPGA was designed, for which the protocol analysis, anti?jamming capability, clock crossing domain buffer, user interface and physical layer interface are designed to realize the minimum hardware system. The IP core combined with high?speed serial driving chip can simply connect to the mainstream processors such as DSP, ARM and PowerPC to increase the extension quantity of asynchronous serial communication interface and improve the communication rate. The maximum communication rate can reach up to 30 Mb/s, and the extension quantity is determined by the internal resource of FPGA and has no upper limit theoretically. This IP core can be widely used in airborne and ground equipments.

Keywords: high?speed communication; asynchronous serial communication; DSP; ARM; Artix?7; processor

0 引 言

通用异步收发器(Universal Asynchronous Receiver/Transmitter,UART)包括RS 232,RS 499,RS 423,RS 422和RS 485等总线标准规范。UART协议作为一种串行通信协议,广泛应用于通信、语音、图像、仪器仪表、军事域等各种场合,具有电路结构可靠、通信接口简单、传输距离远等特点。随着硬件处理能力的提升和通信技术的快速发展,无线信道上的数据速率和带宽也稳步提升。简单的UART协议在集成度较高的处理器标配外设平台上通信速率较低,不能满足高速率数据接口和多源接入的要求。

本文设计的异步高速串行通信IP继承UART传统优点并进行改进设计。基于Xilinx公司的Artix?7 FPGA芯片进行实现,并成功应用于某型地空通信电台数据输入输出接口。按照RS 422电平标准通过硬件平台测试后,通信距离可达10 m,通信速率可达30 Mb/s。异步高速串行通信IP具有高可靠通信速率、容量可扩展的数据缓冲区、便于多目例化实现等优点,在军事装备领域具有广泛的应用前景。

1 软件协议

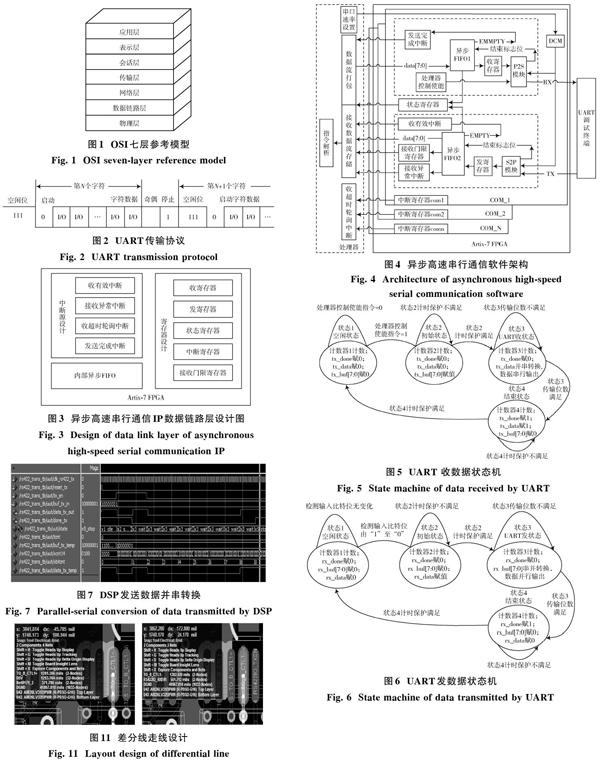

开放式系统互连参考模型(OSI)描述了计算机网络通信的基本框架,其采用分层的结构体系,模型如图1所示。它作为一个概念性框架规定了各层次位置和提供的服务,协调和组织各层协议的制定和执行,满足开放系统环境互联和应用可移植性[1]。通信协议设计时可参考OSI模型,根据系统信息交换问题分解到一系列可控的软硬件模块层中,各层进行独立修改和功能扩充。本文设计的异步高速串行通信IP根据应用场景,需要应用物理层和数据链路层协同通信,物理层利用硬件传输介质为数据链路层提供物理连接。数据链路层负责将数据分帧,处理流控制。

1.1 物理层设计

异步高速串行通信IP采用UART起止式异步协议。基本的UART通信需要4条信号线: 接收端RXD±和发送端TXD±。UART数据发送和接收的帧格式: 第一位为起始位,置“0”,表示通信开始; 最后一位为停止位,置“1”,表示通信结束。每一个字符的前面都有一位起始位:低电平,逻辑值“0”。字符本身由8 bit数据位组成,字符后面是一位校验位,最后一位是停止位高电平,逻辑值“1”。停止位和空闲位都规定为高电平,这样就保证起始位开始处一定有一个下降沿。传输时,数据的低位在前,高位在后。字符之间没有固定的时间间隔要求[2]。其格式如图2所示。协议分析:异步通信按字符传输,每传输一个字符,就用起始位通知收方,以此来重新核对收发双方同步,从而避免由于接收设备和发送设备之间的时钟频率偏差累积而导致的错位,加之字符间的空闲位也为这种偏差提供一种缓冲,所以起止式异步协议具有较高的传输可靠性[3]。

1.2 数据链路层设计

本文设计的异步高速串行通信IP采用中断源与外部处理器进行通信;内部设计寄存器用作状态和数据存储;数据收发时使用异步FIFO,保证外部处理器和Artix?7 FPGA之间实现跨时钟域正常通信,具体数据链路层设计如图3所示。

其中,中断源设计如下:

处理器收超时轮询中断:在多串口多中断情况下处理器内部对每个中断源轮询查找,按优先级别控制执行中断执行源;处理器收有效中断:通知处理器接收数据;处理器接收异常中断:对中断异常情况处理,保证系统接收稳健性;处理器发送完成中断:通知处理器整包解析发送完成,可进入下一次发送状态。

寄存器设计如下:

UART发寄存器:存储需要串并转换的字节数据;UART收寄存器:存储需要并串转换的字节数据;UART状态寄存器:将异步FIFO状态的输出按位组合为状态寄存器发送至处理器进行状态判断;中断寄存器:高低电平转换控制具体串口中断发生;处理器接收门限寄存器:异步FIFO可读门限值,保证数据转换完整,可正确地按序读取,提高系统运行时间[4]。

FIFO存储深度设计:FIFO存储深度根据系统需求设定,深度大会占用不必要的FPGA资源,深度小不能提供大容量的数据转存[5]。

2 FPGA IP逻辑设计实现

2.1 软件模块

异步高速串行通信软件架构如图4所示。串行通信传输系统中多目串口例化时,设置多个中断寄存器[1~n]输出,控制外部处理器响应对应串口[1~n]中断进程。处理器收超时轮询中断:在中断源多的情况下,处理器内部对每个中断源轮询查找,根据中断优先级别高低执行中断进程,若等待超时即进入下个中断源。将2个异步FIFO输出的FULL,GROG_FULL和EMPTY,共计6个信号按位组合为状态寄存器,传输给处理器进行状态判断执行。

数据并串转换流程:处理器内部完成数据打包并写入异步FIFO1中;处理器发送控制使能信号至P2S模块,准备并串转换;根据先进先出原则按字节存入UART收寄存器中,输出至并串转换P2S模块;P2S模块按比特位输出至UART收通道,一个字节转换完成。并串转换结束标志位和异步FIFO1的EMPTY输出同时作用控制读取速率,直至完成整个FIFO1的读取,一包数据解析完成,执行发送完成中断信号。

数据串并转换流程:UART发通道输出至S2P模块;S2P模块完成串并转换按字节输出存储在UART发寄存器中。串并转换结束标志位控制写入FIFO2的速率。接收门限寄存器中门限值的设定控制处理器读取FIFO2的读取起始时机。异步FIFO2的HALF_FULL有效输出,FPGA发出收有效中断,通知处理器进入执行接收状态。处理器根据先入先出原则按字节读取FIFO2中的数据。

2.2 高速波特率的实现

针对数据传输需求,将串口传输速率设为可调模式。包括三档速率:115.2 Kb/s,1.44 Kb/s,10 Mb/s。在DSP中控制串口速率,FPGA中配置为相应的DCM核进行分频。用不同的波特率控制串口收发。串口调试终端按协议发送、接收数据,实现通信交互[6]。

2.3 UART数据转换

2.3.1 UART 收数据状态机设计

UART 收状态工作流程如图5所示,共计4个状态。

状态1:空闲状态。状态机在收状态前或完成后处于空闲状态。计数器1负责计数等待;转换结束标志(tx_done)赋0;待发送串行数据(tx_data)赋0;待转换并行数据(tx_buf[7:0])赋0。处理器发出控制使能指令控制状态跳转。

状态2:初始化状态。tx_buf按设计的FIFO1读取速率赋初值等待转换。计数器2计时保护确保数据正确保存,作为状态跳转信号。

状态3:UART收状态。根据计数器3计数做并串转换,tx_data按UART时钟按位输出。计数器3计时保护满足8位比特位传输进入状态跳转。

状态4:结束状态。计数器4负责计数等待;完成一个并串转换流程,状态机复位。状态4跳转回状态1,完成一次状态机工作。

2.3.2 UART发数据状态机设计

UART 发状态工作流程如图6所示,共计4个状态。

状态1:空闲状态。状态机在发状态前或完成后处于空闲状态。计数器1负责计数等待;转换结束标志(rx_done)赋0;待转换串行数据(rx_data)赋0; 待发送并行数據(rx_buf[7:0])赋0。检测输入比特位的电平高低跳变情况作为状态跳转信号。

状态2:初始化状态。rx_data根据UART发数据速率依次保存比特位,计数器2计时保护确保数据正确保存,作为状态跳转信号。

状态3:UART发状态。根据计数器3计数做串并转换,rx_buf按字节输出。计数器3计时保护满足8位比特位转换完成进入状态跳转。

状态4:结束状态。计数器4负责计数等待;完成一个串并转换流程后状态机复位。状态4跳转回状态1,完成一次状态机工作。

2.4 仿真测试结果

本文系统在ModelSim 10.1环境中进行验证。模拟DSP发送数据并串转换,仿真结果如图7所示。当buf_tx_in 输入为“10000001”时,data_tx_out按时钟输出“0,1,0,0,0,0,0,0,1,1”,done_tx在转换结束后输出“1”。

模拟串口发送数据串并转换,仿真结果如图8所示。当data_rx_in按时钟输入“0,1,1,0,1,1,1,0,1,1”,buf_ rx_out输入为“0xBB”时,done_rx在转换结束后输出“1”。

3 硬件系统逻辑

3.1 硬件系统架构

高速串口传输系统硬件结构系统硬件架构如图9所示。Artix?7 FPGA使用通用输入输出接口与处理器的EMIFA总线接口连接,包含片选线、地址总线、数据总线、读写使能线等。寄存器、各种交互信息和高速通信数据都通过EMIFA总线传输[7]。中断源通过通用输入输出接口与处理器GPIO口连接,管脚电平跳变控制中断是否发生。处理器实现数据组包、解析、纠错、指令控制等[8]。通过芯片使能线和4路数据线将Artix?7 FPGA与高速串口驱动芯片AM26LV31E,AM26LV32E连接。AM26LV31E支持4路RS 422数据发送单端转差分,最高转换速率为为32 MHz,4路共用一组使能控制线。AM26LV32E支持4路RS 422数据接收差分转单端,最高转换速率为32 MHz,4路共用一组使能控制线。系统使用RS 422作为平衡通信接口,经过9针D型串行接口通过串口转换器合并连接至PC端机,并根据需求扩展串口线路数量以实现10 Mb/s的传输速率[9]。

3.2 差分串行总线设计

RS 422差模传输抗干扰能力强,理论传输距离为1 200 m。终端匹配采用终极电阻方法,在总线电缆远端并接电阻100 Ω匹配电缆阻抗特性[7]。本文使用的高速驱动芯片电路设计如图10所示。AM26LV31芯片差分输出阻抗匹配100 Ω,AM26LV32芯片差分输入阻抗4~17 kΩ。

在实现高速数据高可靠性传输时,使用差分串行抵消通信传输时的外部干扰。差分总线作为一个整体,外部干扰叠加在两条差分线上后相抵消。通信电路设计完成后进行PCB设计布图时,差分输入输出应考虑差分线走线等长。对PCB布图中AM26LV31E第二通道差分输出长度进行测量,如图11所示:TO_B_CTRL1+长度为1 281.356 mils,TO_B_CTRL1-长度为1 282.93 mils,设计长度满足走线需求。

3.3 硬件测试结果

PC端机中设有串口测试终端[10]。测试软件使用C++语言编程,终端界面负责下达、数据收发检测、实时状态上报、误码率判断等工作。测试时将发送波特率设定为10 Mb/s,验证串口传输误码率,重复次数为10 000次时,误码率为0,验证了该通信方法的可靠性。

4 结 语

本文设计的异步高速串行通信IP基于Xilinx公司的Artix?7实现,具有可编程性以及面向DSP、存储器和连接功能支持的集成式模块的合理组合,是Xilinx公司的成熟产品。系统应用在任务处理机硬件平台上,经过实际测试达到10 Mb/s通信速率,满足实时性要求高、数据量大的数字通信系统通信需求,硬件扩展性强,可靠性高,调试直观,可广泛应用于机载和地面设备中。

参考文献

[1] 何亚兰,周刘纪.基于FPGA+DSP的调频电台传输系统[J].单片机与嵌入式系统应用,2013(10):1?4.

HE Yalan, ZHOU Liuji. FM radio transmission system based on FPGA+DSP platform [J]. Application of SCM and embedded system, 2013(10): 1?4.

[2] 田佳,王一平.基于FPGA的带CRC校验的异步串口通信[J].现代电子技术,2010,33(20):5?7.

TIAN Jia, WANG Yiping. Asynchronous serial port communication with CRC verification based on FPGA [J]. Modern electronics technique, 2016, 33(20): 5?7.

[3] 蔡艳辉,胡锐,程鹏飞,等.一种基于FPGA+DSP的北斗兼容型高精度接收机系统设计[J].导航定位学报,2013(2):1?6.

CAI Yanhui, HU Rui, CHENG Pengfei, et al. Design of a Beidou compatible high precision receiver based on FPGA+DSP [J]. Journal of navigation and positioning, 2013(2): 1?6.

[4] 李莹,贾彬.一种基于状态机的串口通信协议的设计与实现[J].电子设计工程,2012,20(7):100?103.

LI Ying, JIA Bin. A serial port communication protocol based on state machine and its implementation [J]. Electronic design engineering, 2012, 20(7): 100?103.

[5] 李伟.基于FPGA的多串口通信设计与实现[J].数字技术与应用,2015(2):174?175.

LI Wei. Design and implementation of multi?serial port communication based on FPGA [J]. Digital technology and applications, 2015(2): 174?175.

[6] 胡焱.基于FPGA+DSP 的数字中频收发机的设计[J].现代电子技术,2016,39(15):78?80.

HU Yan. Design of digital medium frequency transmitter based on FPGA+DSP [J]. Modern electronics technique, 2016, 39(15): 78?80.

[7] 王冲,汪宝祥.基于FPGA 的串行通讯接口设计[J].微处理机,2016,37(3):73?76.

WANG Chong, WANG Baoxiang. Design of serial communication interface based on FPGA [J]. Microprocessors, 2016, 37(3): 73?76.

[8] 王斌,张林,邓军,等.一种基于高速串口通信的高效数据处理方法[J].自动化技术与应用,2016,35(6):57?60.

WANG Bin, ZHANG Lin, DENG Jun, et al. A high efficiency data processing method based on high?speed serial port communication [J]. Technology of automation and applications, 2016, 35(6): 57?60.

[9] 桂江华,邵健,潘邈.一种高可靠串行通信协议[J].电子与封装,2016,16(2):40?43.

GUI Jianghua, SHAO Jian, PAN Miao. A high reliable serial communication protocol [J]. Electronics and packaging, 2016, 16(2): 40?43.

[10] 丁毅,赵笑龙,丰伟.基于在线调试的串口通信协议测试方法[J].航空电子技术,2016,47(2):30?33.

DING Yi, ZHAO Xiaolong, FENG Wei. Test method of serial port communication protocol based on online debugging [J]. Aero?electronic technology, 2016, 47(2): 30?33.