AI架构创新和高端芯片发展

摘要:在“2017中国集成电路产业促进大会”上,清华大学魏少军教授就架构创新和高端芯片发展做了相关报告。根据魏少军教授会上报告整理,已获作者授权。关键词:集成电路;架构创新;高端芯片

0 引言

随着近年来人工智能(AI)的兴起,Al芯片的需求量越来越大,性能要求越来越高。而Al运算量很大,这就意味着其需要有足够高的运算速度,预计其运算速度需要达到每秒几千亿次。如果从能量效率角度分析,大概要做到每瓦1万亿次。因此,国内做Al芯片的企业大部分还在用专用芯片在做。采用专用集成电路的问题在于,当网络一旦变化,专用集成电路做成的芯片将无法应对再应用。这就为可编程器件带来了机遇。

1 FPGA难以达到Al的要求

可编程器件的一个优点是可以通过软件的方式来改变芯片的功能,从而适应各种不同功能的应用。最终提升销量,从而分摊产品的成本。

而现在较为常用的可编程器件——FPGA仍然存在诸多问题,还难以达到Al的速率及通过软件改变芯片功能的需求。

1) FPGA的配置信息量很大,多达数十兆字节,因而所需配置时间也很长,大概要几十毫秒,甚至几秒。

2)能量效率低。FPGA面板利用率很低,大概只有5%用来进行计算,95%用来配置信息。正因为其95%是用来配置用的,还要耗电,因而能量效率很低。

3)另外,由于各方面原因,FPGA往往需要最先进的工艺,同时还必须要有电路设计的支持,这也带来了高设计成本。

FPGA存在的问题总结起来包含十点:高细密度、配置信息量大、配置时间长、需要断电静态配置、没有逻辑复用能力、面积利用率低、能量效率低、工艺要求较高、对开发人员知识储备要求高、价格贵,具体如表1所示。

2 理想的硬件结构

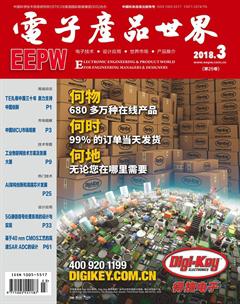

如图1所示系统架构为设想的理想系统架构。其中左边为软件(应用),如果不考虑硬件的代价,左边有怎样的操作,右边就要对应怎样的硬件,左边和右边的拓扑结构是完全一致的。从计算上来看,这样的结构一定是效率最高的。

在这样的架构中,软件可以无穷大,例如写一个循环语句,可以一直循环下去,但是硬件不论多大都是有边界的,这就需要将软件分块搬到硬件上按顺序执行。这样搬的过程中,右边的硬件架构其实是在不断变化的,我们称之为架构和功能可以动态按照软件要求实时改变。

3 软件执行方式

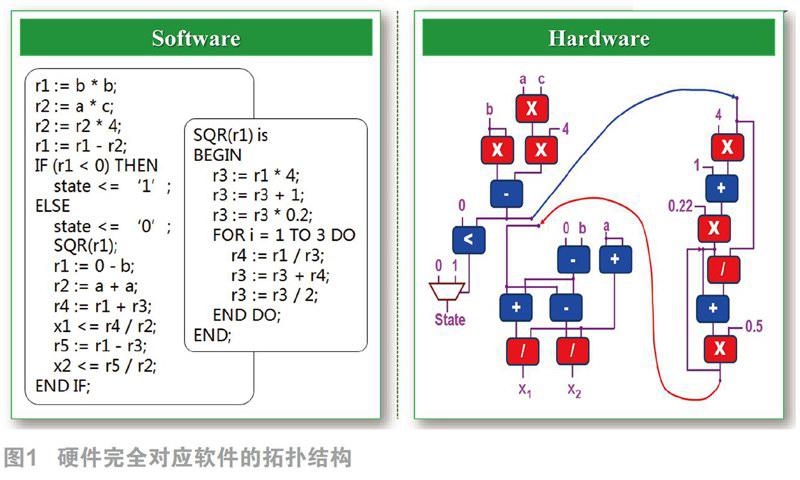

软件信息主要可以分为两类:计算信息和控制信息。如果我们将软件写成如图2所示形式,中间对应的是控制信息,用来控制程序执行流程,右边对应的是计算信息。如果将软件中的计算信息和控制信息分开,就可以找到相应的架构,包括控制单元和数据通道。

数据通道对应的是阵列,控制单元对应的是有限状态机,不论是阵列,还是有限状态机,都是完全可编程的。从而实现不同软件部分按要求搬进去执行,具体地,将分块软件按照他们的依赖关系送到数据通道中,通过数据通道配置其中阵列,并执行。

而在软件配置和执行过程中,如果整个系统是按照C语言编写的,通过编译器会产生一系列的控制流,最后在硬件芯片上运行。这种架构的独特之处在于采用控制流、数据流和配置流代替之前的指令集。

4 软件定义芯片架构

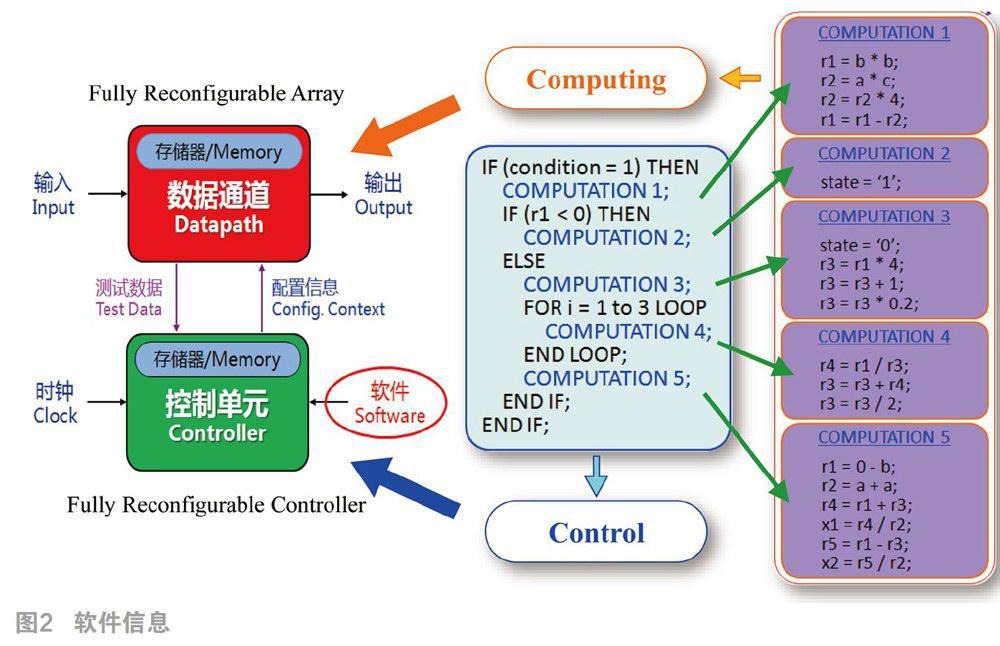

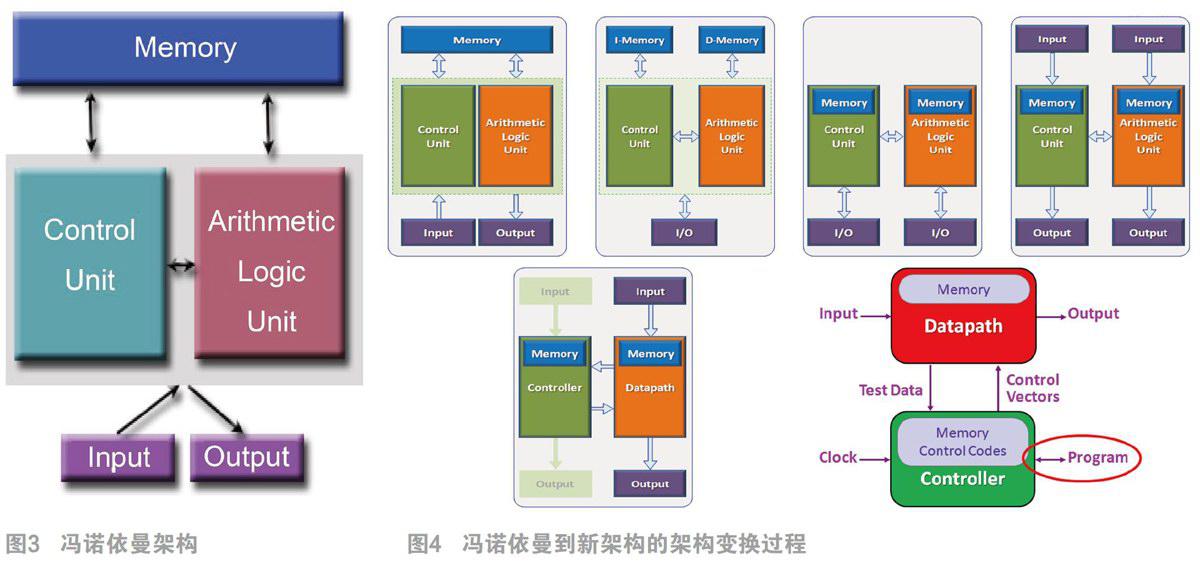

如图3所示为基本冯诺依曼架构,包括控制单元、算数逻辑单元、存储器、输入和输出五个基本模块。首先将存储器分为两块,即l-Memory和D-Memory,分别对应指令和数据,这就是HUS结构。Input和Output合并,变成I/O:然后将存储器分别放入控制单元和算数逻辑单元,再将I/O分为两部分,一部分和控制单元相关,另一部分和数据逻輯单元相关:再将I/O分开,输入放在上边,输出放在下边:然后将这个结构逆时针旋转90度,得到的架构即为软件定义芯片架构(以下简称“新架构”)。冯诺依曼到新架构的架构变换过程如图4所示。

因此,该架构实际上是从经典的冯诺依曼架构变换得来。但是它和冯诺依曼体系结构又有所不同,即它不再使用指令集,而直接采用信息流,这也是两者间的本质区别。

另外,与传统架构比较,新架构还具有以下特点:

1)传统架构都是冯诺依曼等效架构,是刚性的:而功能化的硬件架构,是应用性的。

2)传统架构是应用去适应计算的架构,新架构是计算架构适应应用。即,传统架构是软件适用硬件,而新架构是硬件适用软件。

3)在传统架构中,一个任务一个软件;而在新架构中,一个任务会有多个等效软件。

4)在传统架构中,硬件和软件是不变的;在新架构中,硬件和软件是选择性动态改变的。

5)传统架构中,为了节省硬件资源,大量复用:新的架构中是使用冗余方式实现的。

5 计算模式的改善

硬件配置时间和执行时间对于硬件架构来说是一个必须考虑的问题。当硬件配置时间多于执行时间时,显然是不经济,不合理的。而新架构在刚开始工作的时候,其中将近90%的时间都用来配置硬件,而只有10%的时间是用来进行计算和执行的。显然这样的架构需要进一步改善,主要通过以下两种方式进行改善:

1)首先将配置信息减少。通过采用诸如配置子图的方式、结构化组织等一系列方法,最终将配置信息减少将近80%。

2)数据不断写的过程也会耗费大量时间。很多数据写进去并不需要翻译,采用频次优先方法,用的最多的先写入,频次少的就不写入或少写入,这样可以将整个配置时间缩短12倍。

其计算模式变化如图5所示。传统架构是串行计算模式,而新架构则是交叉的并行计算模式。经过努力后,我们可以使一个阵列的计算时间占到整个运行时间的90%,而只有10%的时间用来实现配置。这样将多数时间用来计算的架构才是更合理的架构。

6 针对不规则阵列的架构改善

在上述例子中给出的是规则的运算阵列,而实际上的运算阵列是不规则的,有不同的密度,中间可能出现迭代和循环,分支长短可能不一。在规则的阵列上运行不规则的运算显然会出现效率的高低。

阵列是硬性放大的,我们无法改变硬件,因而只能改变软件,具体通过以下方法:

1)把软件并行化处理。特别是控制性的软件并行化处理,甚至在时空上也作相应的变换,让其在时空上也能并行化。

2)改变电源的供电情况。例如,在阵列中并非所有运算单元同时存在,这样就需要一部分打开,一部分关掉,由于完全关掉后重新启动需要很长时间,会降低性能,因而要使其部分处于浅度睡眠,有的进入深度睡眠,有的进入浅度睡眠,从而恢复的时候,节省启动时间。

3)将软件映射到不同的硬件上。不同映射形式会带来不同的运算结果,这里给出两种不同的应对方法,如图6所示。a的数据走中间,可以通过route(计算资源)或者buffe(缓冲层)来传输,这两种传输方式哪种更适合新架构,还需要建立一整套模型,通过性能的模型实现各种仿生变换,最终确定最优的执行时间。如果建立面向性能的模型,可以使得性能提升20%:而如果建立面向功耗的模型,可以使功耗降低26%。但是,现在还无法建立两种模型的统一方案。

7 编程语言

全新的架构需要考虑全新的编程范式。传统硬件用C语言编程:而出现GPU后,随之而产生的是OpenCL编程语言;出现FPGA后,又有verilog、VHDL编程语言。而新架构软件的编程语言是基于传统编程语言,而基于原有的编程语言,语言不变、硬件不变的情况下,就需要去想新的编程范式。

FPGA很多时候是在编译时做分析,来进行决策。例如非功能运算是在运行过程中通过依赖关系来决定。这种方法有诸多不便。其中,依赖关系在编程序的时候就知道了,并非到运行的时候才会发现。新架构编程序的过程中就可以发现其依賴关系,在编译9新架构的新应用

这样变化的结构可以应用到Al,Al还有很多新的变化,不同的应用或神经网络,我们能否通过变结构的方式,只要我们可以识别到一个具体的应用,识别出他用的是一个怎样的神经网络,就可以通过改变今天的功能来适应他,产生全新的发展呢?

如图8所示,采用新架构设计的语音识别芯片,精度已经可以达到91 .8%,可以识别声纹,延时低达25 ms,功耗远远小于1 mW,应用到手机上几乎不耗电;右边是一个人脸识别,人脸识别结果最主要的是精度,可以达到99%,人类只能识别97%,工作在200 MHz,可以实现6 ms,运算功率,每瓦100万亿次的运算。

10 结论

芯片工艺技术进入10 nm,专用集成电路面临严峻的挑战,我们就该在架构上进行创新。其实在高端芯片上也是如此,如果跟着CPU的架构前进,我们永远是跟在别人后面的,能够在架构创新上超过别人才能引领时代。

硬件架构随着软件变化而变化的全新概念在保证芯片的功能满足要求的同时,又能保证其融合性,也是一项很好的创新。