一种短波宽带中频信号数字化实现方法

陈侃 皮明峰 王国波

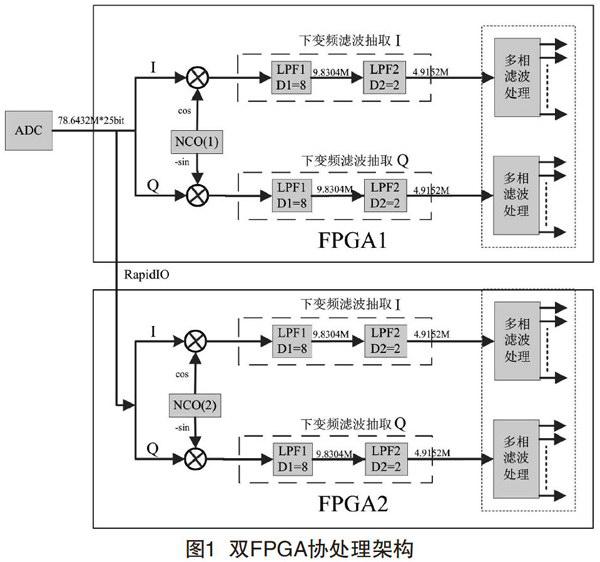

摘要:文章提出一种短波宽带中频信号数字化实现方法。先对宽带中频信号进行带通采样。为保证多相滤波信道化工程实现,提出双FPGA协处理架构。之后对降采样低通滤波和多相滤波信道化实现方案进行资源分析,得出一种最佳的宽带中频信号数字化实现方法。

关键词:多相滤波;中频数字化;降采样

短波通信通过电离层反射来实现远距离通信。由于电离层高度和密度的时刻变化,使得短波通信稳定性较差。同时,3?30 MHz短波通信频段内的全球用户众多。电磁环境复杂,又极易受到其他通信干扰。为获得抗干扰稳定通信能力,采用宽带接收的频率分集合并技术是种不错的解决方案[1]。但受A/D和FPGA器件处理能力制约,传统短波接收机只能对单个3 kHz带宽的窄带中频信号进行数字化处理。近年来,随着器件能力提升,采用目前高性能的A/D和FPGA芯片使短波宽带中频信号数字化实现成为可能。

1 宽带中频信号下变频设计

对于带通信号,假设信号中心频率为f0;,那对应的上下通带的截止频率为fh=f0+B/2, fl=f0-B/2。其中,B为所处理信号的带宽,根据带通采样定理对其进行均匀采样,满足采样值不失真地重建信号的充要条件为:

本设计中: fh==63+6/2=66 MHz,fl=63-6/2=60 MHz。根据式(1)可得采样频率的频率选择范围为:12∪(13.2,13.3333)∪(14.6667,15)∪(16.5,17.1429)∪(18.8571,20)∪(22,24)∪(26.4,30)∪(33,40)∪(44,60)∪(66,120)∪(132,+∞)单位MHz。考虑到后续下变频降采样过程的整数倍抽取,这里A/D器件选择的采样速率为78.643 2 MHz。

为提升的频率分集增益效果,对于6 MHz带宽的短波中频信号,数字接收机至少需要具有512路基带信号的多相滤波信道化处理能力。而目前单片Virtex-5系列FPGA芯片处理能力无法满足要求。由于芯片间RapidIO高速串行接口的支持,这样便可以采用多芯片协处理的方案来实现我们的目标,双FPGA协处理架构如图1所示。

实现步骤如下:

(1)首先,FPGA1通过A/D器件完成对中心频率为63 MHz,带宽6 MHz的中频信号数字采样。之后利用芯片间的RapidIO高速串行接口,将采样数字信号的复制传输给FPGA2以实现并行处理架构。

(2)每片FPGA可通过NCO来实现频谱搬移功能:NC01选择的混频频率为61.5 MHz,NC02选择的混频频率为64.5 MHz。再通过后续低通滤波可以将60?66 MHz的频段划分为2个3 MHz带宽的等间隔区间。即FPGA1处理60?63 MHz频段的中频信号,FPGA2处理63?66 MHz频段的中频信号。

(3)中頻采样信号经过频谱搬移后将进行下变频处理。下变频总抽取倍数为16倍,采样率由78.643 2 MHz降低到4.915 2 MHz以便之后的多相滤波信道化处理。

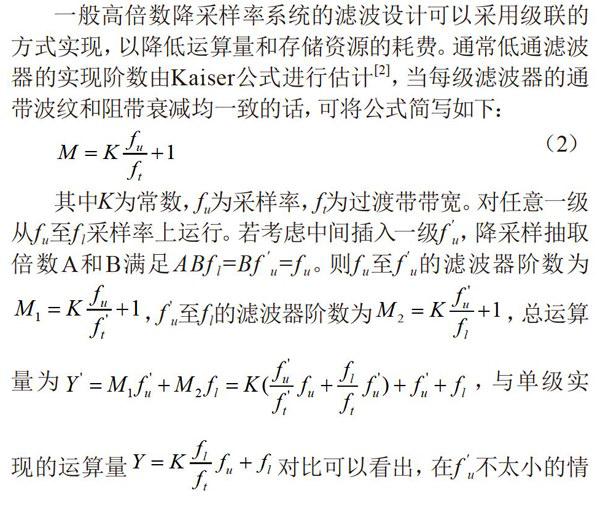

一般高倍数降采样率系统的滤波设计可以采用级联的方式实现,以降低运算量和存储资源的耗费。通常低通滤波器的实现阶数由Kaiser公式进行估计[2],当每级滤波器的通带波纹和阻带衰减均一致的话,可将公式简写如下:

可获得运算量的最大节省。很明显采用两级实现方案,第一级将采样率抽得尽量低是最佳选择。即实现16倍低通降采样,先对中频信号进行8倍抽取后再进行2倍抽取低通滤波,为最省器件资源的实现方案。

2 多相滤波信道化设计

降采样后的中频信号将进入多相滤波信道化实现过程,可以采用低通滤波器实现方法[3]:设输入信号为x(n)则可先将x(n)移至零频处再低通滤波,能直接得到基带信号。设低通滤波器的冲击响应为h(n),那么得到的基带信号为:

2.1 多相滤波设计方案1

两片FPGA均工作在4.915 2 MHz的采样率下,通过多相滤波多信道化处理,分别输出256路采样率为38.4 kHz的基带数据流,根据预先设定的频率中心值,将每个3 kHz带宽的窄带基带信号从其频谱中心搬移到零频,这样输出的256路数据流中,每路基带信号的通带范围为[-12 kHz,12 kHz],相邻通道数据流的中心频点相隔19.2 kHz。

2.2 多相滤波器设计方案2

两片FPGA均工作在4.915 2 MHz的采样率下不变,通过多相滤波信道化处理,分别输出512路采样率为19.2 kHz的数据流,根据预先设定的频率中心值,将每个预设频点的3 kHz基带信号频谱中心搬移到零频,输出的512路数据流中,每路信号的通带范围为[-6.5 kHz,6.5 kHz],相邻通道数据流的中心频点相隔9.6 kHz。

2.3 两种方案FPGA资源消耗情况

两种多相滤波信道化方案的FPGA资源消耗估算情况,如表1所示。

由表1可知:方案2较之方案1的DSP资源多消耗20个,存储资源多用77个18 kB的BlockRAM。如果在进行宽带下变频时,采用I、Q串行输入的方式进行低通滤波,比并行输入方式滤波可节省DSP资源22个,以弥补后续多相滤波DSP资源的消耗。但又考虑到基带信号后续需要进行能量检测处理,若采用方案1需要通过4倍抽取滤波及匹配滤波处理;而采用方案2要进行2倍抽取滤波及匹配滤波处理,资源消耗是方案1的2倍。同时,在多相滤波信道化设计中采用子信道带宽越窄,相邻信道的暂态效应越严重[4],所以综合考虑方案1为最佳的宽带中频信号数字化实现方案。

3 结语

随着通信器件处理能力的高速发展,使多相滤波信道化工程实现成为可能。传统短波窄带通信方式不稳定的弊端,在频率和空间分集技术的引入下迎刃而解。短波通信也将由可用变得更加好用。

[参考文献]

[1]刘丽哲.瑞利衰落信道下带内频率分集性能分析[J].无线通信技术,2012(6):36-37.

[2]杨小牛,楼才义,徐建良.软件无线电原理与应用[M].北京:电子工业出版社,2006.

[3]邓小炜.中频信道化数字接收机方案与算法研究[D].成都:电子科技大学,2008.

[4]姜建军.基于多相滤波的超宽带接收机研究及FPGA实现[D].南京:南京航空航天大学,2010.