一种片内调试功能实现方式的改进方法

中国电子科技集团公司第38研究所 刘小明 许 聪

0 引言

随着集成电路设计和制造工艺的发展,数字信号处理器(Digital Signal Processor)的集成度及性能越来越高,功能日趋复杂。为便于后期DSP应用软件的开发,不同的开发调试手段应运而生。JTAG调试作为最为基础的调试开发手段现已成为嵌入式系统默认集成的开发调试方式。然而不同体系架构DSP处理器在实现JTAG调试时,需要根据实际情况加以适配改进。

本文提出了一种某国产DSP处理器片上调试逻辑实现的改进方案,目的之一是降低调试逻辑控制指令流水启停信号的负载,改善芯片整体时序,其二是在不等长指令流水处理器架构中,避免调试开发时,用户观察到后发指令先生效的现象,产生不必要的误会。

1 工程实现面临的问题

处理器的JTAG片内调试逻辑通常会支持断点、观察点、单步等调试操作,其核心功能是在处理器指令流水满足一定条件的情况下,调试逻辑控制处理器由运行状态转入停止状态,或者命令内核从停止状态转入运行状态[1]。为实现上述功能,需要JTAG调试逻辑提供一个供全芯片使用的全局信号dsp_en(‘0’表示处理器核心进入停止状态,‘1’表示处理器核心进入运行状态),控制处理器核心所有流水线寄存器的更新。由于处理器核心的启停状态切换需要在一个时钟周期内完成,因此dsp_en信号需要与内核工作时钟同频,而不能像调试逻辑中的其他非关键信号可以使用multicycle技术改善时序,所以该信号极有可能成为全芯片物理实现的一个时序关键信号。如果能够通过某种方式减少dsp_en控制的寄存器数目,即减少其负载,将可以有效降低dsp_en的时序实现难度。

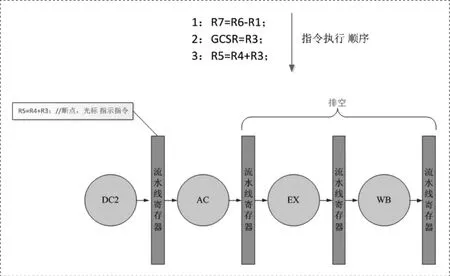

图1 某国产DSP指令流水示意图

图2 某国产DSP断点生效时指令流水示意图

随着DSP性能的提升以及功能的不断丰富,DSP处理器核心通常会采用较深的指令流水,指令的执行也会采用多级流水形式[2]。出于处理器执行效率的考虑,处理器中不同指令的执行流水可能不等长,也就是不同类型的指令在不同的指令流水级生效。下图为某国产DSP的指令流水示意图,其中AC、EX、WB为指令生效的主要3个流水级,其中地址辅助寄存更新、内核控制寄存器更新、核外访存等指令在AC级生效;ACC/MACC/SACC等特殊寄存器的更新在EX级生效;通用寄存器更新在WB级生效(见图1)。

该DSP处理器断点、观察点、单步生效时,内核会转入停止状态,所有流水线寄存器停止更新。软件开发界面光标所指示的指令会停止在DC2级流水线寄存器上。由于指令的生效时机不一样,会观察到后发指令先生效的状况,虽然经过时序规划此种设计不存在功能问题,但会引发用户的困惑。示例如图2,断点生效后后发射的特殊寄存器GCSR赋值指令会先于通用寄存器R7更新指令生效。

2 解决措施

鉴于上述问题,考虑在指令流水控制器与调试逻辑之间增加握手机制,已断点实现为例,当断点等触发时,不立即将DSP内核转入停止状态,而是在AC级生成一个普通的指令流水阻塞信号,将断点所处指令及其后续指令阻塞进入AC级,待ACEXWB三级流水上的指令全部排空,即全部执行完毕后,指令流水控制器通知调试逻辑,调试逻辑再真正将DSP核心转入停止状态(dsp_en清0)。在排空指令流水的过程中,EX级若有分支指令生效,可以取消由于断点引发的阻塞, flush整个指令流水,即断点未生效。

图3 某国产DSP断点触发改进方案

上述措施执行后可以产生如下效果:

后三级指令流水(AC/EX/WB)寄存器不再受dsp_en控制(后三级的寄存器数目可以达到整个DSP内核寄存器数目的三分之一),降低dsp_en信号的负载,同时降低了布线难度。

断点真正生效时,先于断点所标记指令之前发射的所有指令全部生效,避免用户观察到后发指令先生效的情况出现。

后续伴随执行流水更长的指令出现时,此实现方案同样适用。

上述断点的处理方法,同样适用于观察点/单步操作,即JTAG调试常用的调试操作可以统一。

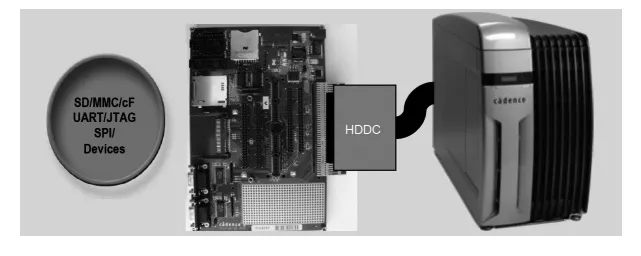

为检验改进方案的正确性,基于cadence公司的PalladiumXP硬件加速平台构建软硬件协同仿真平台[2]。

图4 PXP仿真验证平台

基于仿真验证平台,可以随机产生测试激励,随机设置断点、观察点,连续执行单步操作,经过测试证明该实现方案切实可行。

图5 仿真测试结果

3 结束语

本文介绍的调试逻辑改进方案是针对某国产DSP超长指令字的并行处理结构设计,可以有效降低调试逻辑全局控制信号的物理设计难度,同时改进用户调试开发体验,现已在某国产DSP中得到实际使用,效果良好,未来会在系列DSP产品中得到更进一步的应用。