星载机检错纠错模拟系统设计与实现

张志洲, 李东阳

(国防科技大学 空天科学学院,长沙 410073)

0 引 言

大气外层空间存在很强的自然辐射,主要来自各种宇宙射线和一些高能粒子(包括高能质子、中子、粒子、重离子等)。高能粒子具有很高的能量,很难通过屏蔽来防护。特别是随着微电子技术的发展,微电子器件体积小、质量轻、功耗低的特点使其迅速在航天器中得到广泛应用,并且它的集成度越来越高,于是出现了单个高能带电粒子造成航天器逻辑系统紊乱,导致航天器故障的单粒子效应(Single Event Effect,SEE)[1-2]。在众多的SEE中,对电路影响最大的,也是人们最为关注的分别是单粒子闩锁效应和单粒子翻转效应(Single Event Upset,SEU),其中又以SEU对星载RAM的影响最大[3-4]。

单粒子翻转效应是人们最早发现的单粒子效应,所造成的逻辑错误不是永久的,属于单粒子效应中的一种软性错误,通过系统复位、重新加电或写入可恢复。其最主要的影响是使存储器数据位翻转 (“1”变“0”,“0”变“1”)[2,5]。飞行记录表明,单个高能粒子引发的单粒子翻转导致大量飞行器发生故障,轻则引起卫星各种数据错误;重则导致卫星执行错误指令、发生异常或故障,甚至使卫星处于灾难性局面之中。

1989年10月的太阳质子事件期间,美国TDRS-1卫星的RAM存储器记录到239次单粒子翻转事件。“风云一号B”气象卫星于1990年9月发射后,星上姿控计算机多次出现单粒子翻转,从而致使卫星姿态失控、卫星失效;美国MSTI和IRON9906卫星分别于1993年和1997年发生严重单粒子效应而提前结束寿命。“实践四号”探测卫星平均每天测到3.4次单粒子翻转事件[6-9]。

由于航天器设计要求电子器件的体积小、功耗低、存储量大、运行速度快,这就必然促使微电子器件的集成度提高,内部的单元电路体积缩小,而每一次状态改变所需的能量和电荷下降,其结果是抗单粒子效应的能力下降。因此,随着航天事业的发展和微电子器件集成度的提高,将会不断出现新的单粒子效应问题。在航天电子设计领域中,这已经成为一个不能忽视的问题,必须提出有效的手段加以解决。

本文采用EDAC技术用于克服单粒子翻转引起的航天电子系统故障,优势在于可以延长卫星寿命,提高卫星应用能力,非常适合未来敏捷航天器的平台需要。通过了解国内外关于EDAC技术方面的研究现状,本文提出了星载机EDAC模拟系统设计方案,给出星载机EDAC模拟系统硬件电路设计,完成星载机EDAC模拟系统软件设计,最后进行演示验证。

1 系统设计方案

错误检测与纠正(Error Detection And Correction,EDAC)技术是一种差错控制技术,也称作纠错编码、数据校验码。它是一种具有发现某些错误和自动改错能力的数据编码方法,起初应用于数字通信系统中用以提高数据传输的可靠性,现在也应用于星载处理器中用以提高星载RAM存储数据的可靠性,防止RAM内部因单粒子翻转效应引发的错误。其工作原理是首先对要存储到RAM中的数据进行编码,即在原始数据中以一定的规则加入不同方式的冗余码,然后存储到RAM内。在对数据进行读取时,依靠多余的冗余码来发现或纠正数据的错误。

目前,国内外航天界对存储器的EDAC实现已经很少采用EDAC专用芯片,而一般采用以下两种方式:①将EDAC功能直接集成在航天用CPU芯片内;②使用没有集成EDAC功能的CPU,采用FPGA或其它器件实现EDAC功能[10-16]。

1.1 系统需求

本文设计一种EDAC系统,可模拟因单粒子翻转引起的翻转故障,并可能利用EDAC技术排除故障。一般地,EDAC过程实现方案大致可分为硬件和软件两种方案。硬件方案是通过硬件逻辑器件(分离元件、现场可编程逻辑器件)实现;软件方案是在处理器内部,通过EDAC编码和解码程序进行处理。

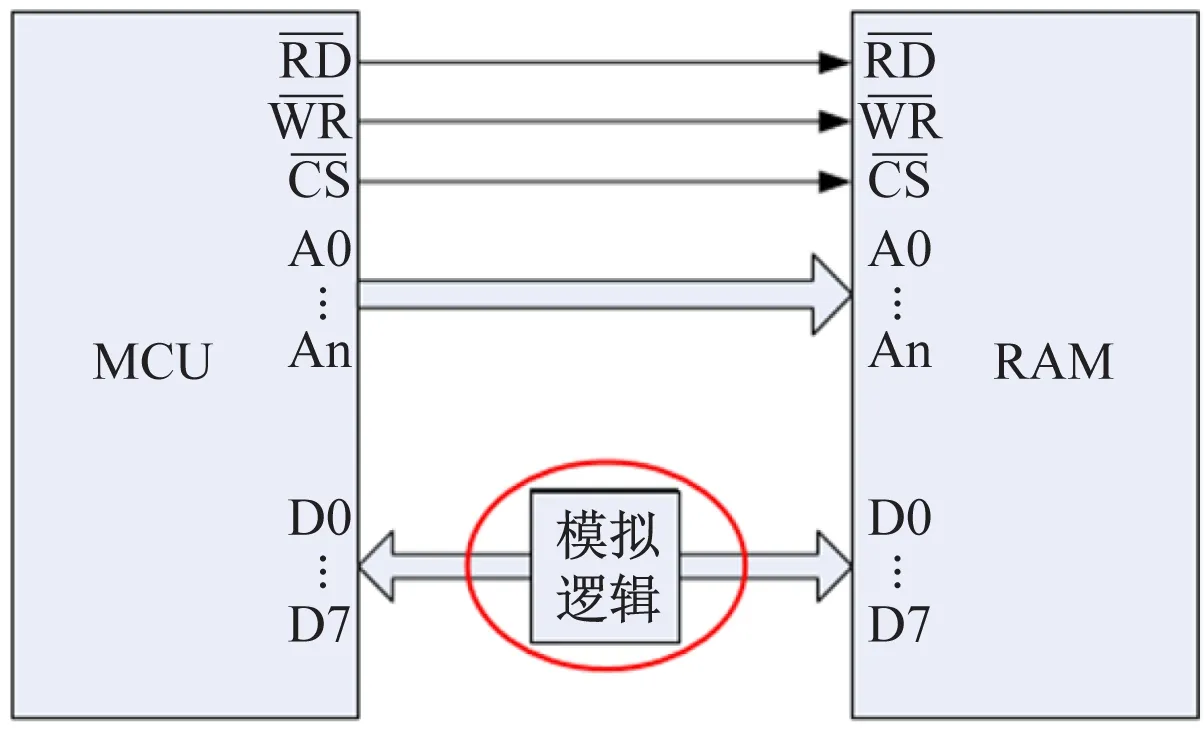

1.2 系统方案

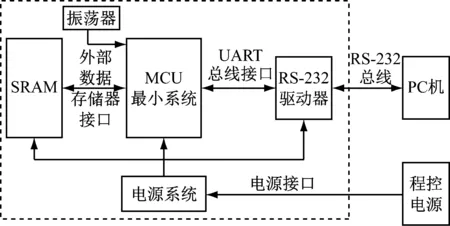

本文采用软件方案。在MCU和SRAM之间设计模拟逻辑模拟单粒子翻转故障,然后通过EDAC编码程序检查并纠正错误,其结构框图如图1所示。设计步骤主要包括:①设计带有MCU、RS-232接口和扩展RAM的模拟星载机,并制板实现;②串口接收数据,进行EDAC编码后,写入存储器;③读取存储器数据时随机注入错误,星载计算机进行EDAC处理,将错误数据和纠错数据发送回PC机记录。

图1 星载机EDAC模拟系统方案

2 EDAC工作原理

目前,绝大多数的高可靠微处理器中都采用了一定的EDAC技术。EDAC有多种编码方式,不同的编码方式有不同的检错和纠错能力。例如奇偶校验码只能检测出一个码字中的奇数位错误,但是不能定位错误更不能纠正错误。其他的,如汉明码可以纠正一个码字中任何1位错误,检测出两位错误,但是对于多位错误不具有任何的检错和纠错能力。当然,还有许多其他的编码方式,可以检测和纠正一个码字中的多位错误,但是它们的算法往往更为复杂,增加了编码器和译码器的实现难度,增加了电路面积开销,而且关键路径中的延时也会变得更大。

2.1 汉明码

汉明码[9,12,16]有多种编码方式,如果只要求纠错1位错误,那么校验位K和数据位N之间的对应关系如表1所示。

表1 校验位K和数据位N之间的对应关系表

2.2 编码规则

数据存储时常见的编码方式为(7,4),这里阐述汉明码(7,4)编码的规则。

假设汉明码共m位(HmHm-1…H2H1),包括N位数据位(DNDN-1…D1)和K位校验位(PKPK-1…P1)。

规则1每个校验位Pi在汉明码中被分在位号2i-1的位置,其余为数据位,并从低到高依次排列。

以(7,4)为例,3个校验位分别对应汉明码的位号为1、2、4。排列顺序为D4D3D2P3D1P2P1。

规则2每1位校验码Hi由多个校验位校验,其关系为被校验的每1位位号要等于校验它的校验位的位号之和。

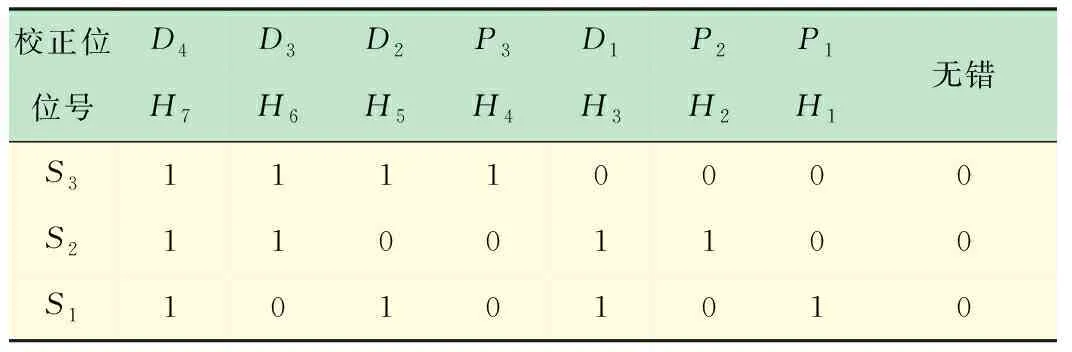

(7,4)编码的7位汉明码如表2所示。

表2 (7,4)编码的7位汉明码表

据此,可以求出由各有关数据位形成Pi值的偶校验结果:

P1=D1⊕D2⊕D4

P2=D1⊕D2⊕D4

P3=D2⊕D3⊕D4

2.3 解码规则

根据如下关系对汉明码进行偶校验:

S1=P1⊕D1⊕D2⊕D4

S2=P2⊕D1⊕D2⊕D4

S3=P3⊕D2⊕D3⊕D4

记S=S3∶S1为伴随向量。根据S3∶S1中“1”的数量和位置可以反映汉明码的出错情况。

若在传输过程中只有1位出错,可以得出错误位与伴随向量的对应关系(即汉明码译码表),如表3所示。

表3 错误位与伴随向量的对应关系表

2.4 处理流程

基于汉明码的EDAC技术的处理流程为:

(1) 编码。根据数据位(D)计算校验位(P)形成汉明编码(H),将编码H存储到RAM中。

(2) 解码。从RAM中读出汉明编码(R),计算伴随向量(S),根据汉明码译码表确定错误位置,并进行纠正。

(3) 错误处理。如果发现1位错误,则进行数据回写。如果发现超过1位错误,则告知CPU发生多位错误。

2.5 EDAC过程模拟

在MCU和SRAM之间专门设计故障注入单元来模拟单粒子翻转故障,然后通过EDAC编码程序检查并纠正错误。

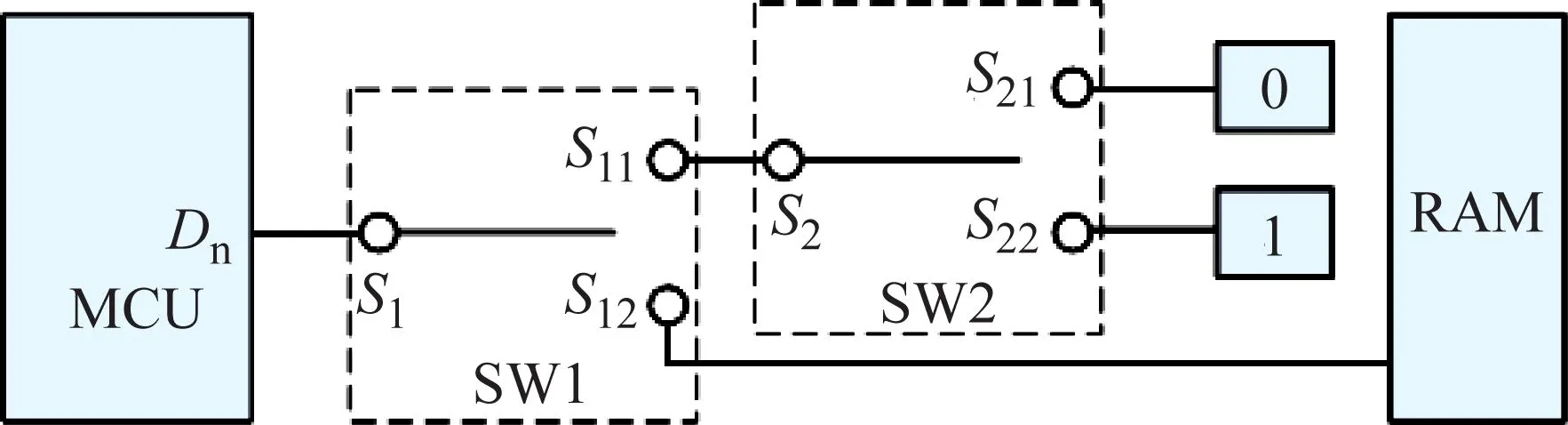

模拟步骤如图2所示。①数据写入时,S1与S12相连,数据正确写入RAM。②数据读出时,将S1与S11相连,当S2与S22相连时,Dn位始终为“0”,当S2与S22相连时,Dn位始终为“1”。当Dn的状态与RAM中实际状态相反时,就是1位SEU故障。

图2 SEU模拟逻辑图

EDAC编码流程:①根据数据D计算校验码P;②将数据写入外部RAM的Addr地址;③将校验码写入外部RAM的Addr+1地址。

EDAC解码流程:①从RAM的Addr地址读回数据位;②从RAM的Addr+1地址读回校验位;③计算伴随向量S;④根据S4、S3、S2、S1译码,确定错误位置,并纠正数据位;⑤如果S不全为0且没有对应编码,则错误超过1位。

3 硬件电路设计

按照EDAC模拟系统的设计需求,给出系统硬件架构,其总体结构图如图3所示。

图3 星载机EDAC模拟系统硬件架构

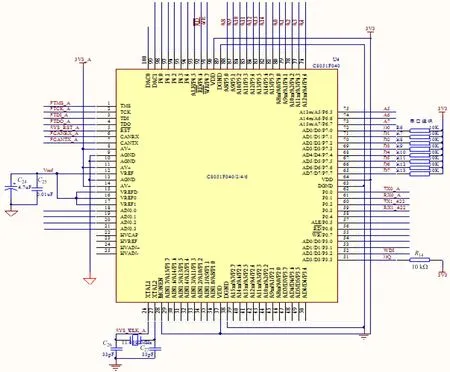

(1) 单片机最小系统。本系统采用Silicon Laboratories公司的C8051F040单片机。C8051单片机是功能最强大的8位单片机之一,具有飞行经历。

单片机最小系统如图4所示。除了电源接口、复位接口、时钟电路,该系统还提供了RAM接口、通信接口等。

图4 单片机最小系统

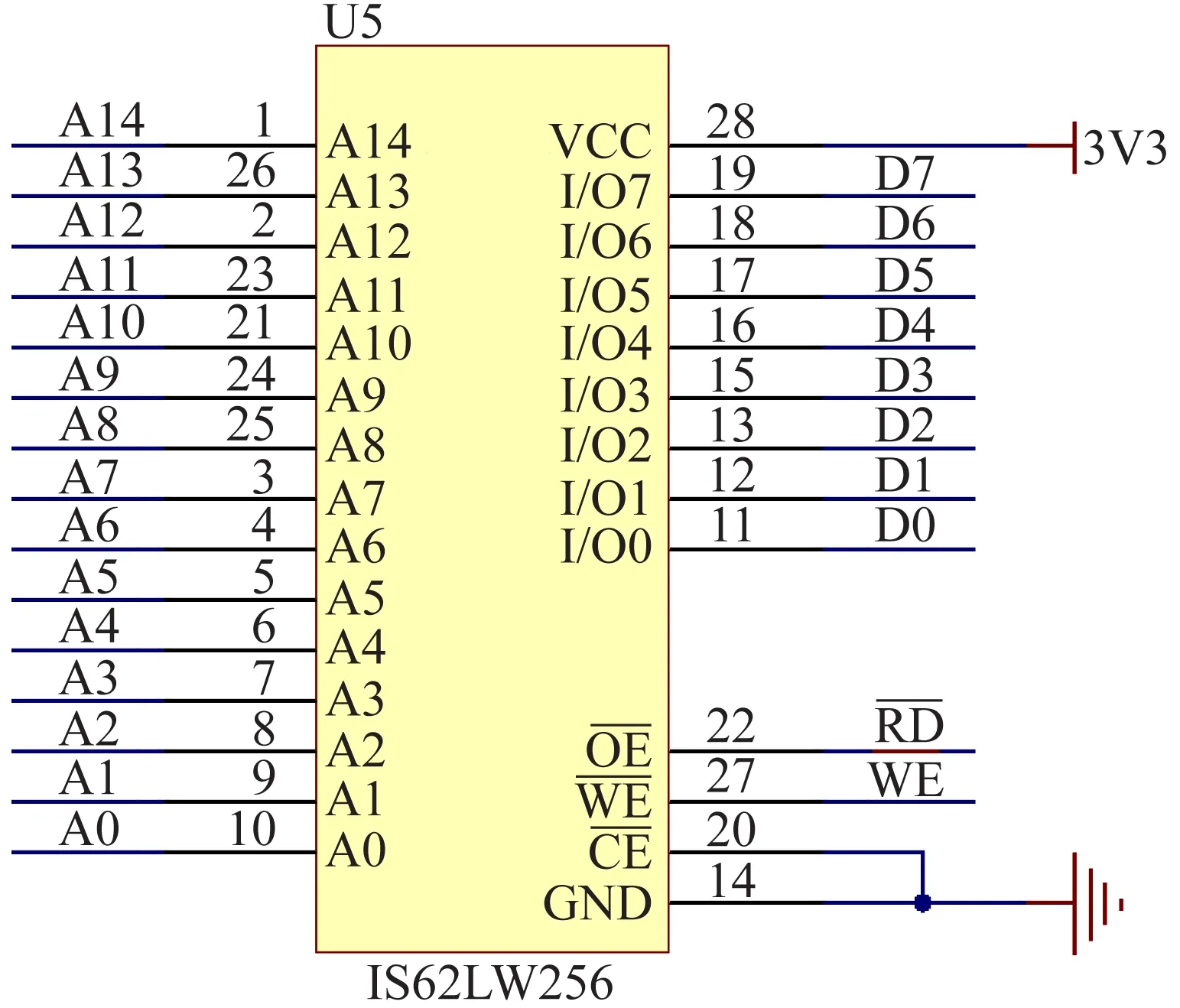

(2) RAM存储单元。RAM存储单元包括15位地址线和8位数据线,如图5所示。

图5 RAM存储单元

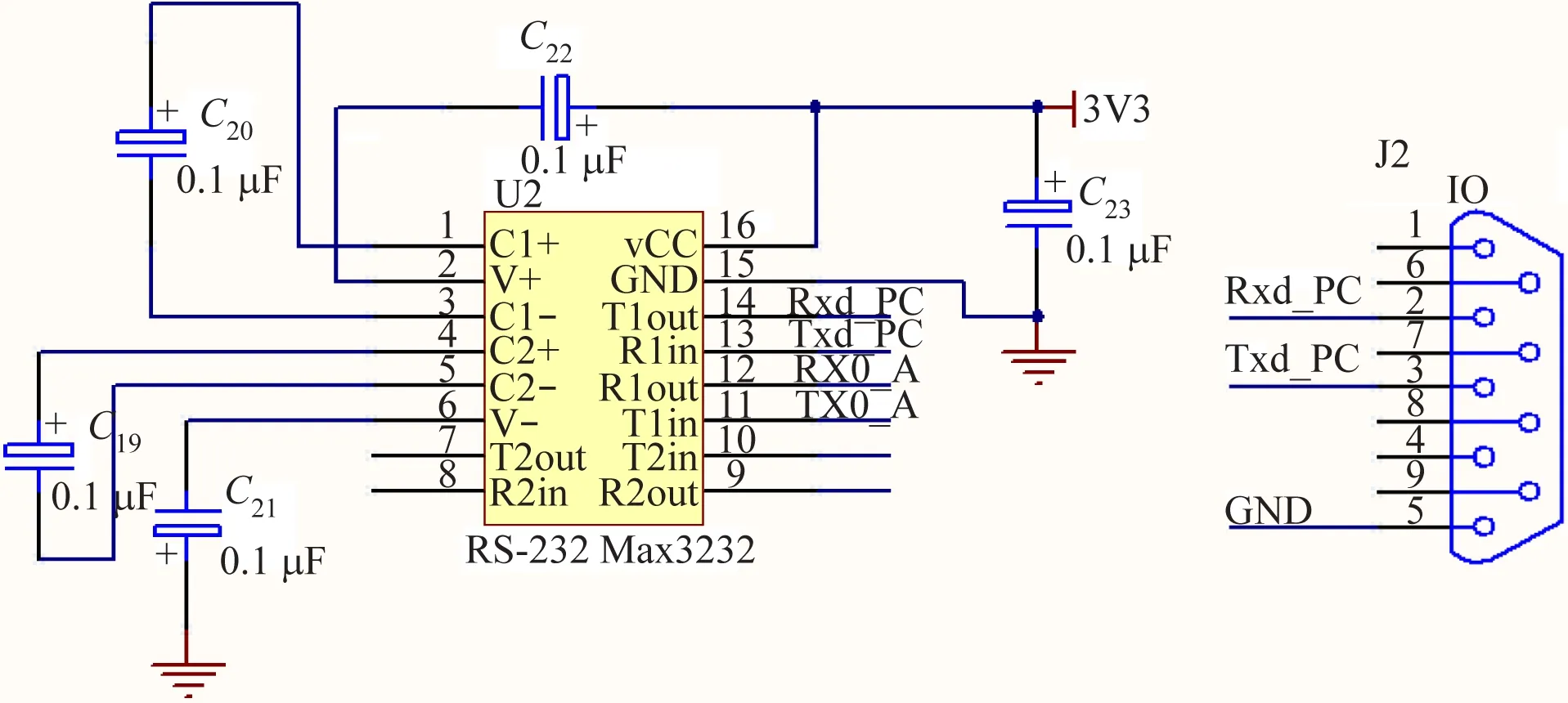

(3) 通信接口。通信接口将单片机的数据TX0_A发送至上位机Txd_PC,同时将上位机的命令Rxd_PC传递到单片机RX0_A(见图6)。按照上述硬件系统的设计要求,完成PCB的布局、布线、加工和焊接。

4 软件架构设计

该系统的软件算法用于模拟EDAC过程,采用(7,4)编码结构,能验证1位出错时的检错与纠错过程。模拟过程如下:

(1) PC机通过串口发送一个0x00~0x0F之间的16进制数给星载计算机(OBC);

图6 通信接口

(2) OBC将数据进行EDAC编码后正常写入RAM;

(3) 对外部故障注入单元的某1位强制为0或1,以此造成RAM数据存储过程中的某1位错误,模拟一次SEU事件;

(4) PC机发送命令控制OBC读出RAM存储的数据;

(5) OBC对读出的数据进行EDAC校验;

(6) OBC将读出的原始数据、EDAC校验后数据、错误数据编码等通过串口发送给PC机;

(7) 在PC机对处理结果进行判断。

涉及的软件程序包括:

(1) 系统的初始化。主要包括禁止看门狗定时器、配置系统时钟、端口配置、串口初始化、RAM模块测试等。

(2) 接收数据。包括测试串口通信,等待串口发送数据,接收数据后再发送回PC。

(3) 数据编码。首先将十进制数转化为二进制序列,然后根据汉明码算法计算以上4位有效数据的校验码P1、P2、P3,保存到 BinaryArray 数组中,即1、2、4位保存校验位,3、5、6、7保存数据位。将BinaryArray数组中保存的数据(Dx)和校验码(Px)按照汉明码的编码方式进行编码后,保存到变量CodeData中,并将CodeData写入RAM。

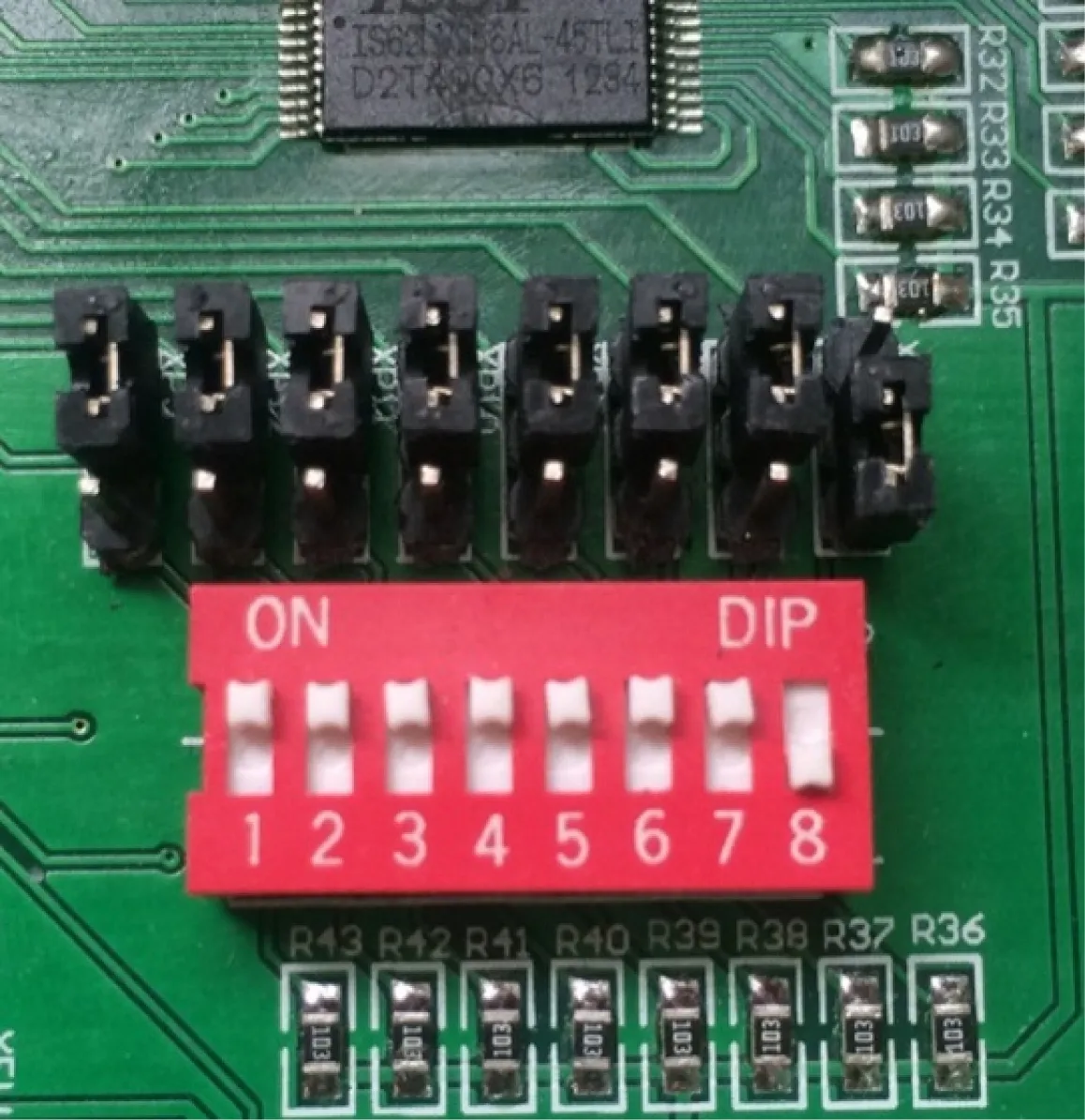

(4) 数据解码。人工调整拨码开关,强制该位为0或1,使得某数据位出现编码翻转。然后读取内存data_buffer[0],保存到变量ReadData中。随后根据汉明码,使用数组BinaryArray计算校验码S1、S2、S3。根据校验码S1、S2、S3计算S。按照前文的错误位与伴随向量的对应关系表,发现故障位ErrorBit,同时调整数据翻转位ErrorBit的值,完成纠错,并将纠错后的数据重新保存。

5 演示验证

演示过程分为以下几个步骤:

(1) 打开串口助手,设置串口号COM,波特率为600 b/s,校验位为NONE,数据位8,停止位1,设定16进制发送,然后运行程序。

(2) PC用串口助手手动发送00~0F的16进制数。如在“发送的字符/数据”一栏中填入2个8位的16进制数,点击发送。串口助手界面将显示刚发送的数据SendData,解析出4为有效数据ValidData,给出编码后的数据CodeData。

(3) 设置故障位,跳线、拨动拨码开关,并且再次点击“手动发送”,编码后的数据将写入RAM。串口助手的界面将显示出读回的数据ReadData,标示出错误的位ErrorBit,并给出校正后的数据DecoData。

这里演示某数第0位检错纠错过程。①发送16进制数据“14”,界面显示收到发送的数据SendData位“14”,解析出4为有效数据ValidData为“04”,给出编码后的数据CodeData为“2A”。②设置跳线和拨动拨码开关,令数据第1位为“1”,并且再次点击“手动发送”,编码后的数据将写入RAM。串口助手的界面将显示出读回的数据ReadData为“2B”,标示出错误的位ErrorBit为“1”,并给出校正后的数据DecoData为“04”。其中,强制设置数据第1位为1的故障注入单元如图7所示。

整个演示过程串口助手界面的显示结果如图8所示。

上述演示结果表明,星载机检错纠错模拟系统可以模拟MCU和RAM存储单位间的1位数据翻转,并且可以自动纠正该位错误。通过多次选择不同的16进制数据,上述模拟系统都能很好的模拟1位数据位故障,并能正确地纠正出该位错误。

图7 数据位第1位强制置1

图8 演示结果

6 结 语

本文设计了基于汉明码的EDAC存储器检错纠错模拟系统。包括带有MCU、RS-232接口和扩展RAM的模拟星载机,可以随机模拟RAM存储数据过程中的1位错误,此时该系统读取带有1位故障位的存储器数据时能进行EDAC处理,将错误数据和纠错数据发送回PC机记录,自动完成检错纠错过程。整个过程模拟了因单粒子效应引起的翻转故障,并运用了EDAC技术进行消除,达到了预期的设计效果。