一种支持源代码级调试的全芯片仿真技术*

, ,

(中国电子科技集团公司第三十八研究所, 安徽合肥 230088)

0 引言

随着半导体工艺的快速发展,以及“摩尔定律”所预言的晶体管增长趋势,芯片规模、设计复杂度都在持续不断迅速增大,片上系统(System on Chip, SoC)已成为主流的设计技术。为了缩短IC开发周期,目前的主流设计方法是采用软件与硬件同时开发的手段,在实体硬件还没有就位之前,软件开发调试一般在系统仿真平台上进行。在项目早期构建功能完备并支持源代码级调试的全芯片仿真平台能够大幅提升目标软件的开发效率,对整个项目的顺利完成以及芯片产品的迅速推广具有重要意义。

使用完全基于Verilog HDL硬件描述语言的数字前端仿真平台[1-4]可以保证系统的周期精确性与功能完整性,但存在仿真速度慢且无法实现源代码级调试的缺点。只能通过指令级或者汇编级的调试发现问题再反向追溯到高级语言的源代码,不仅调试难度大而且效率低下。

使用基于C/C++的纯软件仿真方法[5-8]建立的目标机模型可以支持源代码级调试且具有描述能力强、抽象层次丰富、仿真速度快等诸多优势,但是在一个较大规模的全芯片系统中想要同时获取所有子模块对应的软件模型难度较大,在实际操作中几乎很难满足。另一方面,由于到目前为止,工业界IC设计还是广泛采用基于硬件描述语言Verilog HDL,因此基于Verilog HDL的前端数字仿真IP库相当丰富。如果能够有效地结合两类不同的模型建立可源码级调试的系统级仿真平台,则对于早期开展目标机相关的操作系统程序及硬件驱动程序都具有重要意义。

本文针对以上问题,首先在第1节介绍基于SystemC[9]的纯软件虚拟仿真方法并分析其特点;第2节提出了一种基于VPI技术的可支持C语言源码级调试的全芯片混合仿真方法并通过实际工程应用证明其有效性;最后总结全文。

1 SystemC软件建模方法

基于片上网络的复杂SoC电子系统的设计需要使用先进的系统级描述语言对其进行描述。SystemC是由OSCI(Open SystemC Initiative)提出的一种基于C++的统一建模平台,其本质是在C++的基础上添加了硬件扩展库和仿真核,这使得SystemC可以在不同的抽象级别对复杂电子系统建模,解决了传统C++语言在描述硬件时不具有并发性、时序概念等缺陷,从而可以在系统级用高级语言统一描述软件和硬件行为。SystemC基本体系结构框架如图1所示。

SystemC中关键类的继承关系如图2所示,其最底层是一个节拍式仿真内核,由sc_simcontext类封装。其他常用的关键类型如下。

1) 模块(sc_module)

一种层次化实体,可嵌套其他模块和过程,一般一个完整的SystemC仿真系统可由大量模块经实例化后互联组成。

2) 过程(sc_process)

用来描述模块的具体功能,可由事件触发,多个过程可并行执行,SystemC支持3种不同的过程类型:方法过程(sc_method、线程过程(sc_thread)及时钟线程(sc_cthread)。

3) 接口(sc_interface)

定义了一组方法实现目标,但是不实现。

4) 通道(sc_channel)

实现了接口中定义的方法,分为基本通道和层次化通道。

5) 信号(sc_signal)

用来实现各个过程之间的通信,SystemC提供了多种信号格式来满足从寄存器传输级(Register Transmit Level,RTL)到功能级等不同抽象级的模拟。

6) 事件(sc_event)

用来触发各个过程的开始以及暂停,通常多个事件组成一个敏感列表(sensitive list)共同控制一个过程的状态。

7) 时钟(sc_clock)

时钟在同步电路设计中是一个非常重要的角色,本质上是一种特殊的信号,为仿真过程提供了时间基准。

由于SystemC中添加了专门用于硬件描述的类库和仿真内核,使之可以在抽象层次较低的RTL层次对系统进行描述。尤其是SystemC支持延迟赋值这一硬件特殊行为,通过支持Δ延迟(delta-delay)来支持硬件信号的行为建模,Δ延迟是最小的仿真步骤,一个Δ周期包括许多估值 (evaluate)和更新(update)相,当事件调用notify()时,将在仿真环境的事件队列中插入这个事件,用request_update()发出更新请求,在更新相时,调用update()更新信号。

另外,由于SystemC是完全基于标准C++实现的,使得其对抽象层次较高的行为级、算法级的系统任务天然地具有非常强的描述能力,同时有大量成熟的软件库可供使用,也较容易实现支持源代码级调试的调试器[10-12]。

目前使用完全基于SystemC的纯软件仿真方法所面临的主要问题是基于SystemC建立的模型库还不够完善,很多面向工业级应用的IP核依然缺乏;另一方面,由于历史上Verilog HDL长期在工业界的数字前端设计领域占主导地位,因此基于Verilog HDL设计开发的模型库是相当丰富的。

2 基于VPI技术的全芯片仿真

针对前文中对SystemC建模仿真方法的优势及劣势的分析,本文提出一种基于VPI技术的全芯片混合仿真方法。

VPI(Verilog Procedural Interface)是第三代Verilog HDL与C语言过程调用接口,目前已经成为IEEE 1364标准(IEEE Verilog HDL标准)的一部分,其中定义了一组标准API接口用以实现Verilog与标准C之间的通信。利用此接口,一方面可以为Verilog硬件代码添加额外的用C实现的系统函数以弥补Verilog行为级描述能力的不足;另一方面,可以在软件代码中根据需要直接以后门方式读写Verilog硬件代码中的仿真部件(如reg,wire,memory等),VPI技术为软硬件混合仿真提供了必要条件。

一些关键的VPI接口及其概要描述如表1所示。

表1 VPI中常用API概述

通过使用VPI技术可以实现全芯片级的软硬件混合仿真平台的搭建,将系统中复杂度最高、运算量最集中的指令执行模块使用周期精确的软件模型构建,同时对其他缺乏周期精确软件模型的模块直接使用Verilog HDL数字电路模型。因为目标机是由软件实现的,因此自然地可以使用Socket编程方法实现本地Jtag Server进程与远程软件集成开发环境IDE(Integrated Development Environment )中运行的Jtag Client进程之间的通信,且由于使用了VPI技术,因此软硬件模型之间的通信一方面可以通过传统的端口连接实现,另一方面也可以通过VPI定义的API接口实现,如图3所示。

图3中最左侧模块可认为是有调试需求的指令执行部件,如CPU,DSP等,因此使用SystemC建立其周期精确的模拟;最右侧使用Verilog模型可能是因为其软件建模困难,或者已存在成熟的商用IP核;中间的模块可以视为一个桥接功能模块,一方面它与软件模型之间通过TLM[13](Transaction Level Modeling,一种基于SystemC的事务级仿真框架)方式通信,通过C++函数调用接口nb_transport_bw/nb_transport_fw来传递被包装成generic_payload(TLM中指定的数据帧格式)的数据帧,另一方面它通过sc_signal

“魂芯”多核DSP[14]是一款完全由中国电子科技集团公司第三十八研究所自主研发的面向高性能电子应用领域的通用DSP。由于该款芯片面向高端应用,因此其支持多种高速外设,而同时获取或者构建所有这些外设控制器的周期精确的软件模型是不现实的,同时也没有必要,而逻辑最复杂同时也是计算量最密集的计算内核模块其周期精确的软件模型是可用的。基于以上事实,在该款DSP的实际设计中使用了本文提出的基于VPI技术的混合仿真方法为其构建了软硬件混合仿真平台,该平台的大致结构如图4所示。图中的顶层是全芯片层,其中包含众多的Verilog硬件模型,如AHB,Uart,RapidIO,PCIE等,而内核计算模型则是由SystemC实现的周期精确的模型(其内部实现了Jtag进程),另外在内核内部中还嵌入了一个DMAC(DMA Controller)硬件电路模型,整个混合仿真平台既保证了系统的完整性,同时还支持在远端IDE上进行基于源代码级的软件开发。

由于该混合仿真平台使用周期精确的软件模型描述计算内核,因此仿真速度大概是纯硬件仿真速度的10~100倍(由目标机运行的应用程序决定),同时由于此平台包含了几乎所有高速外设的Verilog HDL模型,因此它也是功能完备的。在芯片流片的窗口期该平台支撑了操作系统、驱动程序等目标机相关生态软件的开发、调试,为大幅缩短产品研发周期起到了关键作用。

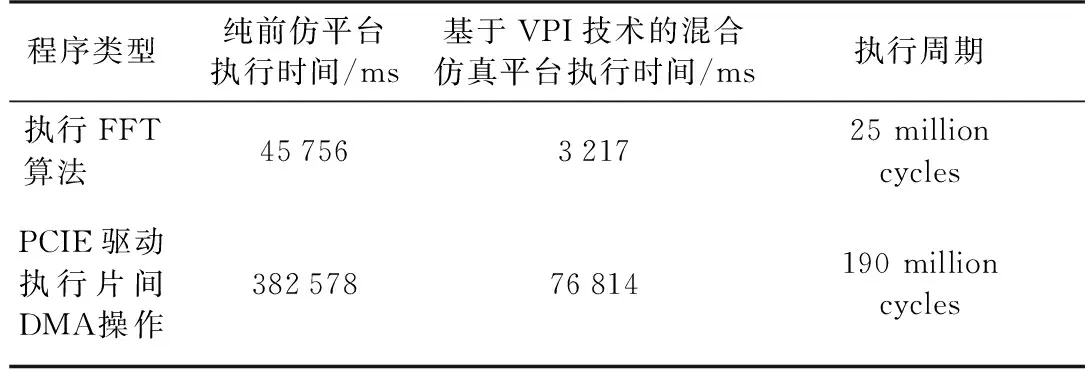

具体的执行效率对比如表2所示,第一项显示了外设无关的程序在前仿平台和混合仿真平台在执行效率方面的对比(执行FFT算法),可以显然地发现在完成同样的仿真周期数的前提下,本文提出的混合仿真方法在执行效率方面相比纯RTL的前仿平台提升了大约1~1.5个数量级。而第二项显示了一种PCIE驱动程序调试情景下的执行效率对比(通过PCIE执行片间DMA),由于存在内核与外设RTL模型的周期级交互,因此混合仿真平台的执行效率有所下降,但仍然远远领先于纯前仿平台,大约提升了0.6个数量级。

表2 纯前仿平台与VPI混合仿真平台的执行效率对比

3 结束语

在IC设计早期建立支持高级语言源码级调试的全系统仿真平台对于提升嵌入式软件开发效率具有非常重要的意义。基于C++的SystemC仿真方法具有描述能力强、仿真速度快、可用软件库丰富等优点,但是目前工业界中大量使用的还是基于Verilog HDL的IP核,基于SystemC实现的周期精确的仿真模型相对还比较匮乏。在实际工程应用中试图搭建功能完备的纯软件仿真平台难度较大,可能需要放弃系统的完整性,而系统功能完整性对于操作系统软件以及硬件驱动程序的开发是非常必要的。本文提出一种基于VPI技术的全芯片混合仿真方法,通过后门读写的方式完成软件模型与硬件模型的交互,一方面保证了系统的完整性,同时支持多种源码级调试手段。最后通过将该方法在一款实际DSP设计中的应用说明了本文提出方法是可行的、有效的。

另外,本文提出的混合仿真方法在执行效率方面还有进一步提升的空间。由于使用了VPI编程接口,因此使得系统软硬件模块的裁剪变得更加灵活和自由,一方面,可以在面向某些特定需求的仿真时,根据需要裁减掉一些当前场景下无关的大型复杂的硬件模型;另一方面,当周期精确不再是系统必需的特征时,可以使用TLM方法进行行为级建模,进而进一步大幅提升执行效率。以上是下一步研究的重点内容。