基于FPGA的HS400模式eMMC控制器设计与实现*

张 煜,陈 微,吴利舟,肖 侬

(1.国防科技大学计算机学院,湖南 长沙 410073; 2.国防科技大学高性能国家重点实验室,湖南 长沙 410073)

1 引言

嵌入式多媒体卡eMMC(embedded Multi Media Card)是一种主要针对移动设备的内嵌式存储设备,用于代码和数据的存储。eMMC结构主要包括快闪存储器设备NAND Flash、主控制器以及多媒体卡MMC(Multi Media Card)接口,外部为球栅阵列BGA(Ball Grid Array)封装。eMMC具有体积小、复杂度低、集成度高、布线难度低等特点。eMMC可以很好地解决内部NAND Flash的MLC(Multi-Level Cell)与TLC(Tri-Level-Cell)管理,ECC(Error Correcting Code)纠错、区块管理、损耗均衡管理、指令管理、低功耗管理等方面的问题。eMMC能够在提供移动设备所需要的功能和性能的同时保持低功耗,并且支持大数据的高带宽传输与代码中常见的小的随机数据访问,同时提供多种安全功能。2015年3月,JEDFC发布最新的eMMC 5.1(JESD84-B51)[1]协议标准,在各大生产商根据新的协议标准推出芯片的同时,开发基于新协议的高速、安全、低功耗的eMMC控制器具有重要的意义和应用前景。当前基于eMMC 5.1标准协议所设计的eMMC控制器中大部分还停留在仿真阶段,并且使用低速总线速度模式[2]。

本文在FPGA平台设计并实现了一种高速安全的eMMC控制器,利用最新的eMMC 5.1协议标准,采用HS400高速源同步模式设计,数据传输速率可达400 MB/s。在数据传输的过程中为了保证数据传输的正确性和完整性,对数据使用CRC校验。利用FPGA高速并行的特点实现CRC校验和数据传输同时进行,并使校验位紧随数据位传输,因此最大化传输速率。设计针对最新的协议标准,可以实现向下兼容,并适用于不同厂商推出的芯片。

本文将eMMC控制器在硬件平台上进行实现和测试,结果表明eMMC控制器可正确完成读写指令解析以及高速读写操作[3]。实验平台采用母板/子板总体架构,母板为Xilinx Zynq-7000 FPGA开发板Zedboard,子板为eMMC芯片制作而成的FMC(FPGA Mezzanine Card)子板[4]。eMMC控制器通过母板的FMC接口与子板进行通信,通过执行一系列连续的读写命令实现对设计方案的正确性验证。

2 eMMC与HS400模式

2.1 eMMC概述

eMMC设备内部由NAND Flash以及主控制器组成,带有标准的MMC接口。eMMC通信包括11条通信总线,即CLK线、数据选通DS(Data Strobe)线、CMD线及DAT0-DAT7线。时钟信号CLK控制eMMC设备读写频率;DS由eMMC设备产生,用于控制HS400模式下数据读频率;CMD为双向命令通道,用于命令与响应的传输;DAT0-DAT7为双向数据通道,用于数据的传输。

eMMC上电或者复位后,根据协议,首先要对其进行初始化操作。初始化操作成功后,可通过CMD线传输命令对eMMC设备进行总线模式配置、数据读写等操作。

如果需要使用高速总线模式,则可通过发送一系列命令配置需要的总线速度模式。eMMC定义了多种总线速度模式,如表1所示。本文设计是在HS400模式下展开的。

Table 1 Bus speed modes表1 总线速度模式

2.2 HS400模式

HS400模式,即高速双倍数据率DDR(Double Data Rate)模式,最高工作频率为200 MHz,最高数据传输速率为400 MB/s。在HS400模式下,使用DAT0-DAT7线同时传输8比特数据,由eMMC设备生成的DS信号控制响应、CRC校验响应以及进行读操作时的数据传输频率;CLK信号控制命令、写操作时的数据传输等频率。

HS400模式仅支持单块读写操作且块大小固定为512 B。进行读写操作的时候,通过DAT0-DAT7数据线进行数据传输。当没有进行数据传输的时候,DAT0-DAT7处于高电平状态。数据传输以块为单位,在每一位数据线上,数据块中数据按先后顺序进行传输,数据块中包括一位开始位(为0)、数据流位、数据的CRC校验位,最后以一位终止位(为1)结束。在HS400模式下,写操作的数据传输同步于时钟信号,读操作的数据传输同步于DS信号,且数据与CRC校验码以DDR模式传输,即数据以每时钟周期两比特数据率传输。

数据块使用的CRC16校验码(每个数据块中有两个CRC16校验码)分别为奇位校验码与偶位校验码。在高速源同步数据传输时,使用CRC校验码可以保证数据传输的正确性与完整性。

3 eMMC控制器设计

3.1 缓存框架设计

完整的设计由六个部分组成,包括eMMC控制器以及若干外围的辅助缓存,如图1所示。eMMC控制器是整个架构的核心,此外,本文在eMMC控制器的外围增加了若干个缓存,进行测试指令以及读写数据的缓存处理。Command_fifo中存放读写指令,指令主要包含操作类型和操作地址两部分。Wr_data_fifo中存放写数据块。指令和数据块由上层模块所给出。Finish_command_fifo中存放已完成的读写指令。Rd_data_fifo中存放读操作所读出来的数据块,完成的指令以及读出的数据由下层模块所确认。当执行指令时,eMMC_controller从Command_fifo中顺序读取指令,执行指令解析操作,完成数据传输并将完成的指令及读出的数据分别放入Finish_command_fifo与Rd_data_fifo中。辅助缓存均由集成开发环境Vivado提供的ip核先进先出FIFO(First In First Out)实例化,FIFO的特点是顺序读出数据,数据地址由内部读写指针自动加1完成。因此,若数据写操作出现错误,需要重新执行该写操作的时候,由于FIFO的特性,将无法从Wr_data_fifo中取得所需数据。因此,本文在eMMC控制器中增加一个512 B的随机存取存储器RAM(Ramdom Access Memory),命名为Write_backup,进行数据写操作的时候,同时将数据备份到Write_backup中,当出现写出错需要重新传输数据时,eMMC_controller选择将 Write_backup中数据写入eMMC相应地址中。

Figure 1 Overall design diagram图1 整体设计框架图

3.2 eMMC控制器模块设计

eMMC控制器执行eMMC设备的初始化操作、模式转换操作以及读写数据传输操作。

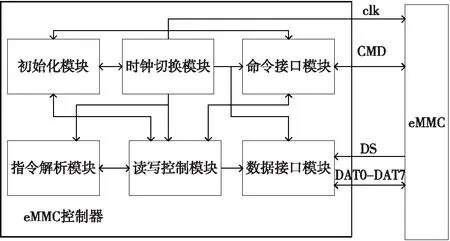

Figure 2 Internal modules of eMMC controller图2 eMMC控制器内部模块

如图2所示,eMMC控制器内部分为六个模块:时钟切换模块、初始化模块、指令解析模块、读写控制模块、命令接口模块以及数据接口模块,各模块协同工作。

3.2.1 时钟切换模块

在eMMC设备初始化阶段与数据传输阶段使用不同的工作频率。初始化阶段要求eMMC控制器的工作频率小于400 KHz;而在进行数据传输的时候,为了提高数据传输速率,eMMC控制器的工作频率最高可达到200 MHz。因此,在设备初始化和数据传输两个阶段,eMMC控制器所使用的时钟频率分别设置为400 KHz与200 MHz,故需要一个时钟切换模块对时钟进行切换。

在eMMC设备上电之后,eMMC控制器以400 KHz的频率对eMMC设备进行初始化操作。当eMMC设备成功进入HS400模式之后,时钟切换模块将时钟频率切换为200 MHz,eMMC控制器根据指令进行数据传输操作。

3.2.2 初始化模块

初始化模块在eMMC设备上电之后首先对设备进行初始化操作,为设备分配相对应的相对设备地址RCA(Relative device address),后续命令根据RCA确定通信设备。初始化操作结束后,配置总线速度模式至HS400模式。初始化操作中所有通信都只使用CMD线,工作频率设置为0~400 KHz。

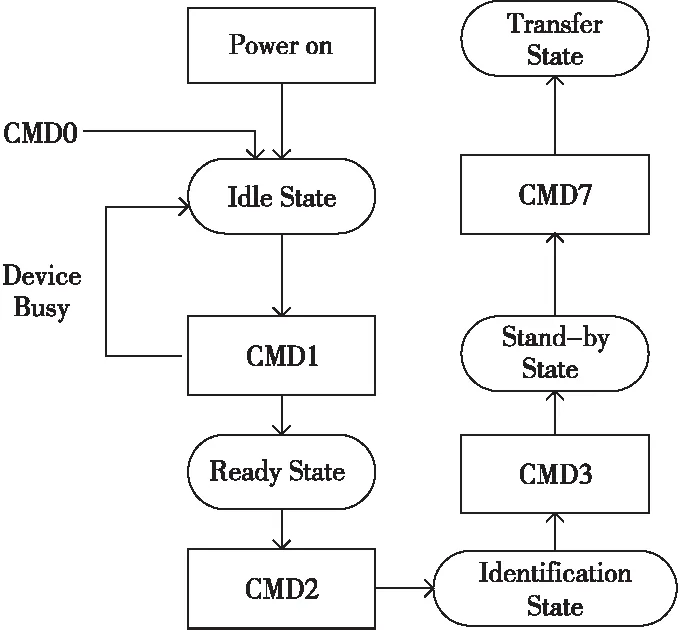

初始化流程图如图3所示,具体操作如下:

(1)Power up至Idle State:eMMC设备上电之后进入Idle State,或者使用命令GO_IDLE_STATE(参数为0x00000000的CMD0)进入Idle State。

(2)Idle State至Ready State:eMMC设备进入Idle State后,发送CMD1(SEND_OP_COND)命令,请求eMMC设备通过CMD线发送OCR(Operating Conditions Register)内容。CMD1响应中有一位为busy位,标志eMMC设备是否还在进行上电复位。busy位为0,上电复位尚未完成,需要一直向eMMC设备发送CMD1; busy位为1,则进入Ready State,只有最后一个CMD1的响应OCR值有效。

Figure 3 Flow chart of initialization图3 初始化流程图

(3)Ready State至Identification State:进入Ready State后,向eMMC设备发送CMD2(ALL_SEND_CID)命令,请求eMMC设备发送其CID号。当eMMC设备成功地向eMMC控制器传送了其CID号后,eMMC设备进入Identification State。

(4)Identification State至Stand-by State:进入Stand-by State后,eMMC控制器向eMMC设备发送CMD3(SET_RELATIVE_ADDR),为eMMC设备分配RCA。一旦eMMC设备接收到RCA后,就进入Stand-by State。CMD2为广播信号,当有多个eMMC设备的时候,一次只有一个eMMC设备成功发送其CID号并被分配RCA。循环发送CMD2与CMD3,直到所有eMMC设备被分配RCA。

(5)Stand-by State至Transfer State:当eMMC设备处于Stand-by State时,通过发送带有eMMC设备RCA参数的CMD7(SELECT)命令选中设备,使eMMC设备进入Transfer State。进入Transfer State后,表示eMMC设备完成初始化操作,可进行传输模式的配置、数据传输等操作。

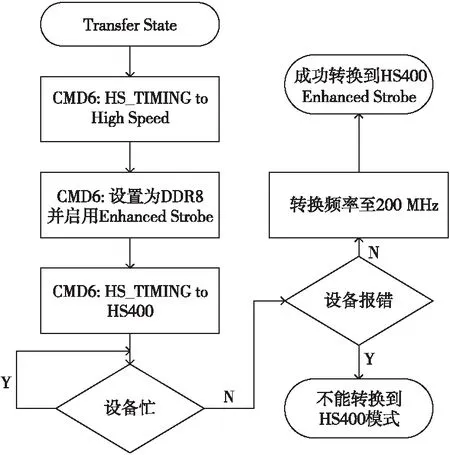

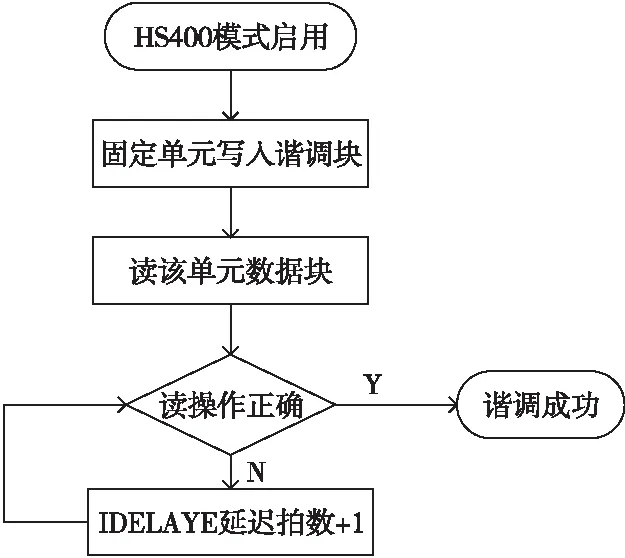

初始化操作后eMMC设备处于默认总线速度模式,即速度模式为 Backwards Compatible Timing。开启HS400模式流程如图4所示,要执行以下步骤:

(1)当eMMC设备经过初始化后处于Transfer State时,发送CMD6(SWITCH)命令配置总线速度模式,设置命令中HS_TIMING参数为0x1,转换为High Speed模式。

(2)当eMMC设备处于High Speed模式后,需要配置数据传输位宽为8比特并采取双数据率传输模式。通过向eMMC设备设备发送CMD6命令对EXT_CSD寄存器中相应内容进行修改,将BUS_WIDTH设置为0x86,即选择双数据率×8总线模式并开启Enhanced Strobe。

(3)设置完成之后,再向eMMC设备发送一次CMD6命令转换数据传输模式,将HS_TIMING设置为0x3,即转换到HS400模式。

(4)成功转换到HS400模式之后,将频率提高到200 MHz,即可进行正常的数据传输。

Figure 4 Flow chart of enabling HS400图4 HS400模式启用流程图

3.2.3 指令解析模块

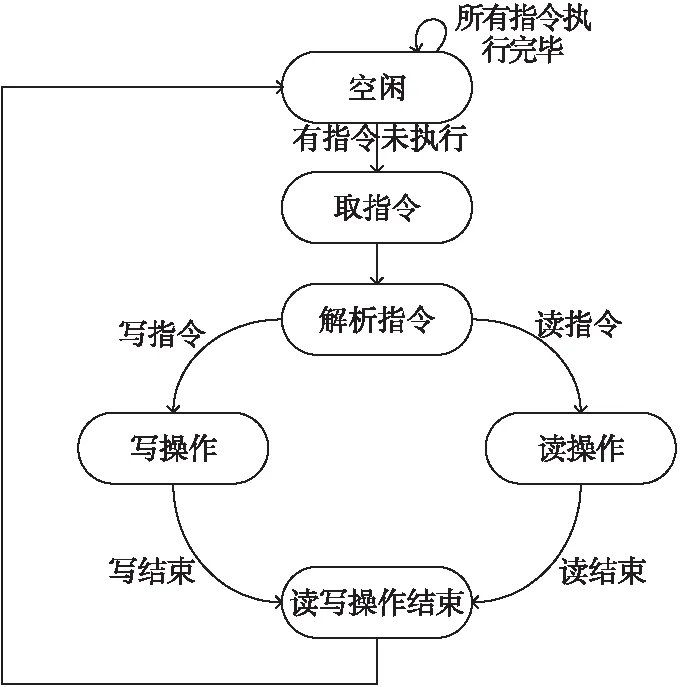

eMMC控制器的指令分为两类:读指令与写指令。每条指令由操作码与操作地址两部分组成。操作码为1位,用0、1分别代表写指令、读指令。操作地址为32位,地址为扇区地址,扇区大小为512 B。一条指令对相应地址的一个扇区进行读或者写操作。

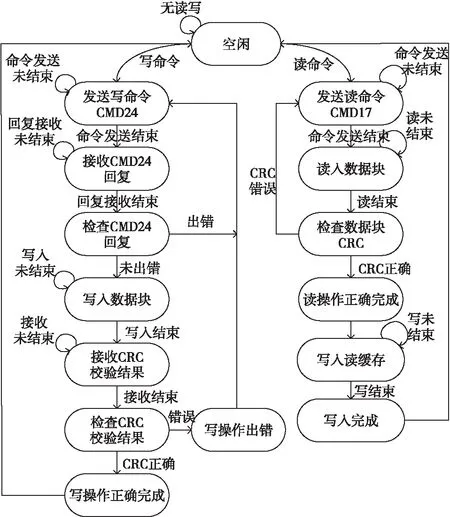

空闲状态下,指令解析模块从Command_fifo中读取一条指令并进行指令解析操作,根据操作码类型,选择进入读或写操作阶段,并构造相应的eMMC设备命令。这时指令解析模块给读写控制模块发送读/写开始信号。读写控制模块开始进行读/写操作,读/写操作完成后向指令解析模块发送读/写结束信号。指令解析模块等待接受读/写结束信号,一旦接收到信号表示该指令读/写操作完成,指令解析模块可准备读取下一条指令。指令解析模块工作状态机如图5所示。

Figure 5 State machine of instruction parsing module图5 指令解析模块状态机

3.2.4 读写控制模块

读写控制模块对eMMC设备进行读写操作。空闲状态下,读写控制模块若接收到指令解析模块发送的读开始信号,则向命令接口模块发送带地址参数的CMD17(READ_SINGLE_BLOCK)。命令发送成功后若数据接口模块经CRC校验接收到正确的数据,则读操作完成,并向指令解析模块发送读完成信号,回到空闲状态继续等待指令解析模块信号;接收到错误的数据则重新发送相同的CMD17命令。

空闲状态下,读写控制模块若接收到指令解析模块发送的写开始信号,则向命令接口模块发送带地址参数的CMD24(WRITE_BLOCK),接着等待命令接口模块返回CMD24响应。一旦接收到响应,则对响应进行检查,响应出错时重新发送原CMD24给命令接口模块,响应正确时由数据接口模块将Wr_data_fifo中一个512 B数据块与其CRC校验一并写入eMMC设备,同时将数据存入Write_backup中备份。数据传输完毕后,数据接口模块返回CRC校验结果,结果错误时重新发送原CMD24并改变此次数据接口模块取数据的来源,使数据接口模块从Write_backup中读取备份数据。CRC校验正确时,eMMC控制器等待eMMC设备完成写操作后返回空闲状态。读写控制模块的工作状态机如图6所示。

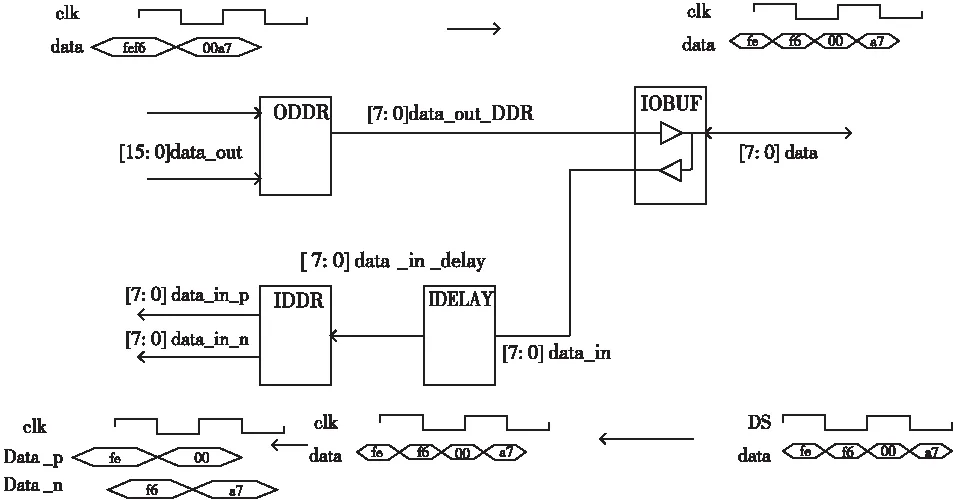

在HS400 Enhanced Strobe模式下,如图7所示,eMMC设备向FPGA传输的数据是与DS信号边沿对齐的,而数据进入FPGA内后是由时钟切换模块产生的200 MHz时钟采集的,由eMMC 5.1协议所知,数据与时钟是中心对齐的。高速模式下,时钟与数据关系不确定,不能保证时钟和数据中心对齐,因此可能会导致最后采集的数据出错。本文的设计使用IDELAY原语对时钟和数据进行调谐,使时钟和数据中心对齐,确保能采集到正确的数据。

Figure 6 State machine of read and write图6 读写控制状态机

Figure 7 Data interface design图7 数据接口设计

调谐操作在eMMC设备初始化操作并启用HS400 Enhanced Strobe模式后进行,时钟切换模块将CLK信号转换为读写工作频率进行调谐操作。调谐成功后即可进行正常读写操作。调谐操作的原理是先向eMMC设备的一个固定保留地址写一块数据,之后不断读取该地址中的数据,根据CRC校验结果判断是否读操作出错。如果读出错,将IDELAY的延迟数增加1,否则保持当前延迟数目不变,此时认为时钟和数据中心是对齐的。具体调谐流程如图8所示。

Figure 8 Flow chart of tuning图8 调谐流程图

3.2.5 命令接口模块

命令接口模块功能为根据指令解析模块发来的命令构造CMD命令,并将其发送给eMMC设备;接收、解析eMMC设备的响应并发送给读写控制模块。

在命令发送过程中,命令接口模块会对命令进行CRC7校验码的计算。指令解析模块传送给命令接口模块相应40位命令,命令接口模块计算出40位命令的CRC7,与40位命令、结束位一起构成48位的CMD命令发送给eMMC设备。

3.2.6 数据接口模块

数据接口模块的主要功能是将Wr_data_fifo或Write_backup中数据写入eMMC设备相应地址中以及将eMMC相应地址中数据块写入Rd_data_fifo中。

采用HS400总线速度模式,该模式使用DDR方式传输数据,即每根数据线在时钟上升沿和下降沿分别传输一位数据。因此,在200 MHz工作频率下,eMMC控制器可达到400 MB/s的数据传输率。

数据接口如图7所示,每根数据线上数据经过IOBUF、ODDR、IDDR、IDELAY原语处理。其中IOBUF选择输入输出数据; IDDR、ODDR分别处理输入输出的DDR数据;IDEALY对输入进行调谐操作[5]。

进行数据写操作的时候,FPGA需要向eMMC设备输出DDR数据,16位的输出数据data_out通过ODDR之后在时钟的上升沿和下降沿分别传输8位数据,并通过IOBUF写入eMMC设备。在进行数据读操作的时候,eMMC设备向FPGA通过IOBUF传输DDR数据,由3.2.4节所知,此时数据经过IDELAY使用IDDR原语进行处理,使得数据与时钟中心对齐。数据通过IDDR分离成两路单倍速率的数据。data_in_p为上升沿所采数据,data_in_n为下降沿所采数据。

进行数据写操作的时候,数据接口模块会对数据进行CRC16校验码的计算。数据接口模块计算取出的512 B数据的CRC16校验码,分别对奇位数据与偶位数据算出CRC16校验码。将数据与计算出的奇偶CRC16校验码、开始位、结束位组成一个数据块,由数据接口模块写入eMMC设备中。进行数据读操作的时候,数据接口模块会对接收到的数据块进行CRC16校验,如果CRC校验通过则读操作正确,将512 B数据位读入Rd_data_fifo;否则表示读操作不正确,返回错误信号给读写控制模块,要求对该数据块进行重读。数据的传输与CRC16校验码的计算同时进行,因此校验码的生成与检验不影响数据传输的速率。

4 实验评估

本文使用母板/子板架构,在Zedboard开发板(母板)上实现eMMC控制器,并定制一个eMMC的FMC子板。控制器通过FMC接口传输信号,对eMMC芯片进行操作。

本文用Verilog硬件描述语言[6,7]设计实现eMMC控制器,使用Vivodo 2015.4集成开发环境进行综合实现[8],在综合后添加debug核,抓取真实工作情况时的数据接口的信号,以观察在开发板上运行时的真实信号波形。

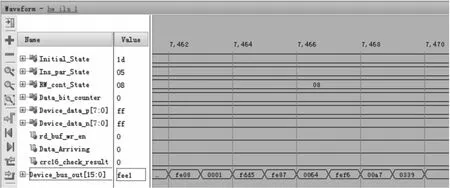

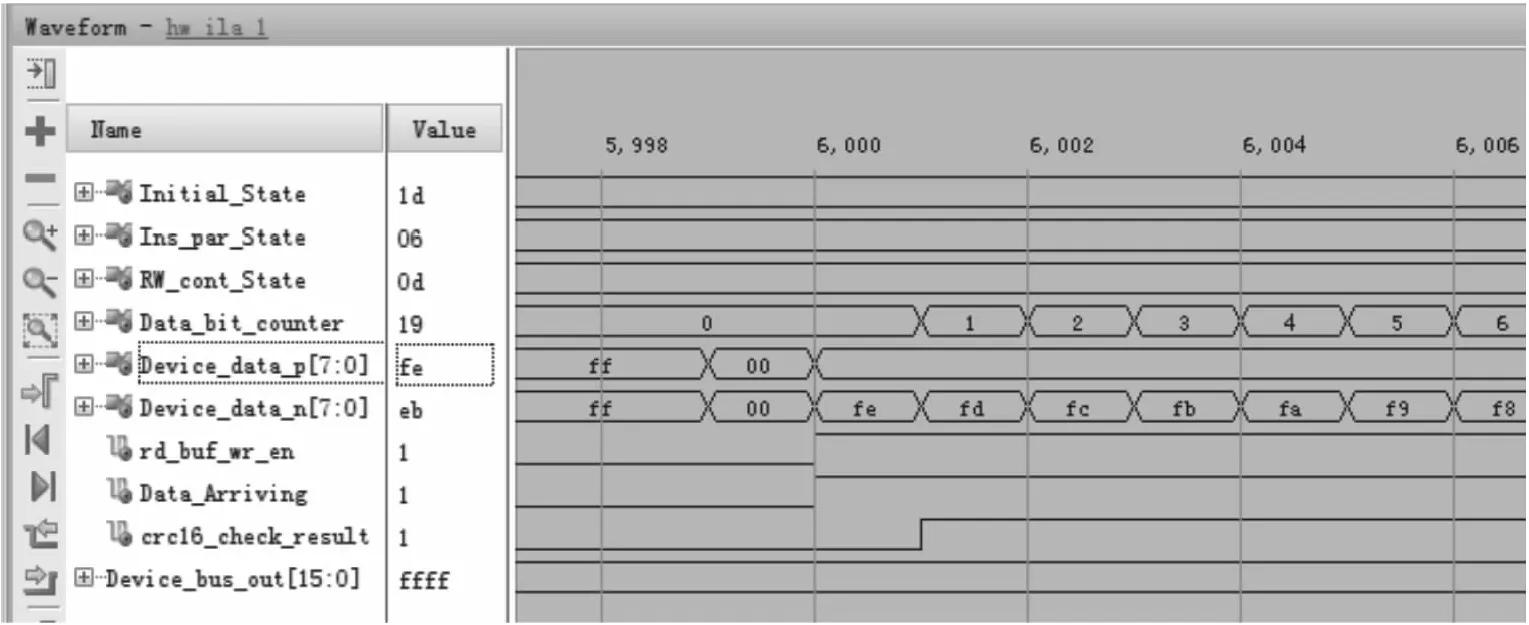

测试采用200 MHz时钟频率,通过在Command_fifo中存入指令对设计进行测试,观察执行读写指令时部分关键信号。Initial_State、Ins_par_State、RW_cont_State分别为初始化、指令解析、读写控制状态机当前状态。Device_data_in_p与Device_data_in_n为从eMMC设备中读取的数据块的高八位与低八位,Device_bus_out为写入eMMC设备的数据块。Data_Arriving、rd_buf_wr_en与crc16_check_result为读操作时的部分控制信号,Data_Arriving为1时表示eMMC设备正在向数据接口发送数据块,包括数据位和CRC校验码部分;rd_buf_wr_en为1时表示将此时读取的数据为数据位部分,数据存入Rd_data_fifo中;crc16_check_result为CRC校验结果,此值为1时表示校验结果不正确,此值为0时表示正确,校验结果在数据传输结束后一个周期有效,即Data_Arriving由1变0时第一个周期有效。

写指令时,发送CMD24且eMMC设备正确响应进入数据接收状态后,eMMC控制器向eMMC设备发送数据,如图9和图10所示,开始位(Device_bus_out为0000)后发送数据位512 B,之后发送奇偶CRC16校验码,最后以结束位结束,Device_bus_out为写入数据。当eMMC设备返回CRC校验响应为出错时,说明数据在传输过程中出错,eMMC控制器将重新执行该写指令,直到eMMC设备返回CRC校验通过。

Figure 9 Write start of a data block图9 数据块写开始

Figure 10 Write end of a data block图10 数据块写结束

Figure 11 Read start of a data block图11 数据块读开始

Figure 12 Read end of a data block图12 数据块读结束

读指令时,读取上一写指令写入数据。如图11所示,发送CMD17后,等待若干周期,开始位之后(Device_data_in_p与Device_data_in_n分别为00),eMMC设备发送数据给eMMC控制器,Device_data_in_p与Device_data_in_n为读出数据。在数据位开始传输时,Data_Arriving、rd_buf_wr_en控制信号同时为1,表示开始传输有效数据。

当512 B数据位传输完毕后,rd_buf_wr_en变为0,表示此时数据块中数据位传输完毕,开始传输CRC16校验码。

最后,如图12所示,CRC16校验码传输完毕后Data_Arriving变为0,表示数据块部分传输完毕,CRC16校验结果在数据传输完毕后一周期由crc16_check_result给出,此值为0表示校验通过,数据传输正确,否则表示CRC校验不通过,数据传输出错,eMMC控制器将重新执行该读指令,直到读取正确的数据。

5 结束语

本文基于eMMC接口协议设计了一个高可靠性、高性能的eMMC控制器。eMMC控制器可对多个eMMC设备进行初始化并激活HS400模式,在HS400模式下进行数据的读写,并通过CRC校验完成对传输错误的数据的重写或重读,保证数据传输的正确性与完整性。通过激活HS400模式和DDR接口,数据的传输率可高达400 MB/s。我们使用Verilog硬件描述语言在Vivado集成开发环境中编写eMMC控制器,在Zedboard母板及eMMC子板上实现。通过设计指令对eMMC控制器功能进行测试,验证了设计的正确性与可行性。

[1] Embedded multi-media card(eMMC) electrical standard(5.1):Jedec Standard: JESD84-B51[S].2015-02-01.

[2] Zhang Yao-hui, Sun Ming,Wang Jian. eMMC controller design based on Virtex-6 FPGA[J].Microcontrollers & Embedded Systems,2016,16(2):10-13.(in Chinese)

[3] Xilinx Inc. Xilinx introduces ultra fast design methodology for Vivado design suite[EB/OL].[2017-12-10]. http://news.cision.com/xilinx/r/xilinx-introduces-ultrafast-design-methodology-for-vivado-design-suite, C9487458.

[4] Liu Chang-peng. Digital logic circuit[M]. Beijing:Higher Education Press,2010.(in Chinese)

[5] Xilinx Inc. 7 Series FPGAs selectIO resources user guide[M].San Jose:xilinx Inc, 2015.

[6] Xia Yu-wen. Verilog digital system design tutorial[M]. Beijing:Beihang University Press, 2008.(in Chinese)

[7] Pan Song, Huang Ji-ye, Chen Long. EDA technology and Verilog HDL[M]. Beijing:Tsinghua University Press, 2008.(in Chinese)

[8] Xilinx Inc. Vivado design suite user guide-HLS[M]. San Jose:xilinx Inc, 2013.

附中文参考文献:

[2] 张耀辉,孙铭,王锏.Virtex-6 FPGA的eMMC控制器设计[J].单片机与嵌入式系统应用,2016,16(2):10-13.

[4] 刘常澎.数字逻辑电路[M].北京:高等教育出版社,2010.

[6] 夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2008.

[7] 潘松,黄继业,陈龙.EDA 技术与Verilog HDL[M].北京:清华大学出版社,2008.