基于ZYNQ7000的低功耗软件无线电平台设计

尹志伟 程亮亮

摘 要:文章针对专用无线通信系统中低功耗的应用需求,给出一种新的软件无线电处理平台的硬件设计方案。该平台满足软件无线电的设计要求,采用Ⅺlinx公司的ZYNQ7000架构处理器,通过外设器件型号优选,实现具有高性能、功耗较低的软件定义无线电硬件平台,且已在工程项目中成功应用。

关键词:无线通信;软件无线电平台;低功耗:ZYNQ7000

传统的软件无线电处理平台一般采用GPP+DSP+FPGA的通用架构,3种异构处理器分别实现不同的功能,如图1所示。

其中ARM负责主控功能,实现平台的中心控制、有线接口协议、无线通信协议等;DSP为波形物理层的核心,实现波形接入控制、基带信号的编解码、交织解交织、调制解调等;FPGA主要负责信号的上下变频、窄带译码等功能[1]。

传统的多芯片架构存在问题:单板功耗高,布板面积大。而目前无论是军事应用还是民用专业电台应用,均对小型化、低功耗的需求日趋强烈,与此同时,随着应用软件对硬件平台的处理性能的不断提高,高性能与小体积、低功耗已经成为处理平台的基本要求,而传统的数字硬件平台设计方式越来越难以满足这一需求[2]。

本文给出了一种基于ZYNQ7000架构SoC的软件无线电处理平台设计方案,并分析和论证了低功耗设计的思路。

1 硬件架构设计

SoC目前是处理器发展的趋势,ZYNQ7000是Xilinx公司发布的双ARM内核+FPGA架构的SoC。该系列芯片采用28 nm工艺,具有高性能、低功耗等优点,而且该系列芯片具有不同处理性能型号,可满足不同类型的产品需求。其中,部分型号具有可兼容封装,可以在不更改电路设计的情况下实现产品硬件的升级。

我们选用ZYNQ7000作为新一代数字平台的核心处理器。基于ZYNQ7000的平台基本架构如图2所示。

图2基于ZYNQ7000的数字平台架构

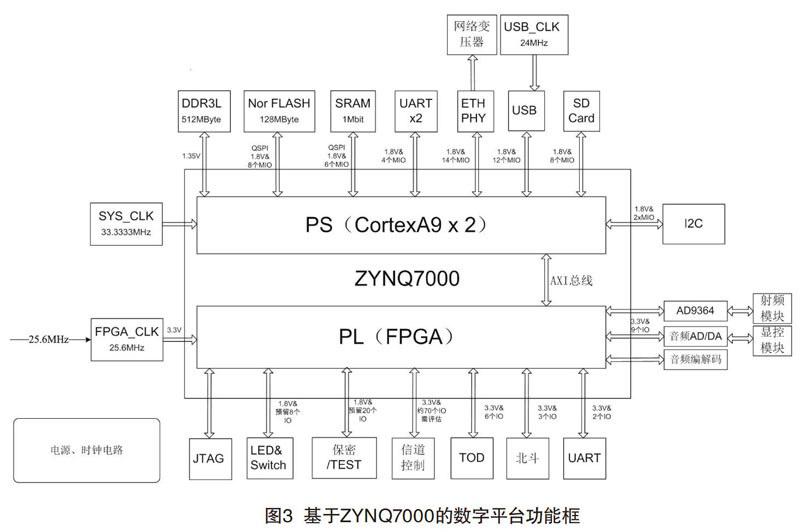

ZYNQ7000的ARM核负责主控、接入等功能,FPGA负责物理层,ARM与FPGA之间的图中配合ZYNQ7000的是高集成度的收发芯片,该类芯片具有ADC,DAC,混频、滤波、增益控制等功能,便于降低平台的功耗和布板尺寸。

结合新一代VHF/UHF的基本需求,我们设计了相应的功能原理框图,如图3所示。

2 器件选型

器件选型在是小型化、低功耗设计的关键环节,选型原则是:在满足产品需求的情况下尽可能选用低容量、低频率、低电压、低功耗的器件。

2.1 ZYNQ7000选型

ZYNQ7000系列芯片有多种型号,每种型号对应不同的性能,不同型号的ZYNQ7000芯片的ARM核差别不大,主要区别在于最高主频的不同。在低功耗设计中应尽可能选用速的型号,这样对应的功耗相对较低。

LS部分资源的选择基于软件的需求,在满足软件需求的前提下,选用资源最少的型号,这样芯片的静态功耗相对较低。为了方便硬件升级改造,尽量采用可兼容不同型号的封装。

除此之外,厂家针对某些型号提供了经过低功耗筛选的型号,例如对应XC72030-2的低功耗型号为XC72030-2L,该低功耗型号的芯片与原型号相比可降低15%功耗。

2.2 DDR选型

DDR的类型很多,从DDR1到DDR4,每一代都会有不同的工作電压方式,不同形态对应的功耗不同,而ZYNQ7000支持LPDDR-2 (1.2 V)、DDR2 (1.8 V)、DDR3 (1.5 V)、DDR3L (1.35 V)4种类型。其中LPDDR-2工作电压最低,功耗也最低,与DDR3相比至少可降低0.4 W的功耗。选型原则:尽量选用低容量、低电压、低数据率的型号。

2.3 ADC和DAC

ADC和DAC的选型对数字平台的功耗影响很大,因为该部分的电路设计会影响到时钟芯片的选型和功耗,所以需要重点考虑。

传统的数字平台架构中,中频收发链路通常采用分离的ADC和DAC。DAC-般选用带混频的芯片,对于140 MHz的中频而言,DAC芯片功耗一般不低于0.3 W,ADC功耗也在0.2 W左右。除此之外,电路中需要提供相应的时钟电路,为了保证采样信号质量和采样频率,需采用低抖动的具有倍频功能的时钟芯片,这类时钟芯片的功耗一般都在0.5 W以上。这种方案ADC和DAC相关的功耗至少需要1W。

为了降低单板功耗,可选用高集成都的中频收发芯片,该类芯片自带锁相环,ADC,DAC,混频等功能,对于140 MHz的中频信号而言,其功耗不高于0.5 W。

2.4 Flash

ZYNQ支持的FLASH类型有:并行NorFlash,NandFlash,QSPI- Fla sh,其中QsPI- Fla sh连接管脚数最少,对于处理器而言,IO管脚带来的功耗也最少,因此优选QSPI-Flash。

目前主流的QSPI-Flash有+3.3 V供电和+1.8 V供电两种类型,为了进一步降低功耗,应选用+1.8 v供电的型号。

2.5缓冲器

缓冲器有很多功能,如电平转换、增加驱动能力、数据传输的方向控制等,当仅仅基于驱动能力的考虑增加缓冲器时,必须慎重考虑,因驱动电流过大会导致更多的能量被浪费掉。所以应仔细检查芯片的最大输出电流是否足够驱动下级芯片,当可以通过选取合适的前后级芯片时应尽量避免使用缓冲器。

2.6上下拉电阻

从节约功耗及芯片的倒灌电流能力上考虑,上拉电阻应足够大,以减小电流;从确保足够的驱动电流考虑,上拉电阻应足够小,以增大电流;在高速电路中,过大的上拉电阻会使信号边沿变得平缓,信号完整性会变差。

因此,在考虑能够正常驱动后级的情况下,尽可能选取更大的阻值,以节省系统的功耗。对于下拉电阻,情况类似。

2.7接口芯片

对于设备中的各种外设,如网口、USB口、RS2332串口等,要进行各种型号的功耗对比。尽可能选用厂家最新的型号,新型号一般会采用较新的工艺,相应的功耗也会较低。

3 供电设计

3.1供电方式

传统的背负式电台一般采用集中供电的方式,电台中的各功能模块统一由直流电源模块供电,这种方式适用于车载设备等对体积功耗不敏感的应用场景。对于背负、手持等电池供电的设备而言,集中供电效率较低,且电流在传输线上的压降也会比较大,功率损耗高。

为了提高电源电路的转换效率,在小型化、低功耗设备中应采用分布式电源供电。分布式供电具有以下优点:可靠性高,转换效率高,电压稳定性好,电磁兼容和安全性可以方便实现,并可易于设计分时启动、电源功耗控制。

除此之外还应该注意,尽量都选用以此转换,避免多次转换,提高电源效率。并且在设计时,同一个电源电压尽可能共用一个芯片,减少电源芯片的使用量。

3.2电源电路设计

由于采用双ARM+FPGA架构,且有多种外设,数字平台需要多种电源电压。仅以ZYNQ7000来说,就需要0.95 V、1.8 V和3.3 V电压,因此需要很多电压变化单元。通常,有以下几种电压变换方式:线性调节器;DC-DC;低漏失调节器(Low Dropout Regulator, LDO)。其中LDO本质上是一种线性稳压器,主要用于压差较小的场合,所以将其合并为线性稳压器。

线性稳压器的特点是电路结构简单,所需元件数量少,输入和输出压差可以很大,但其致命弱点是效率低、功耗高,其效率完全取决于输出电压大小。

而DC-DC电路的特点是效率高、升降压灵活,缺点是电路相对复杂,纹波噪声干扰较大,体积也相对较大,价格也比线性稳压高,对于升压,只能使用DC-DC。

因此,关于电源选型,需主要以下几点:(1)对于电源纹波噪声要求不严的情况,尽量用轻载高效型的DC-DC,提高DC-DC在轻载和重载时的效率,降低损耗。(2)用DC-DC可以提高效率,但是干扰相对大一些。要考虑DC-DC对外界的干扰,如开关信号走内层降低干扰等。(3) DC-DC设计时,电感选型要注意,要选择DCR较小并且磁损耗较少的电感,提高电源效率。(4)电池供电产品,通常要做防反接,也有可能做防高压设计,如果用二极管,尽量用压差较小的肖特基二极管。(5)如单板内用到MOS管,尽量用Rdson小的MOS管,降低MOS管损耗。

4 动态电源管理

动态电源管理是指在系统运行期间通过对系统的时钟或电压的动态控制来达到节省功率的目的,这种动态控制与系统的运行状态密切相关,该工作往往通过软件来实现。主要可从以下几个方面进行考虑:(1)设计设备的待机状态模式,该模式需要保证在可以快速启动设备的前提下,尽可能关掉各功能电路的电源,使功耗降到最低。(2)根据软件对硬件资源的使用情况,实时调节主芯片工作频率、逻辑资源的占用、功能电路的状态等,使工作模式下功耗尽可能最低。(3) DDR在待机状态下,尽可能处于自刷新状态,或是关掉DDR芯片电源,此时无法热启动。(4)关闭空闲的外设控制器和外设。做驱动设计时,要关掉主芯片没有用到的所有模块,降低功耗。如没有用USB,那就关掉USB模块。(5)前面板的显示频在不用时,尽量关掉。

5 结语

随着芯片技术的发展,在手持式、背负式专军用通信电台中,低功耗设计会成为一个越来越迫切的问题。随着一些新技术的出现并应用于相关的设计中,例如先进的电源管理芯片、先进的处理器,给设计者提供了更大的灵活性,可以大大降低数字平台的功耗。

[參考文献]

[1]张剑锋基于认知无线电的电台架构研究[J].软件,2011(5):56-58

[2]李涛龟台自动测试与分析系统的设计与实现[D].济南:山东大学,2012.