SoC系统超低功耗设计方法*

杨瑞瑞,何 涛,唐伟文,范伟力

(成都三零嘉微电子有限公司,四川 成都 610041)

0 引 言

在集成电路发展的历史上,通过单纯在工艺上减小器件尺寸和降低工作电压来降低功耗已经发挥了很大作用。当前,器件尺寸和工作电压已经逐渐接近其物理极限。随着工艺技术的不断进步和电路集成的不断提高,功耗已经开始成为纳米设计领域面临的最严峻挑战。

1 SoC系统功耗概述

由图1可以看出,在0.18 μm以上工艺中,漏电功耗的影响很小,同动态功耗比可基本忽略。但是,到了65 nm工艺,漏电功耗已占到总功耗的35%~55%。当工艺下降到45 nm及以下工艺时,漏电功耗甚至可以占总功耗的一半[1]。可见,在此阶段的超深亚微米工艺SoC设计中,漏电功耗是继动态功耗之后的另一主要设计因素,而功耗的优化已成为设计者在设计初期必须面对的挑战之一。

图1 不同工艺下功耗组成

按照理论公式,动态功耗[2]为:

其中f是系统工作频率;A是跳变因子,即整个电路的平均翻转比例;C是门电路的总电容;V是供电电压;τ是电平信号上升/下降的时间;Pswitch是跳变功耗,是器件在工作过程中对电容充放电形成的;Pshortcircuit是短路功耗,是器件在工作时由电源到地形成的通路造成的。可见,降低动态功耗的主要方法是降低工作电压、降低负载电容、降低开关活动性和降低时钟频率。

降低芯片静态功耗的方法和动态功耗完全不同。芯片工作在休眠模式时,芯片内部时钟停止,门电路不发生翻转,只有漏电流产生。静态功耗为:

其中Panolog是SoC芯片中模拟电路部分的功耗;Pdigital是数字内核部分的静态功耗;Ppad是芯片管脚不工作时的静态功耗。

2 动态功耗优化方法

本章介绍流水线设计、存储器分块访问、无复位端DFF寄存器的使用、系统时钟门控以及后端物理低功耗实现等降低系统动态功耗的方法。

2.1 模块低功耗设计方法

2.1.1 流水线设计

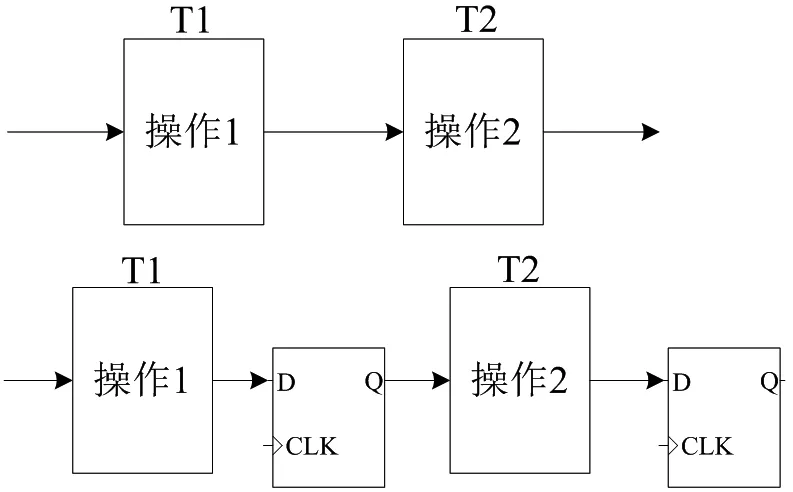

流水线技术是把规模较大、层次较多的组合逻辑电路分为几个级,在每个级插入寄存器组暂存中间数据。K级的流水线是从组合逻辑的输入到输出有K个寄存器组,上一级的输出是下一级的输入而又无反馈的电路。

如图2所示,无流水线操作时,经过操作1和操作2,所需要的时间为(T1+T2);在操作1和操作2之间插入流水,单级处理需要的时间为MAX(T1,T2)。若想二者达到相同的数据处理速度,无流水处理和有流水处理需要工作时钟频率比为(T1+T2)/MAX(T1,T2)。可见,流水线可以有效降低工作频率,从而降低动态功耗。但需要注意,流水线技术需要插入寄存器,增加了面积,需要额外的时钟驱动。因此,使用时应权衡得失灵活选择。

图2 流水线设计

2.1.2 存储器分块访问技术

存储器分块访问技术是将系统所需要一定容量的存储器分成多块,然后用高位地址线进行片选译码,使得每次对于RAM的操作节省了至少一半的访问空间,而仅一半容量的RAM工作功耗远小于一整块RAM的功耗,不仅降低了数字集成电路的功耗,而且提高了系统指令的执行速度。

2.1.3 无复位端寄存器

电路设计中,有些寄存器如用作临时存储的寄存器、数据传输寄存器等,根据功能需求对上电初始化时的初始值无要求,可以使用无复位端的DFF寄存器减小动态功耗的开销。

2.2 系统时钟门控设计方法

系统时钟门控是将系统中不工作模块的时钟从根部实现时钟门控,最大限度降低系统功耗。如图3所示,系统由模块A/B/C组成,时钟根部节点由各自门控单元给出,模块内部是独立的时钟树网络。若其中有模块不需要参与工作,将整个时钟树关闭,最大限度降低时钟路径的功耗和无效翻转。

2.3 物理综合实现低功耗策略

2.3.1 公因子提取

在逻辑综合中,公因子提取是简化逻辑网络、降低电路实现成本的常用方法。一个函数通过化简变形可以得到多种表达式,可以采用不同的逻辑结构实现同一个函数。不同逻辑结构的实现虽然可能在面积和时序上差别不大,但由于各个输入信号的翻转率不同,可能导致电路的功耗差别较大。因此,设计电路时,应该使翻转率较高的信号驱动的负载尽量少,也就是使这些信号靠近输出端,即经过的器件尽量少。例如,函数F=ab+ac+cd,其中a的翻转率假定为80%,信号b、c、d的翻转率均为20%。a的活动性更强,对函数F进行化简,使a尽量处在靠近输出端的位置,即提取公因子a,化简后的函数为F=a(b+c)+cd。信号少经过一个与门,减少了电路翻转,降低了功耗,提高了电路的稳定性,如图4所示[3]。在综合时,通过读入典型应用模式下的翻转波形,获得信号的翻转率,由综合工具自动优化实现这一目的。

图3 系统时钟门控

图4 公因子提取

2.3.2 逻辑时钟门控

门控时钟的设计方法是在寄存器处增加一个使能端。当使能有效时,时钟正常工作;当使能无效时,时钟保持固定电平,将电路中的一部分时序单元空闲下来,达到减小功耗的目的,如图5所示。在综合时,通过加入门控时钟的选项实现这一目的。

图5 逻辑时钟门控

2.3.3 低功耗综合脚本

在后端设计时,通过加入以下约束语句,实现低功耗物理综合的目的。

/读入典型应用模式下的saif波形,获得信号的翻转率/

read_saif -input work.saif -instance top

/设置动态功耗和静态功耗优化/

set_dynamic_optimization true

set_leakage_optimization true

/设置门控时钟的风格,使用基于锁存器的门控单元,上升沿触发的寄存器使用GCKESFB8LERMX6门控单元,下降沿触发的寄存器使用GCBESFB8LERMX6门控单元,对宽度大于等于8的寄存器阵列设置门控,门控单元驱动最大不超过64/

set_clock_gating_style-sequential_cell latchminimum_bitwidth 8-max_fanout 64 -positive_edge_logic{integrated:GCKESFB8LERMX6}-negative_edge_logic{integrated:GCBESFB8LERMX6}

/打开时钟门控和深度self_gating门控选项/

compile_ultra-gate_clock-self_gating

3 静态功耗优化方法

3.1 数字内核静态功耗优化

数字内核部分的漏电功耗产生的主要来源是亚阈值电流、栅极电流以及源漏区反偏二极管电流[3]。降低内核静态功耗的主要方法是多阈值电压技术和电源关断技术。

3.1.1 多阈值电压技术

多阈值电压技术基于这一原理:低阈值电压(LVT)单元漏电流较大,但工作频率高、速度快;高阈值电压(HVT)单元漏电流较小,但工作频率低、速度慢。

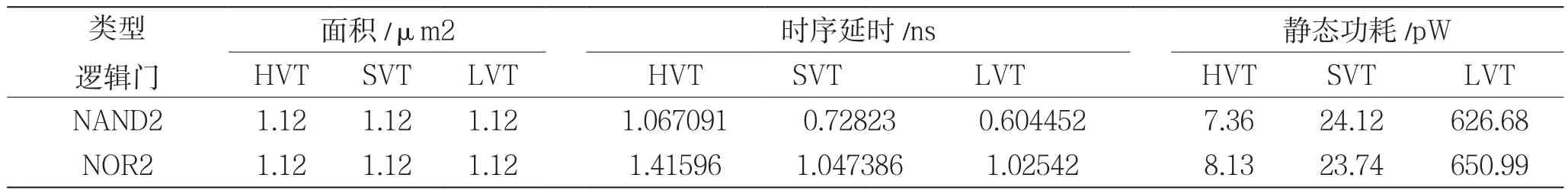

物理设计工具充分利用这些库对设计的时序和功耗同时进行优化,因而多阈值电压技术的基本方法是:在时序关键路径上使用RVT和LVT单元来满足时序要求,在非时序关键路径上使用RVT和HVT单元来满足漏电功耗最小化。表1以SMIC 55nm LL工艺库NAND2(二输入与非门)和NOR2(二输入或非门)在TT环境下为例作比较[4]。

表1 逻辑门在三种阈值下面积、时序和功耗比较

由表1可以看出,NAND2和NOR2逻辑门在3个阈值下面面积是相同的,时序在LVT下面最优,在HVT下面最差;相反地,逻辑门在HVT库静态功耗最小,在LVT库中静态功耗最大。在后端物理综合时,通过低功耗约束手段在非关键路径使用高阈值和标准阈值的门单元,降低数字内核的漏电功耗。

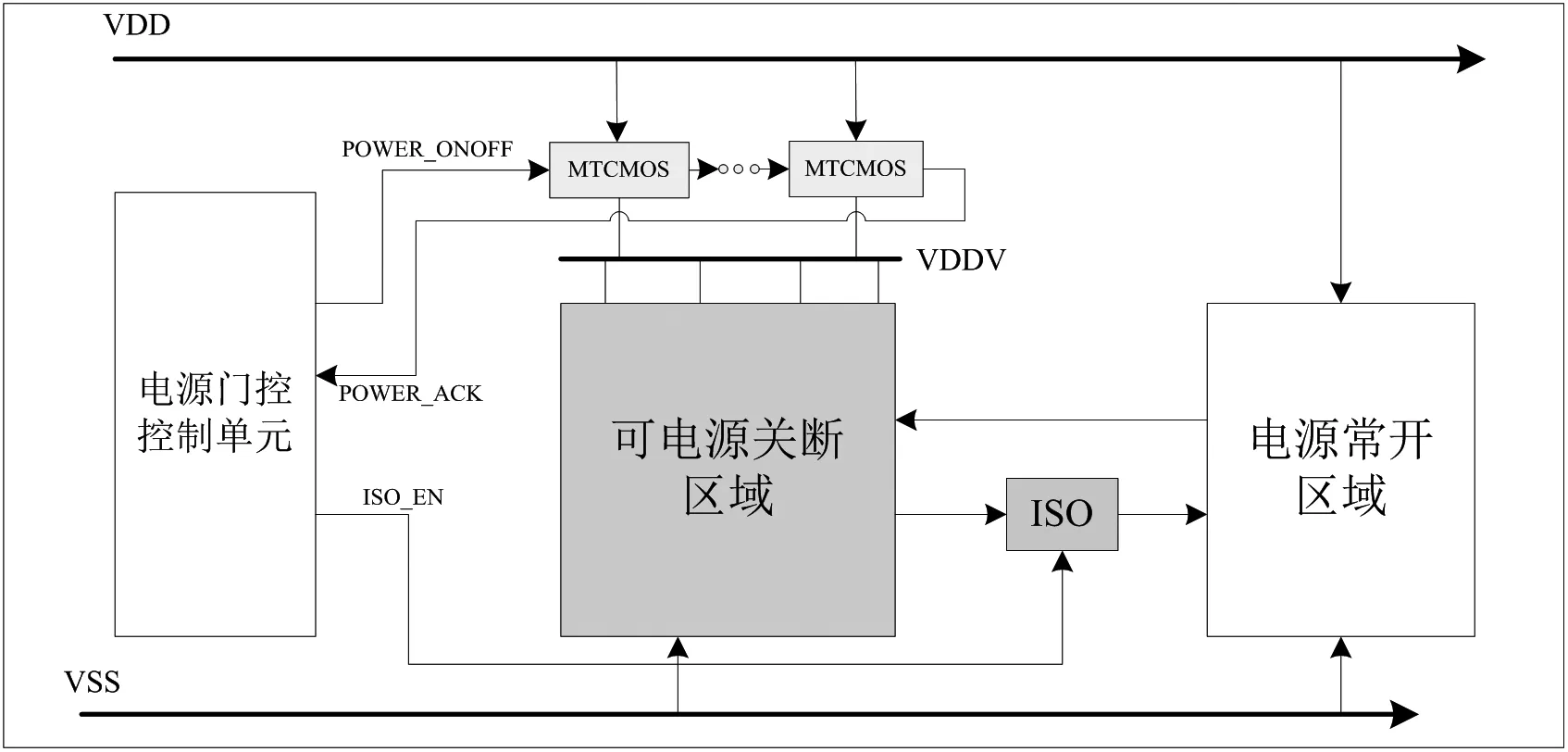

3.1.2 电源门控技术

电源门控技术是把处于休眠模式状态的模块供电电源关断,选择性地关断芯片中某些模块的供电而保持其他模块的正常供电,将处于非工作状态模块的电源关断以节省漏电功耗。

图6 电源门控组成部分

具体实现组成部分如图6所示。电源门控控制单元负责控制电源关断区域的掉电和上电过程,保障掉电和上电不对其他功能区域造成影响;VDD/VSS是供给整个系统的电源地,MTCMOS单元是用来控制VDDV和VDD的通断开关单元。输入关断区域的信号不需要隔离处理,从关断区域输出的信号需要加入隔离单元,即从掉电区域输出的信号固定为“0”或者“1”,不影响其他模块的正常工作。

电源门控实现的过程为:首先门控控制单元使能ISO_EN信号有效,将输出信号钳位在高电平或者低电平,然后将POWER_ONOFF信号拉低,MTCMOS单元逐级断开VDDV和VDD的连接,POWER_ACK信号返回低电平,完成电源关断。上电过程为:首先将POWER_ONOFF信号拉高,MTCMOS逐级打开VDDV和VDD的连接,POWER_ACK信号返回高电平,完成关断区域的电源上电,然后再将ISO_EN信号拉低,隔离撤离,完成区域上电。

3.2 管脚PAD静态功耗优化

SOC芯片系统中,一般有几十甚至上百个数字管脚。数字管脚的类型可以分为上拉PAD、下拉PAD和无上下拉PAD。系统使用中,为了使电路工作的状态默认正确,使用许多上下拉PAD。图7是上拉PAD示意图,图8是下拉PAD示意图,上下拉电阻的阻值一般为30~50 kΩ。

图7 上拉PAD

图8 下拉PAD

如图7所示,假设上拉PAD管脚由于外部输入低电平或者作为输出时输出低电平,那么在PAD上会形成一个导通电流。以47 kΩ计算,导通电流为70 μA。同样地,如图8所示,下拉PAD由于外部输入高电平或者作为输出时输出高电平,那么在PAD上同样形成一个导通电流。以47 kΩ计算,导通电流同样约为70 μA。因此,使用上下拉PAD管脚时,在休眠模式,若由于管脚电平状态与上下拉模式不一致,会产生约为60~70 μA的导通电流,即存在一个这样的导通电流,静态低功耗设计将功归一篑。因此,注意选择上下拉PAD与休眠模式状态电平的一致性。

3.3 模拟器件静态功耗优化

首先,模拟器件有工作模式和休眠模式两种模式。系统应用时,需要数字电路配合在系统进入休眠状态时,将模拟电路切换为休眠模式,仅产生最小的漏电流。有些模拟IP具备深度休眠模式,模式切换时需要进入深度休眠模式。

另一种方法,即当模拟电路比较大,即使切换为休眠模式产生的漏电也不可无视,在系统设计时,将模拟电路的外部供电与其他部分分开供电,当应用场景不使用该部分模拟电路时,将该部分电路实现外部电源关断,完全不产生静态功耗。

3.4 静态功耗的变化

在深亚微米工艺下,漏电流随着工作环境的变化如电压、温度,其漏电流值呈现数量级倍数的增长。下面以SMIC 55nm LL工艺库NAND2(二输入与非门)和NOR2(二输入或非门)为例说明[4],如表2所示。

从表2看出,电压、温度对漏电流的影响非常大,尤其在二者一起变化时,漏电流呈现数量级的变化。

表2 逻辑门在不同环境下漏电功耗比较 /μW

4 结 语

本文介绍了在深亚微米工艺下,通过在模块设计、系统设计以及后端实现过程中采用的低功耗设计方法,基于文中阐述的相关低功耗设计方法和措施,将其成功应用于某款“核高基”超低功耗芯片,使用工艺为SMIC55nm LL。经第三方测试机构测试证明,SoC芯片的动态功耗和静态功耗相比不引入低功耗设计策略均明显降低,在手机、平板等手持设备上面具有广泛的应用。

参考文献:

[1] 张志敏,常晓涛.SOC低功耗设计技术发展综述[DB/OL].(2014-10-01)[2017-12-22].http://www.doc88.com/p-9085745880233.html.ZHANG Zhi-min,CHANG Xiao-tao.Overview of the Development of SOC Low Power Design Technology[DB/OL].(2014-10-01)[2017-12-22].http://www.doc88.com/p-9085745880233.html.

[2] 刘雷波,夏宇闻.低功耗验证方法学[M].北京:北京航空航天出版社,2012:50.LIU Lei-bo,XIA Yu-wen.Low Power Verification Methodology[M].Beijing:Beijing Aerospace Press,2012:50.

[3] 蒋文栋,路勇.数字集成电路低功耗优化设计研究[C].北京:北京交通大学,2008:17.JIANG Wen-dong,LU Yong.Research on Low Power Optimization Design of Digital Integrated Circuits[C].Beijing:Master's Degree Thesis of Beijing Jiaotong University,2008:17.

[4] Innopower Technology Corporation.SMIC 55nm Logic LL & eFlash SVT Process 7-Tracks Generic Core Cell Library[DB/OL].(2014-06-01)[2017-12-12].http://www.innopower-tech.com/eserviceii/web/aipDownload.do.