ATCA平台中FPGA组件化开发环境研究

董胜 岳春生 刘拥军

摘 要: 基于软件通信体系架构无法实现对FPGA等专用处理器的兼容,依据CP289协议的容器和组件模型思想以及MHAL接口规范,针对高速率、多接口、较大规模的ATCA硬件平台和高速、实时信号处理的需求,通过分层抽象的方法,设计一个标准化的FPGA组件开发环境。并设计FFT组件验证该开发环境的可行性和合理性,实现了在ATCA平台上FPGA专用处理器与SCA体系架构的融合以及波形组件的可移植。

关键词: 软件通信体系架构; 软件无线电; FPGA组件; CP289协议; MHAL接口规范; ATCA平台

中图分类号: TN911.2?34; TN014 文献标识码: A 文章编号: 1004?373X(2018)08?0030?04

Abstract: Software communication architecture (SCA) cannot realize compatibility with special processors like FPGA. According to the container and component model of CP289 protocol and MHAL interface specification, and in allusion to the high speed, multi?interface and relatively large scale ATCA hardware platform and the requirement of real?time signal processing, a standard FPGA component development environment is designed by using the hierarchical abstraction method. The FFT component is designed to verify the feasibility and rationality of the development environment. The integration of special FPGA processor with SCA and portability of waveform component are realized on the ATCA platform.

Keywords: SCA; SDR; FPGA component; CP289 protocol; MHAL interface specification; ATCA platform

0 引 言

軟件通信体系架构(Software Communication Architecture,SCA)为软件无线电(Software Defined Radio,SDR)定义了最基本要求的实现框架,构建了一个开放式、标准化和通用性强的软件体系架构[1]。目前基于SCA的SDR系统获得通用处理器(General Purpose Processor,GPP)的良好支持。针对在FPGA处理器上难以集成SCA架构的问题,2004年SCA3.0提出硬件抽象层互联(HAL?C)的概念[2]。硬件抽象层通过对具体硬件的抽象,实现了在软件无线电设备开发过程中软件的设计和通用硬件平台相分离。为了更好地实现专用硬件组件的复用和移植,在随后的SCA3.1中提出了组件可移植规范(CPS),并在此基础上经过广泛的讨论和征求意见,形成了专用处理器组件可移植补充建议(SHP),即CP289[3]。文献[4]提出MHAL接口标准,通过在核心框架与FPGA之间加入代理,明确规范了代理与FPGA之间的数据格式来实现FPGA在SCA中的应用。与此同时,国内外的一些研究团队提出基于FPGA设计ORB引擎的方法,通过实现CORBA报文的解析和封装,使FPGA直接支持CORBA通信从而实现与SCA架构的融合[5?8]。

基于HAL?C和MHAL接口标准,实现了波形外部接口的抽象,减小了硬件平台结构对软件设计的影响,但所提供的接口较少、功能有限,且很多技术细节不对外开放。CP289中提出标准化波形组件的运行环境,保证了波形的可移植,然而怎样设计容器架构并提供一个标准的实时的运行环境仍然是一个问题,CP289中也未做出解答。基于FPGA设计ORB引擎能够实现FPGA无缝地融入到SCA系统中,但ORB引擎设计比较复杂,在运行过程中会有大量的计算资源和存储资源被占用,造成资源的浪费。本文针对ATCA平台板卡多处理器及高速背板交换技术的特点,采用基于CP289协议的容器和组件模型思想以及MHAL接口规范,利用分层抽象的方法构建一个标准化的FPGA组件运行环境,实现FPGA专用处理器与SCA体系架构的融合以及波形组件的可移植。

1 容 器

在CP289协议中,容器为FPGA波形组件提供了标准化的运行环境,使得波形组件与运行的环境相分离,并为SCA核心框架提供对组件的管理、控制和配置等操作。本设计中的容器主要结构如图1所示。针对ATCA平台高速背板传输接口(如Rapid I/O,XAUI,PCIE等)和ATCA平台多层管理的特点,设计了可移植、可裁剪的基于FIFO的数据传输层,而板卡上多处理器间的传输通过透传模块实现。

1.1 复位管理器和时钟管理器

复位管理器主要是对整个计算单元和各个组件的复位进行控制。每个组件都有一个复位信号,都连接于容器。容器给出的复位信号主要是全局复位信号,主要受控于外部硬件复位信号和控制命令发出的全局复位命令。时钟管理器主要是根据外部时钟源和内部组件的需要产生多个时钟信号,容器一般只使用一个锁相环产生一组时钟,组件开发者可以根据需要使用FPGA的其他锁相环。

1.2 数据传输层

数据传输层以数据包为基本数据单元进行传输和路由分发,对板卡进行加载、配置、控制、状态获取等操作,如图2所示。数据传输层是为具体板卡所定制的,与板卡的结构和技术特点紧密相关。传输层提供通信接口的驱动支持,根据平台的类型,主要包括通信接口、PCI接口、PCIE接口、10/100/1 000M网口、万兆网接口等,和外围存储接口,如DDR?RAM接口、SRAM接口、FLASH接口等。为了将这些接口的驱动本地化,在接收端和发送端分别设计了一个基于FIFO的缓冲池,并对FIFO的状态进行检测,以保证传输的可靠性。

对于数据传输层而言最大的任务是在下行数据输入时按照数据传输协议进行解析和判断,判断是否是本板卡的数据包,如果不是本板卡的数据包,則丢弃;如果是本板卡的数据包,则进一步解析后发送到硬件抽象层。而上行数据在经过传输层输出时同样需按照数据传输协议进行封装打包,若在输出过程中存在多个通道同时传输,则需要依据各通道的优先级进行传输申请,实现数据的有序传输。

1.3 硬件抽象层MHAL

MHAL是一个底层的通信模型,它为SCA系统中不同处理单元(CE)上的波形组件和硬件之间的通信提供标准的协议和接口,从而显著提高波形应用的可移植性。由于MHAL建立了DSP,FPGA与GPP之间的标准通信方式,因此它实现了SCA各处理平台之间的互联互通,使得DSP,FPGA波形可以很好地集成到SCA系统中。

下行数据经过“MHAL帧解析”后分为控制接口数据和通信接口数据,控制接口数据能够实现对应用组件的控制和组件参数配置,通信接口数据为应用组件传输待处理的数据。

组件处理完数据后经过互联层向传输层进行传输申请,若申请反馈同意传输,则需要将OCP接口转换为MHAL帧格式从而实现上层数据在传输层的传输,若申请反馈不同意传输,则继续向传输层申请传输,如图3所示。

1.4 互联层

互联层负责本处理器内部组件间的通信互联,因为组件都采用的是标准OCP接口,故对于FPGA内的组件互联不需要进行数据格式的转换,直接进行管脚映射的方式就能实现。

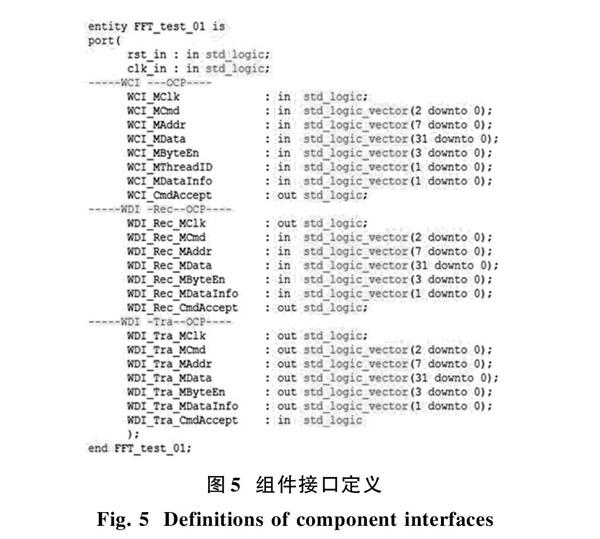

2 组件接口

CP289协议中提出了使用开放核协议(OCP)来设计和实现FPGA上的组件接口。OCP协议[9]全面考虑了各种组件应用,提供了丰富的组件接口信号,可以实现基本传输、突发传输、乱序传输等多种传输方式。但提供的接口过于繁杂,难以直接使用。CP289根据组件的功能需要,综合考虑性能以及可重用性等方面的因素,规定了组件的三种接口[10],如图4所示。

1) 控制接口 (WCI)。控制接口为容器提供了控制和管理组件的通道和方法,实现对组件的初始化、运行、停止、释放、测试、配置参数寄存器等功能。该接口的定义和实现对于任何组件来说都是一样的,波形组件开发者只需要实现该接口,而不必考虑与SCA核心框架之间的交互,这方面的工作都由容器负责完成。

2) 通信接口 (WDI)。通信接口可分为“发送端”和“接收端”,分别用于数据的发送和接收,通信接口负责与容器以及容器之中其他组件之间的数据通信。

3) 本地服务接口。本地服务接口为组件功能实现提供资源服务的接口,主要包括时钟、复位以及存储器访问等标准的本地服务,以及实现波形组件的各种功能。

此外,CP289还对各种组件接口的实现细节以及时钟提供方式、存储器访问方式等做了进一步的约束,图5所示为组件在程序中的接口定义。

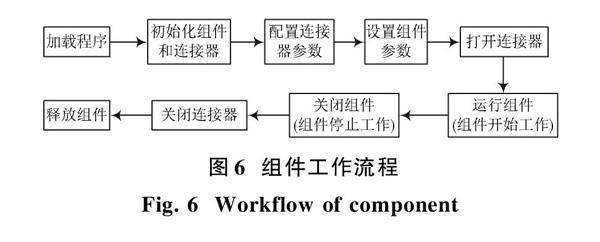

3 工作流程及实例

图6所示为组件在容器环境中的工作流程,用户通过平台控制软件的核心框架将程序下载到FPGA芯片中,加载完毕后首先初始化应用组件,通过控制端口给组件发送初始化命令,接着发送连接器初始化命令,初始化阶段组件和连接器默认为接收状态。配置连接器参数可以明确组件的端口发送的源地址、目的地址、数据位宽等关键参数。组件参数根据用户应用需求也是通过控制端口进行配置,例如A/D组件的采样频率。打开连接器后,组件就可以进行数据的接收和发送,保证了整个数据通道的畅通。组件开始工作后,就会根据应用需求进行相应的数据处理。数据处理结束后关闭组件,待数据通过连接器发送完毕后关闭连接器,然后释放组件,使组件处于脱离状态,以减小运行功耗。

为了测试组件化开发环境的可行性和合理性,设计了FFT组件。FFT组件同样需要采用标准的OCP接口,控制接口是组件作为Slave端的OCP接口,为实时操作,不支持回读,不支持接收响应,每个组件只有一个控制接口。通信端口组件既可以作为Slave端又可以作为Master端,当组件接收容器传来的数据时,组件作为接收方,容器作为发送方,当组件处理完数据后,则容器作为接收方,组件作为发送方。由图7可观察到,FFT组件OCP端口各信号输出正常,说明容器结构设计的可行性和合理性。

4 结 论

本文基于FPGA等专用处理器难以与SCA系统融合的现状,针对硬件结构较为复杂的ATCA平台,设计了一个标准化的FPGA组件开发环境,同时设计了FFT组件验证该开发环境的可行性和合理性,实现了在ATCA平台上FPGA专用处理器与SCA体系架构的融合以及波形组件的可移植。

参考文献

[1] GONZALEZ C R A, DIETRICH C B, REED J H. Understanding the software communications architecture [J]. IEEE communications magazine, 2009, 47(9): 50?57.

[2] 张晓波,窦衡.SCA规范下FPGA的硬件抽象层设计[J].电子元器件应用,2010,12(2):73?76.

ZHANG Xiaobo, DOU Heng. The design of the hardware abstraction layer of FPGA in the SCA specification [J]. Electronic component &; device applications, 2010, 12(2): 73?76.

[3] Joint Program Executive Office. Extension for component portability for specialized hardware processors (SHP) change proposal 289 (CP289): JTRS V3.1x [S]. [S.l.]: Joint Program Executive Office, 2005.

[4] JPO J. Modem hardware abstraction layer API 2.13 [M]. San Diego: JTRS Standard, 2010.

[5] 高宏伟,吴宇,施峻武,等.基于SCA的软件无线电在FPGA上设计与实现[J].现代电子技术,2011,34(19):103?107.

GAO Hongwei, WU Yu, SHI Junwu, et al. Design and implementation of SCA?based SDR on FPGA [J]. Modern electronics technique, 2011, 34(19): 103?107.

[6] 谭翔.基于SCA架构的SoPC设计与实现[D].长沙:国防科技大学,2011.

TAN Xiang. Design and implementation of SoPC based on SCA [D]. Changsha: National University of Defense Technology, 2011.

[7] PrismTech. OpenFusion CORBA Products [EB/OL].[2011?04?12].http://www.prismtech.com/sectionitem.asp?id=570&;sid=18&;

sid2=10&;sid3=251.

[8] BECKWITH W, DELLER S, G. THOMPSON J. Hardware communications infrastructure supporting location transparency and dynamic partial recon?figuration: US2008/0229326A1 [P/OL]. [2008?09?18].

[9] OCP?IP. OCP Specification Release 2.2 [EB/OL]. [2006?03?01]. http://www.ocpip.org.

[10] 鄧刚,高宏伟,周军辉,等.FPGA上SCA波形组件接口的设计与实现[J].信息通信,2012(4):16?18.

DENG Gang, GAO Hongwei, ZHOU Junhui, et al. Design and implementation of SCA waveform component interface on FPGA [J]. Information &; communications, 2012(4): 16?18.