片上网络跨时钟域的高速数据通信接口设计*

,,,

(东北大学 信息科学与工程学院,沈阳 110819)

引 言

随着国内微电子技术的快速发展以及FPGA系统设计的复杂化,在单一芯片上集成数百个IP核已成为可能。片上网络(Network on Chip, NoC)的出现满足了众多IP核通信的需求,已逐渐成为片上多核的标准通信架构。然而,传统的同步设计技术采用单一的电压时钟域,限制了NoC性能的提高和功耗的降低,已逐渐成为片上网络的设计瓶颈[1]。全局异步局部同步(Globally Asynchronous and Locally Synchronous,GALS)设计思想[2]作为一种新的设计方法近年来成为了片上网络的研究热点。它在保持原有IP核同步工作方式的基础上,采用异步握手协议完成IP核之间的通信,一方面增加了片上网络的可扩展性,另一方面进一步降低了系统的能耗。以GALS设计思想为基础的多电压频率岛(Voltage Frequency Island,VFI)片上网络也逐渐替代了传统的同步片上网络。多电压频率岛片上网络中,电压和频率的划分可以采用多种运算模型,例如采用具有可靠性的电压频率岛感知异步片上网络能耗优化算法[3]等。

在实际的工程中,尤其是高速视频采集和处理系统中,系统内部的各个功能模块往往需要工作在不同频率的时钟域中。因此,不同时钟频率的IP核之间如何通信(即跨时钟域同步电路通信机制及其设计方法)近年来成为了多电压频率岛片上网络的研究热点。参考文献[4]提出了多时钟的混合同步/异步系统设计方法,利用GalsBlock运算模型自动生成混合同步异步系统,完成不同时钟域模块之间的混合通信。参考文献[5]提出了高速数据的跨时钟域处理及验证方法,利用Verilog HDL设计了具有空满标志的异步FIFO并进行了测试及验证。参考文献[6]提出了用于多电压频率岛片上网络的可配置FIFO设计,以双端口SRAM为基础,通过读写指针及可配置设计,使其既可以用于同步电路,也可以用于异步电路。参考文献[7]提出了可用于跨时钟域处理的自适应多级FIFO结构,采用虚拟通道机制。参考文献[8]提出了新的异步FIFO结构,采用异步插入同步取出的设计方法,实现跨时钟域的通信。这些设计方法均在一定程度上很好地减小了跨时钟域传输所带来的亚稳态的影响,部分方法通过采用电压频率岛分配机制,能够有效减小NoC的能耗。但是,对于基于片上网络的高速视频采集和处理系统,上述方法仍有一定的局限性,无法在降低功耗的同时满足片上网络对大容量、多比特和高速度视频数据码流进行实时传输的需求。其中,参考文献[4]、[6]、[7]、[8]没有考虑高速数据处理问题。参考文献[5]的设计方法采用基于双端口SRAM的异步FIFO,通过空满标志位的设计完成跨时钟域的通信,并针对60 Hz的图片数据进行了测试,但并未考虑该结构应用于片上网络时需要作出的处理。

针对以上参考文献在基于片上网络的跨时钟域高速数据处理方面遇到的问题,本文提出了一种新的片上网络跨时钟域高速数据接口电路。针对采用多电压频率岛分配方案的异步片上网络,将多路选择器模块和基于令牌环的环形异步FIFO相结合,能够有效减小亚稳态的影响,并增加片上网络系统数据传输的吞吐率,满足用于视频采集和处理系统的片上网络对大数据量和高速度数据码流进行实时传输的需求。

1 片上网络跨时钟域高速数据通信接口电路结构及协议

1.1 跨时钟域高速数据通信接口电路结构

图2 片上网络跨时钟域高速数据通信接口电路设计

为了满足片上网络跨时钟域通信接口电路对大数据量和高速数据处理的需求,本文提出的通信接口电路是由输入多路选择器模块、数据缓冲存储模块和输出多路选择器模块三大部分组成。输入多路选择器模块的输出端连接到数据缓冲存储模块的输入端,数据缓冲存储模块的输出端连接到输出多路选择器模块的输入端。具体电路结构如图1所示。

图1 片上网络跨时钟域高速数据通信接口电路设计

其中,数据缓冲存储模块包括4个基于令牌环的环形异步FIFO。每个环形异步FIFO包括令牌环结构,每个令牌环结构包括8个锁存器,8个锁存器的连接方式为上一级锁存器的输出端连接到下一级锁存器的输入端,最后一级锁存器的输出端连接到第一级锁存器的输入端。

1.2 环形异步FIFO设计及协议

为了在片上网络上实现不同时钟域之间的数据通信,通常采用FIFO作为数据通信的主要方式[9]。常用的设计方法有采用仲裁机制、可停时钟、双端口SRAM等。本文提出一种可采用标准单元设计的基于令牌环的环形异步FIFO,其数据传输通道与读写指针控制逻辑互相独立,数据同步逻辑与读写指针分离。

图2为基于令牌环的环形异步FIFO体系结构图。在该结构中,读/写指针令牌将最后一级的输出与第一级的输入相连构成一个环形,最后一个锁存器中的数值将被转移到第一个锁存器中,即通过“令牌”的移动和调整来产生读/写指针,从而控制基于令牌环的环形异步FIFO的读/写操作。

基于令牌环的环形异步FIFO中有且只有一个读指针和一个写指针,它们均以“令牌”的形式在令牌环中由左向右传递,当基于令牌环的环形异步FIFO进行写操作时,写指针指向数据存储单元进行数据存储,存储完数据后,写指针指向下一级数据存储单元。同理,当基于令牌环的环形异步FIFO进行读操作时,读指针指向基于令牌环的环形异步FIFO数据存储单元进行数据读出,完成读数据后,读指针指向下一级的数据存储单元。读、写操作根据以上协议循环进行。

与传统的异步FIFO相比,基于令牌的异步环形FIFO采用“令牌” 轮询机制来产生读/写指针,简化了常规的异步FIFO单元,避免了使用大量的同步器,从而减少了其占用的逻辑资源数目和面积空间,适于在基于片上网络的系统上使用。另外,通过设计基于令牌的异步环形FIFO的工作协议,实现了数据在跨时钟域传输时的高速延时无关,避免了在跨时钟域传输时可能导致的亚稳态问题。且由于其数据传输通道与读写指针控制逻辑互相独立,数据同步逻辑与读写指针分离,因此该FIFO结构可以支持多种格式及传输协议的数据,提高了接口电路的可重用性,也使其性能有了显著地提高,从而可以满足大数据量视频数据实时传输的要求。

1.3 亚稳态的处理

亚稳态是指触发器无法在规定时间内达到确定状态。当触发器进入亚稳态时,无法预测输出电平,也无法预测输出何时稳定在正确的电平上。在亚稳态期间,触发器输出中间电平或者振荡状态,输出电平沿信号通道上的各个触发器级联式传播下去[10-12]。在片上网络相邻节点之间进行跨时钟域数据传输容易引起亚稳态,导致数据丢失,影响片上网络高速视频数据处理系统的性能。在跨时钟域高速数据通信接口电路中,利用所设计的电路结构和环形异步FIFO,通过对令牌轮询电路的设计将令牌作为FIFO的读/写指针,通过令牌的移动变换来控制读/写过程,使数据传输通道与读写指针控制逻辑互相独立,通过对数据的缓存来满足同步信号传输的“建立”和“保持”时间,减小亚稳态的影响。

2 片上网络跨时钟域高速数据通信接口电路设计和分析

将本文提出的跨时钟域高速数据通信接口电路应用于片上网络,构建能用于高速数据处理的片上网络系统。

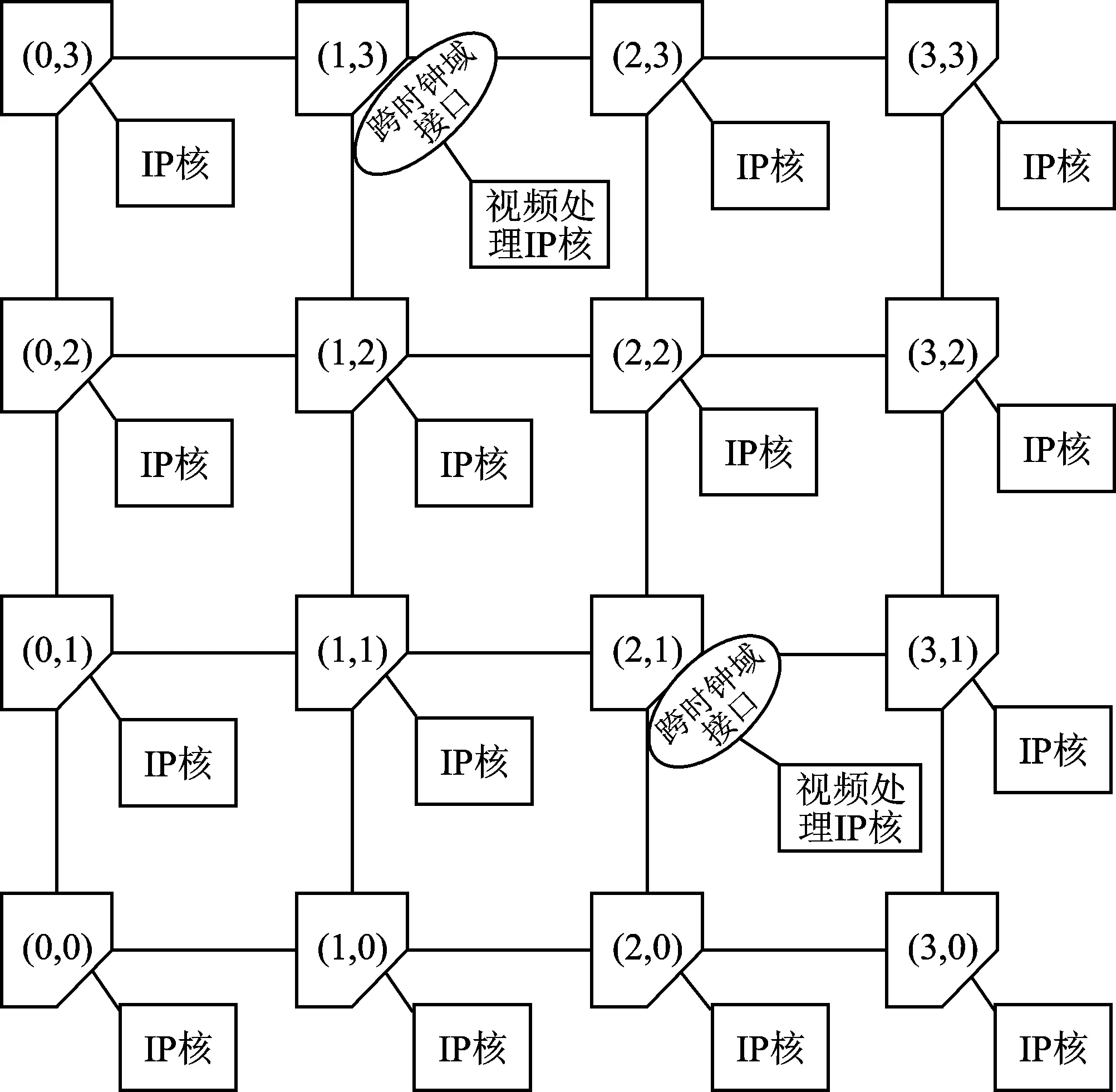

2.1 跨时钟域高速数据通信接口电路实现

采用跨时钟域高速数据通信接口电路的片上网络系统结构图如图3所示。片上网络采用4×4的2D-Mesh拓扑结构,其中(0,0)路由节点在整个片上网络的左下角,(3,3)路由节点在整个片上网络的右上角,X坐标自左向右依次增大,Y坐标自下而上依次增大。片上网络的路由节点可以挂载相应的视频采集IP核和视频处理IP核。将视频采集IP核挂载到(2,1)路由节点,将视频处理IP核挂载到(1,3)路由节点。视频采集IP核的工作时钟为CLK1,视频处理IP核的工作时钟为CLK2,片上网络的工作时钟为CLK3。片上网络的视频采集IP核所产生的输入数据输入到输入多路选择器模块,输入多路选择器模块在使能信号有效的情况下把输入数据依次输出到数据缓冲存储模块,输出多路选择器模块在使能信号有效的情况下将数据缓冲存储模块中的数据依次读出,并将输出数据送入片上网络进行传输。

图3 片上网络跨时钟域高速数据处理系统

2.2 数据缓冲存储模块的电路实现

数据缓冲存储模块包括4个基于令牌环的环形异步FIFO。采用多个基于令牌环的环形异步FIFO结构,可以有效地减小系统存储空间不足的问题,并通过输入数据选择器和输出数据选择器模块的设计保证数据的有序传输,并能有效地避免亚稳态问题。数据缓冲存储模块的结构可以扩展到由N个令牌环的环形异步FIFO组成,具体结构设计要根据片上网络规模及硬件资源情况分析确定。

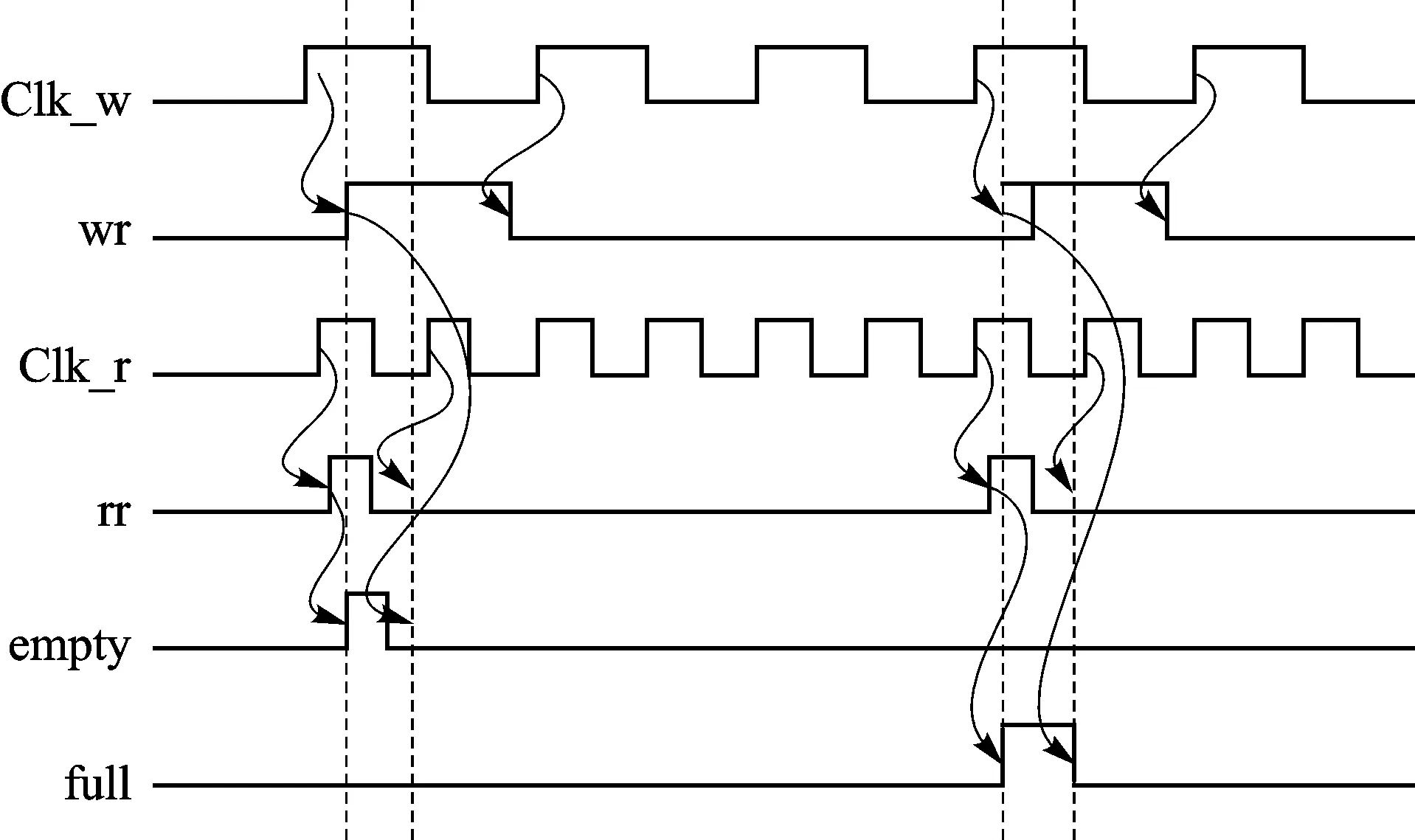

2.2.1 异步环形FIFO空/满判断逻辑时序

为了避免亚稳态问题,采用令牌环结构,当读指针和写指针相等也就是指向同一个内存位置时,异步FIFO可能处于满或空状态。通过判断写指针从后赶上了读指针,还是读指针从后赶上了写指针来确定异步FIFO是处于空状态还是满状态。以从慢时钟域到快时钟域的数据传输为例,分析环形异步FIFO的空/满判断逻辑时序,具体如图4所示。wr为写指针,rr为读指针,高电平有效。电路中有且只有一个读指针和一个写指针,读/写指针的高电平状态称为“令牌”。通过令牌的移动和调整来控制产生基于令牌环的环形异步FIFO的空/满状态,从而控制基于令牌环的环形异步FIFO的读/写操作。

图4 异步环形FIFO空/满判断逻辑时序图

2.2.2 数据缓冲存储模块发送端逻辑时序

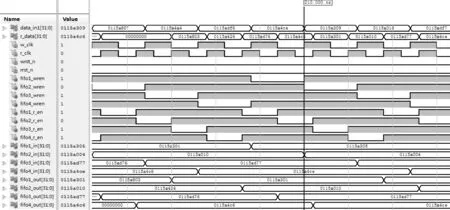

数据缓冲存储模块包含4个异步环形FIFO,以发送端模块为例,分析其发送端逻辑时序,具体如图5所示。Fifo_ren为每个FIFO的读使能信号,Fifo_rdata为数据信号。在使能信号有效时,将输入数据送到相应异步环形FIFO输出端口。

图5 数据缓冲存储模块发送端逻辑时序图

3 实验结果及分析

片上网络跨时钟域高速数据通信接口电路用System Verilog语言,在Altera Quartus II 14.0上实现并仿真测试,片上网络采用4×4的2D-Mesh拓扑结构。系统性能测试使用的硬件平台为Altera DE2-115系列的FPGA。

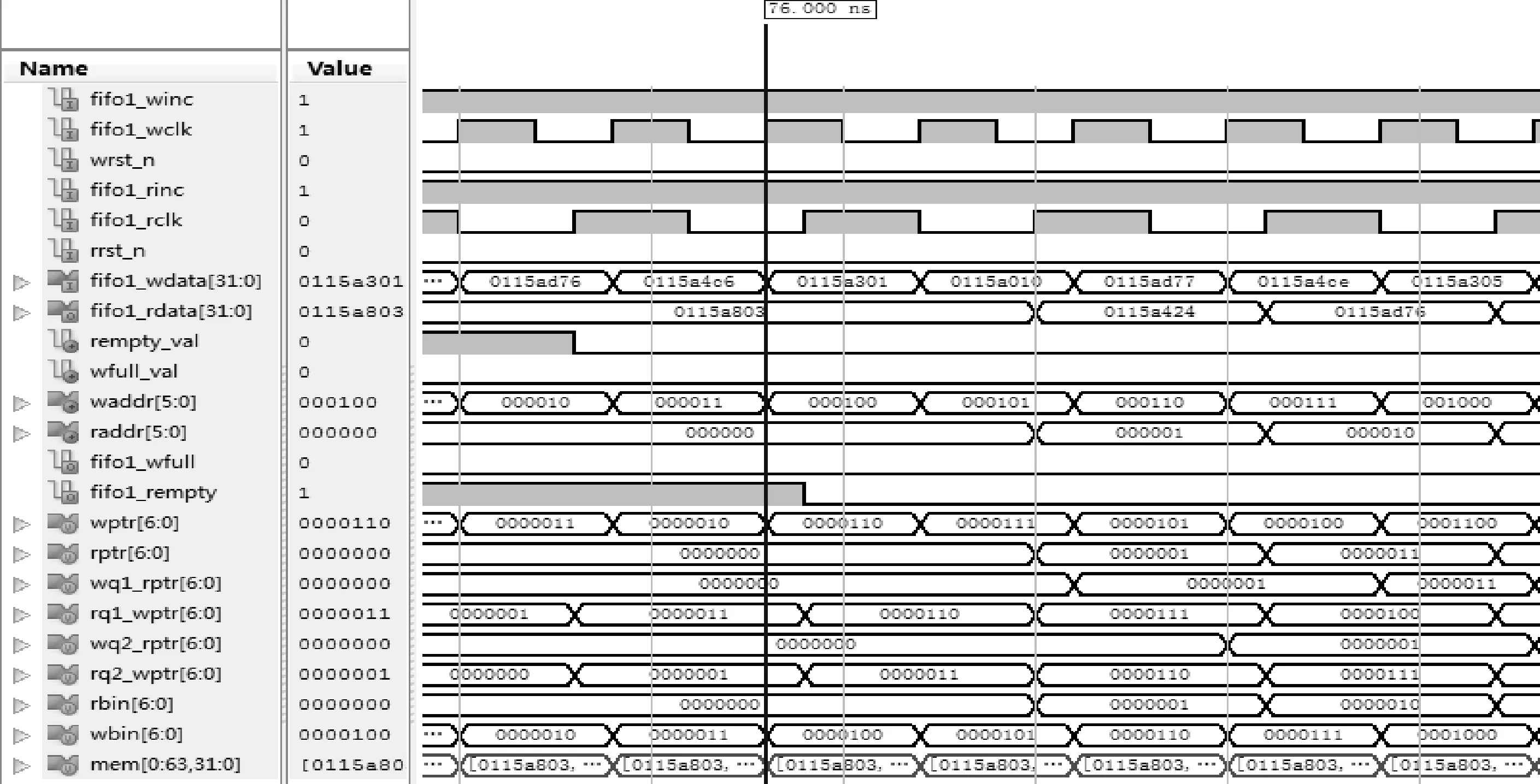

3.1 异步环形FIFO传输性能分析

以数据从快时钟域到慢时钟域传输分析为例,在测试文件中依次写入100个数,如0115 a803、0115 a424、0115 ad76等。数据传输仿真图如图6所示。

当写时钟wclk上升沿到来时,且写使能信号winc有效,输入端口wdata将数据缓存到寄存器my_memory中,当读时钟rclk上升沿到来时,且读使能信号rinc有效,环形异步FIFO将缓存器my_memory中的数据读出到输出端口rdata。从FIFO的输入端口写入一个数据到读出该数据总共需要50 ns。显然,仿真测试结果表明了快时钟域到慢时钟域数据传输的正确性。

3.2 跨时钟域高速数据通信性能测试

在测试文件中定义写时钟周期为4 ns,读时钟周期为6 ns,连续写入50个数据,仿真结果如图7所示。

仿真结果表明,数据从快时钟域到慢时钟域,能够按照4个环形FIFO的顺序写入读出,从FIFO的输入端口写入一个数据到读出该数据需要消耗6个读时钟周期,即会带来36 ns的延时,但是数据是连续传输的,所以对于图像或视频数据来说,采用该文设计的跨时钟域高速数据通信接口,可以保证图像或视频数据的连续传输。

图6 异步环形FIFO仿真测试图

图7 跨时钟域高速数据通信性能测试图

3.3 片上网络调用视频处理单元测试

在Altera DE2-115 FPGA上实现了本文提出的规模为4×4的片上网络,并将视频采集IP核挂载到(2,1)路由节点,将能实现运动目标跟踪检测的视频处理IP核挂载到(1,3)路由节点。视频采集IP核的工作频率为25 MHz,视频处理IP核的工作频率为50 MHz。采集的视频长度为1 min 46 s,帧率为25 fps。跨时钟域数据传输采用本文提出的跨时钟域高速数据通信接口电路。视频处理结果如图8所示。测试中,视频跟踪准确率可达94.76%。实验结果表明,本文提出的跨时钟域高速数据通信接口电路增加了片上网络系统数据传输的吞吐率,满足用于视频采集和处理系统的异步片上网络对大数据量和高速度数据码流进行实时传输的需求。

图8 运动目标跟踪检测结果

3.4 与其它设计的比较

本文设计的通信接口电路与采用相同参数的其它同异步转换接口电路的性能比较如表1所列。参考文献[9]仅采用环形FIFO作为通信接口电路,在传输大数据量的视频数据时,容易造成阻塞现象,导致视频数据的不连续。参考文献[13]采用可停时钟设计,数据传输时暂停时钟可能会导致接收端的视频数据丢失。本文的设计通过采用具有令牌环结构的异步环形FIFO和多路数据选择器构成通信接口电路,增加了吞吐量并能够有效避免因为FIFO阻塞而造成的数据不连续的现象。

表1 不同跨时钟域接口电路性能比较

结 语

本文提出了一种片上网络跨时钟域高速数据处理结构及其电路设计。该结构针对采用多电压频率岛分配方案的异步片上网络,为了满足片上网络对于大数据量和高速数据进行处理的需求,提出利用多路选择器模块和基于令牌环的环形异步FIFO构成跨时钟域高速数据通信接口电路。通过在异步片上网络的路由节点挂载视频采集IP核和视频处理IP核,对片上网络跨时钟域高速数据通信接口电路设计进行验证。

[1] 张剑贤,周端,杨银堂,等.处理器可靠性约束的电压频率岛NOC能耗优化[J].电子与信息学报,2011,33(9):2205-2211.

[2] D M Chapiro.Globally asynchronous locally synchronous systems[D].PhD thesis:Stanford University,1984.

[3] 李贞妮,李晶皎,金硕巍,等.可靠电压频率岛感知的异步片上网络能耗优化[J].信息与控制,2016,45(6):671-676.

[4] Yu Jiang,Hehua Zhang,Huafeng Zhang,et al.Design of Mixed Synchronous/Asynchronous Systems with Multiple Clocks[J].IEEE Transactions on Parallel and Distributed Systems,2015,26(8):2220-2232.

[5] 侯宏录,齐晶晶.高速数据的跨时钟域处理方法及验证[J].西安工业大学学报,2015,35(6):434-440.

[6] Amir-Mohammad Rahmani,Pasi Liljeberg,Juha Plosila,et al.Design and implementation of reconfigurable FIFOs for Voltage/Frequency Island-based Networks-on-Chip[J].Microprocessors and Microsystems,2013(37):432-445.

[7] Masoud Oveis-Gharan,Gul N Khan.Statically adaptive multi FIFO buffer architecture for network on chip[J].Microprocessors and Microsystems,2015(39):11-26.

[8] Thi-Thuy Nguyen,Xuan-Tu Tran.A Novel Asynchronous First-In-First-Out Adapting to Multi-synchronous Network-on-Chips [C]//The 2014 International Conference on Advanced Technologies for Communications,Vietnam,2014:365-370.

[9] 彭瑶,朱端,杨银堂,等.高速环形FIFO的设计[J].计算机辅助设计与图形学学报,2011,23(3):488-495.

[10] Liang Jun,Tang Lu,Zhang Ming.A Random Delay Injection Based Clock Domain Crossing Verification Method[J].Microelectronics&Computer,2014,31(2):1-4.

[11] Amir-Mohammad Rahmani,Pasi Liljeberg,Juha Plosila,et al.Developing a power-efficient and low cost 3D-NoC using smart GALS-based vertical channels[J].Journal of Computer and System Sciences,2013,79(4):440-456.

[12] S Casale Brunet,E Bezati,C Alberti,et al.Partitioning and Optimization of high level stream applications for multi clock domain architectures[C]//2013 IEEE Workshop on signal processing systems,2013:177-182.

[13] De Clercq,Negulescu R.1.1-GD1/s transmissions between pausible clock domains[C]//IEEE International Symposium on Circuits and Systems, Scottsdale,2002:768-771.

李贞妮 (讲师),主要研究方向为嵌入式系统、图像处理、片上网络;李晶皎(教授),主要研究方向为嵌入式系统、模式识别、图像处理等。