TTL电平反推排错法在数电实验教学中的应用

夏斯权 周亦敏 杨一波 谭爱国

摘要:针对传统数字电子技术实验项目在学生设计与实现过程中容易出现故障,对经常出现的问题进行提炼总结,提出TTL电平反推法,根据输出的实验现象一步一步向前反推,找出对应的原状态的致使条件,对的保留,不对的继续反推前一级,找出错误的根源。通过教学实践,学生可以具备自行解决数电实验项目中常出现问题的能力,证明TTL电平反推排错法在数电实验教学应用中具有可实施性。

关键词:数字电子技术;实验;TTL电平

中图分类号:G642.0 文献标识码:A DOI:10.3969/j.issn.1003-6970.2017.08.035

引言

数字电子技术是高等院校电类专业本科教学中一门重要的、实践性强的专业基础课。所有的理论体系都有对应的实践内容,供教学使用。通过实践环节的锻炼,巩固、加深学生们对所学理论知识的理解。通过走访不同高校的电工电子实验室,对比实验教学内容,许多高校开设的数电实验课现施行比较多的还是基于传统的数模电路实验箱,数电实验箱上面有许多IC芯片插座,对应的74系列芯片基本上都是双列直插式的,选取不同引脚数,直接插接在引脚数量相对应的芯片插座上,根据实验设计内容,通过软导线手工搭建对应的实验项目。学生在数电实验课堂上,可以比较直观的理解某个具体功能的实验,其外围线路的连接,电源选取,对于每个芯片的外部结构都会有一个清晰的认识,

操作硬件的思维能力也会有明显的锻炼和提升。但是这样传统的搭建硬件电路实验,复杂的实验项目外接的导线多达上百条数,导线连接容易出错,实验现象不正确,而且学生在短时间内很难找出错误点的位置。笔者在实验教学过程中,总有学生在问这个怎么解决,或者有的学生就把接线全部拆除重接。遇到此类问题,许多教学研究者提出了新的思路,文献对于数字电路实验采用现代Quartus II仿真工具进行了实际研究,并与传统实验方法进行系统对比研究,基础部分实验仍以数字电路实验箱为主要工具完成,对于复杂的数字电路设计实验使用Quartus II电路原理图设计输入及其仿真功能完成数字逻辑。文献采用EDA技术自制了74系列芯片模拟器,通过让学生使用芯片模拟器,使得学生理解数字电子技术和EDA之间的关系,培养了学

生理解数电原理的能力。文献将FPGA技术引入数字电子技术实验教学中,开发了基础实验还有课程设计实验,改善了传统实验教学模式,增强了实验的创新性。综上所述,无论以传统的数电教学模式,还是引入仿真或者高级的教学工具,我们还是缺少对数字电路连接排错的讲解与总结,由于大多数高校还是以实验箱上连接芯片实现相关逻辑功能的基本操作,为此本文提出一种基于TTL电平反推排错法应用到数电实验教学中去,通过输出的实验现象一步一步向前反推找出错误的位置,然后予以快速纠正,让学生在极短的时间内找出错误之处,进一步加强对电路和芯片结构的理解。

1 常见错误提炼

传统的数电实验教学都是基于数电实验箱上的芯片来完成,图1为上海理工大学电工电子实验中心数电教学实验箱,对应芯片选型区域中摆放了多个14引脚74系列的芯片,在使用芯片完成实验内容的时候注意避免基本错误发生,下面提炼3个常见错误。

(1)芯片工作电压极性接反。

(2)多个芯片时,有遗漏芯片没有外加工作电压。

(3)芯片逻辑功能使用前没有测试好坏。

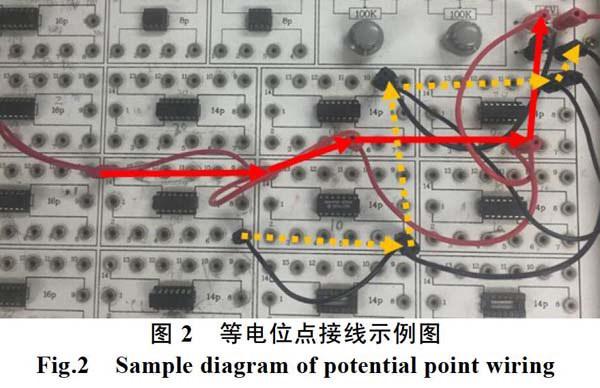

学生使用芯片要对准其管脚图,找到对应的电源管脚VCC和接地管脚GND,外加工作电压——对应连接,使用多个芯片时,确保使用的每一个芯片都要外加工作电压,这里可以运用电路等电位点原理把对应芯片的电源管脚VCC串连在一^起引出一根导线到电源正极,接地管脚GND亦是如此引出一根线到电源负极。具体见图2所示,这样可以有效避免漏接现象。此外芯片逻辑功能测试主要按照对应的门电路真值表进行测试。每一块芯片上实现同一个逻辑功能的门电路至少集成2个以上,每次实验时根据需求,用到就对其进行测试。

2 TTL电平反推排错法原理

TTL电平反推排错法主要根据实践电路的最终输出现象对与否进行应用,电路输出现象观察主要是依据LED灯显示或者数码管显示。因为数电实验内容的输出现象有多个状态,只要有一种状态不对,整个搭建的电路设计就存在某些问题。TTL电平反推排除法以当前错误的输出状态为切人点,找出对应门电路的输出端口,如果要求的输出为高电平,LED灯要点亮,这里使用万用表20V直流档位检测该门电路的输出对应的输入端口的电平高低,利用反推思路测试当前门电路的逻辑功能,首先验证在当前输入电平的状态下,输出状态对与否,对表明此部分芯片的门电路没有问题,不对表明该门电路需要更换,在门电路没有问题的情况下,需要找出该门电路输出端对应的输入致使其输出为低电平的端口,这些输入端口有的是前级门电路的输出,有的是逻辑电平开关输入,需要注意一一区分,如果是前级门电路依据先前分析步骤重复反推测试即可,如果是逻辑电平开关,需要对准原先设计的逻辑电路图认清输入的高与低即可。排除的宗旨就是要抓住“反推”的核心思想,找出对应的原状态的致使条件,对的保留,不对的继续反推前一级,找出错误的根源。

3 TTL电平反推排除法应用

为了更好的推广这一^段,ib学生能够自行掌握,下面分别在常用的实验项里选择组合逻辑电路和时序逻辑电路两个项目进行反推排错说明,本文涉及的实例都是以上海理工大学电工电子实验中心的教学大纲为参考:

3.1 组合逻辑电路测试应用

利用74系列138芯片与相关与非门实现奇偶校验器功能,实现输入变量中有奇数个1输出为1,偶数个1输出为0。结合74LS138芯片的基本结构分析真值表如表1所示,逻辑电路图如图3所示,芯片选用了三输入的与非门芯片74LS10和四輸入的与非门芯片74LS20,还有一个主控芯片74LS138。

表1输出数据是检测奇偶校验器逻辑电路图的依据,下面列举表1両框数据作为反推实例,如Fl,F2输出分别连接到两个LED灯显示,发现灯同时被点亮,对照电路实际的逻辑功能,可以清楚发现ABC的电平状态为101,输入有偶数个1,F1为高电平错误,F2输出正确,使用万用表拨到20V直流档位直接检测F1所在的四输入与非门,先检测当前输入与输出的逻辑状态是否对应,只要当前的输入满足F1为高电平,可以排除四输入的与非门正常工作,下面需要构建TTL反推思想,正确状态F1=0变成Fl=l,74LS138芯片三个输入端口ABC=101时只有对应的Y5输出被选中低电平输出,其余输出都为高电平,对于四输入与非门而言只要万用表测量对应的输入或者74LS138芯片相关的输出有低电平出现就可以找出错误的位置。

3.2 时序逻辑电路测试应用

利用74系列90芯片与相关与非门实现8421码15进制计数器功能。结合74LS90芯片的基本结构分析计数器状态转换如图4所示,逻辑电路图如图5所示,芯片选用了三输入的与非门芯片74LS10和两输入的与非门芯片74LS00,还有两个主控芯片74LS90。

图4为15进制计数器对应的8421码从初始0计数到14的状态转换过程,计数个位的74LS90主控芯片的脉冲信号输入CP0需要外接单次脉冲源或者连续的10HZ以下的脉冲源。下面列举图4画虚线方框的的状态转换过程作为反推实例,其过程类似于组合逻辑电路测试,但计数器属于时序逻辑电路范畴,对于每一个状态的变化需要一个下降沿的触发才会发生改变,复杂程度有所提高。按图5逻辑电路图搭建15进制计数器,正常计数是状态10100到状态00000转变,具体状态变化如图6所示。

如果发生状态10100到状态10101转变,连续给定下降沿脉冲,计数状态持续到10011001后才回到0000()000狀态,实现100进制计数,这时需要关注清零端是否正常工作。15进制计数器从而00000到10100循环转变,由于两个74LS90芯片的清零端R0⑴、R0⑵在出现15这个数时对其进行纳秒级的清零动作,所以查看计数过程中不会出现15这个数。这里需要在状态出现10100时,手动给定一个下降沿脉冲,通过示波器任意通道观察两对串接的清零端R0(l)、R0(2)的电位是否有瞬间高电平脉冲出现,如图7所示,如果没有出现,那么上一级两输入与非门同时出现高电平,找出连接三输入与非门的输出端口,测试当前输入与输出状态下的逻辑功能是否正确,找出错误的位置。

4 结束语

本文结合笔者亲身教学经历,提炼传统的数电实验项目在学生设计与实现过程中经常出现错误,利用TTL逻辑电平反推法去分析实验项目在硬件实现过程中出错的位置,通过反复应用实践,学生可以快速找出线路中存在的问题,在加深了对实验项目的逻辑功能的理解的基础上,进一步提高了对于多种芯片的硬件结构的熟悉,为后续的专业课和创新实践课立下良好的基础。