三维存储芯片堆叠封装技术探研

杨建生

(天水华天科技股份有限公司,甘肃天水741000)

随着便携式电子、航空和军用电子应用等电子系统复杂性的增加,对低功率、质量小和紧密封装技术的要求更多。为了满足这些要求,克服二维(2D)封装局限的3D封装技术越来越多地得到应用。在紧密度方面有了引人注目的进展,整个互连长度更低,寄生特性更低,因而降低了系统功耗。对于硅片封装效率而言(芯片面积对封装面积的比率),从目前MCM封装可得到的硅片效率为20%~90%。然而,与其他2D封装技术相比,3D技术可提供100%的硅片封装效率。尽管3D封装技术能够提供可观的优点,但是对此技术更进一步的推广应用而言,仍存在一些不足。3D封装技术的主要不足在于其工艺复杂性和高封装成本。

按照堆叠类型,有3传统的3D封装技术,即封装堆叠、模块堆叠和裸芯片堆叠。3种封装技术中,裸芯片堆叠封装技术在紧密性、集成密度和电性能方面是最先进的类型。这些技术间主要的差别出现在侧墙绝缘和互连方法,以及在堆叠式封装的侧墙处对功率、接地和信号路径的要求。为了侧墙绝缘,裸芯片堆叠技术后,IBM公司的侧墙互连技术要求硅片蚀刻技术,聚合物介质注入以及侧墙减薄技术。相反,其他公司在裸芯片堆叠技术后,采用导电胶技术在侧墙处进行裸芯片堆叠技术互连I/O。在封装密度、芯片对晶圆的效率以及工艺的复杂性方面,每种技术都有其自身的局限。

因此,与传统的3D裸芯片堆叠封装技术相比,存在更简单、更节约成本的3D封装技术的需求。本文中将论述新研发的3D存储芯片堆叠技术设计、材料体系和工艺流程,并评定其封装可靠性。

1 制造过程

制造过程开始于包含约10个芯片的晶圆分段的侧墙绝缘。最初位于存储芯片中线的I/O焊盘被再分配到侧墙绝缘层,把I/O再分配芯片堆叠到一起,接着在堆叠式模块的聚合物绝缘侧墙处进行互连,最后为下一级组装把焊球粘附到侧墙金属焊盘上。

3D封装制造选择的材料系统为525 μm厚的硅片,25 μm厚的聚酰亚胺膜,作为芯片钝化层。热塑性胶粘剂,为了方便称为TPA-1,作为胶粘剂被涂覆于聚酰亚胺膜上。也选择另一热塑性胶粘剂为侧墙绝缘层,称为TPA-2。其他热塑性胶粘剂,TPA-3用于堆叠芯片。Al和Ti/Cu金属化化合物依次作为I/O再分布和侧墙互连的导线。

1.1 侧墙绝缘

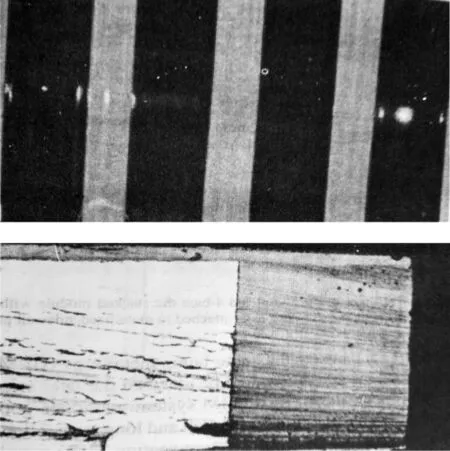

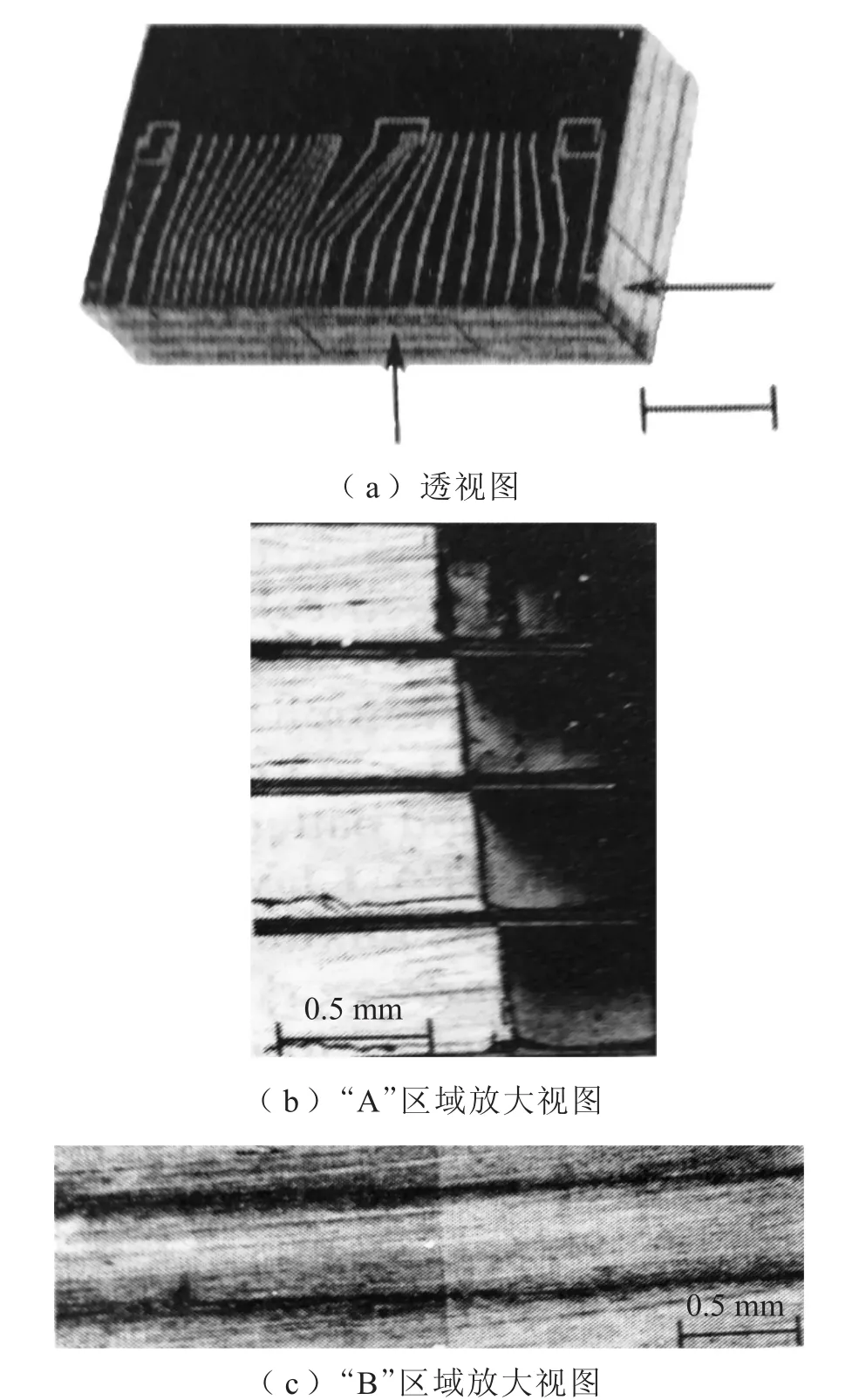

新的3D封装技术的独特特点是在I/O再分布前,完成侧墙绝缘。此工艺过程形成了改进的制造效率,并简化了加工步骤。作为侧墙绝缘的第一步,就是把完全处理的晶圆切割成几个晶圆片段,包含一排或两排芯片。晶圆分割片段后,把与晶圆一样厚的TPA2条带轮流置于涂覆了聚酰亚胺膜的TPA1上,又一涂覆了聚酰亚胺膜的TPA1被置于晶圆片段上,TPA2条为颠倒方式。为了回流TPA1和TPA2,施加热和压力。当样品被冷却,TPA1和TPA2被固化,提供与晶圆片段的强粘附,原因在于它们是热塑性聚合物。图1采用光学显微镜依次示出了侧墙绝缘晶圆片段的俯视图和剖面图。

图1 侧墙绝缘晶圆片段的俯视图和剖面图

1.2 I/O再分布

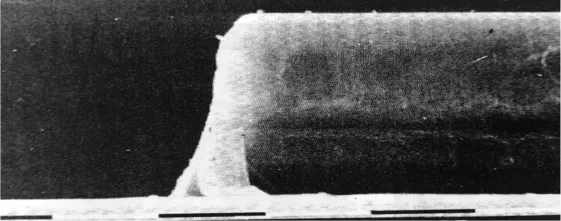

侧墙绝缘层形成后完成I/O再分布。拥有中央I/O焊盘的典型存储芯片不能被直接用于裸芯片堆叠封装制造,因为堆叠式芯片间的电互连应该在堆叠结构的侧墙处完成。因此,要求在芯片堆叠技术工艺之前完成对侧墙的I/O再分布。I/O再分布包括通路口、金属化和图案形成。通路开口于初始I/O焊盘上,是使用O2或O2/CF4气体混合反应离子蚀刻(RIE)通过TPA1层和聚酰亚胺钝化膜形成的。图2示出了通过氧气反应离子蚀刻(O2RIE)穿过聚酰亚胺PI膜和TPA-1层在I/O焊盘上形成的倾斜通路。完成Al金属化和图案形成,以便把初始I/O焊盘互连到绝缘芯片侧墙。因为把再分布的I/O焊盘连接到作为T接合连接的互连金属线的侧墙,推荐厚度大于1 μm的I/O再分布金属焊盘。侧墙绝缘层上的再分布I/O焊盘如图3和图4所示。

图2 由O2RIE形成倾斜的通路

图3 光学显微镜的I/O再分布晶圆分段

图4 在侧墙绝缘层上再分布的I/O焊盘的放大视图

1.3 芯片堆叠技术

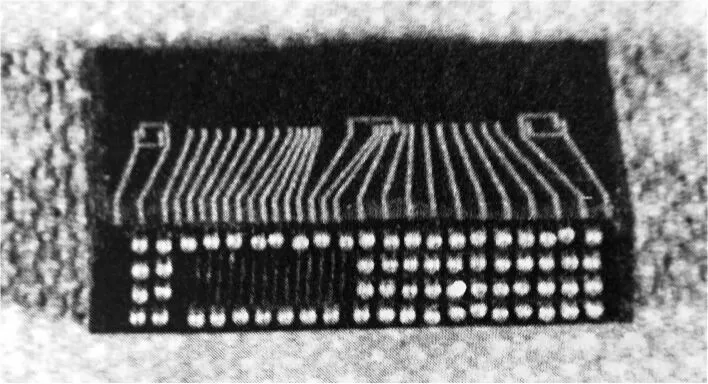

下一步就是沿着Z轴方向堆叠I/O再分布裸芯片。使用金刚石切割片把晶圆片段切割成单个芯片,把4个芯片堆叠到一起形成一个模块。用于芯片堆叠工艺的热塑性胶粘剂(TPA3)提供良好的粘附强度,形成堆叠式模块的高机械完整性。胶粘剂不均匀的涂覆能够在堆叠式芯片之间造成几个空洞或间隙,在侧墙互连上造成穿过芯片的间断的金属化。因此,涂覆在芯片表面上的TPA3胶粘剂应进行回流焊,在芯片堆叠技术工艺期间,随着给定的压力及高于TPA3的Tg温度,完全实现平面化。图5示出了使用TPA3的裸芯片堆叠式模块图,在堆叠式模块中每个芯片相互匹配密切,如图5(b)所示,图5(c)也示出了采用TPA3热塑性胶粘剂后,在芯片之间没有观察到显著的空洞或间隙。

图5 采用TPA3的4芯片堆叠式模块

1.4 侧墙互连

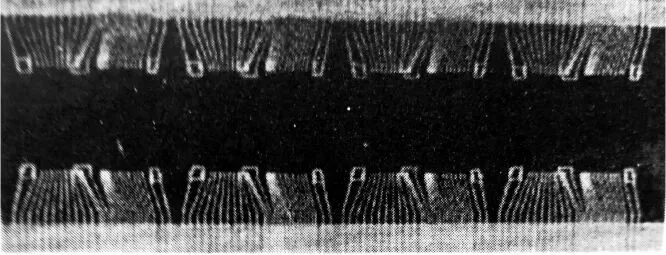

芯片堆叠技术后,完成侧墙互连,把单个的侧墙绝缘芯片进行互连。在堆叠式模块的侧墙上形成功率、接地和信号路径。如前所述,仅仅在芯片堆叠技术工艺后才能完成侧墙互连,是因为在堆叠式模块的侧墙处,暴露的再分布I/O已被TPA1和TPA2聚合物进行电隔离。与其他3D芯片堆叠封装相比,这是新研发的3D封装最独特的特点。Ti/Cu金属化合物可作为侧墙互联技术金属线使用,而且也作为共晶Pb/Sn焊球的凸点下金属化(UBM),将在随后步骤粘附。通过探讨Ti/5 μm Cu UMB体系与共晶Pb/Sn焊球保持良好的粘附性,且具有长期的可靠性。图6示出了4个芯片堆叠式模块的侧墙互连技术Ti/Cu金属图案,虽然把地址、接地、功率和一些控制线进行接合,但数据线和别的控制线没有接合。线宽为100 μm,焊盘为400(μm)2。

图6 4个芯片堆叠式模块侧墙上有图案的金属线

1.5 焊球粘附

3D封装制造的最后步骤,是把焊球粘附到用于下一级封装装配侧墙金属焊盘上。在红外焊料回流焊炉中,把300 μm直径的共晶Pb/Sn焊球粘附到涂覆焊剂的Ti/Cu金属焊盘上。对更好的焊球配准而言,可在表面上提供焊料掩模层。图7示出了整个工艺完成后,3D裸芯片堆叠式封装的原型。

图7 已完成的4个裸芯片堆叠式模块的原型

2 独有的特点

新开发的3D裸芯片堆叠式封装技术比传统的3D封装技术所独有的特点。

2.1 高密度封装

3D封装技术可分为三组封装类型:封装堆叠技术、模块堆叠技术和裸芯片堆叠封装技术。按照硅片效率和电性能,裸芯片封装技术比其他两种技术优越。研发的3D裸芯片封装技术比其他两种3D封装技术或传统2D封装技术尺寸更小,集成密度更高。

2.2 工艺简化

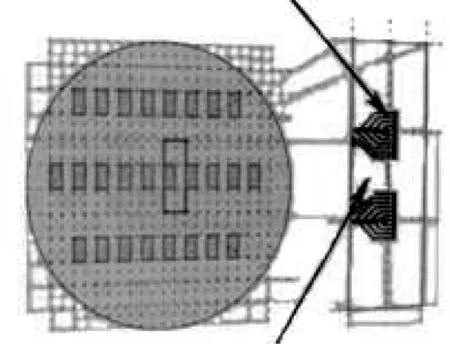

全面推广3D封装技术的主要挑战之一是由于其工艺复杂性,制造成本高。图8和图9简图依次示出了按照IBM公司的设计和本次新研发设计,适于侧墙绝缘技术及对芯片边缘线再分布初始的I/O的两种不同方法。对IBM公司技术而言,在任何绝缘层形成工艺前,把再分布I/O焊盘置于邻近的芯片上。因此,需要增加几个步骤,诸如硅片蚀刻,聚合物介质注入,以及在侧墙互连前为了对I/O焊盘进行电隔离需要的侧墙平面化。相反,如前所述,在新开发的3D封装设计中,在I/O再分布前,可易于形成侧墙绝缘层。再者,侧墙绝缘层处的再分布I/O焊盘已被进行电隔离。因此,裸芯片堆叠技术后,对侧墙互连不要求增加处理步骤,与传统的方法相比,制造工艺更加简易。

图8 IBM公司设计的I/O再分布方法,每个片段包含6个芯体,只有一个芯体可应用于3D封装制造

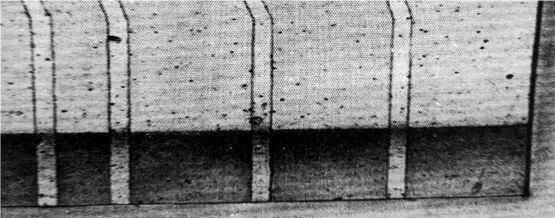

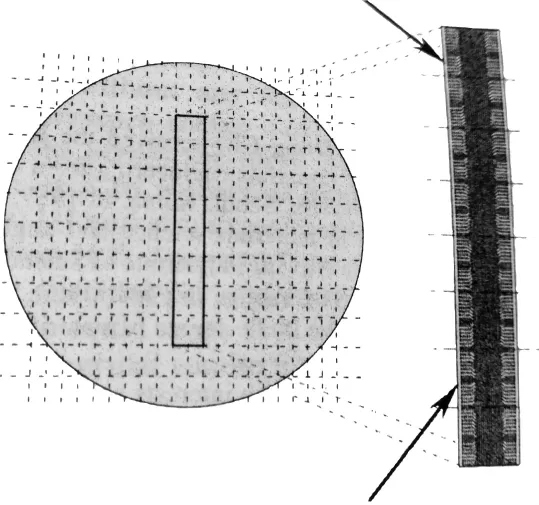

2.3 芯片对晶圆片更好的效率

根据IBM公司的技术,每个包含6个芯体的片段只有一个芯体,可用于3D封装制造。这是因为如简图8所示,在邻近芯体上形成再分布I/O焊盘。另一方面,新研发的3D封装在侧墙绝缘层上构成了再分布I/O焊盘。因此,晶圆片中的所有芯片可用于制造如图9所示的3D封装,在芯片对晶圆效率方面取得显著进展。

图9 按照新研发的3D封装的I/O再分布方法,在加工的晶圆中所有的芯片都可用于3D封装制造

3 可靠性试验

在3D裸芯片堆叠封装原型上,进行JEDECⅢ级试验和高温/高湿度(85℃/85%)试验。完成这些可靠性试验,以便验证已选择的材料体系和单元工艺状况,以及证明3D裸芯片堆叠封装的结构完整性。

3.1 JEDECⅢ级试验

JEDECⅢ级试验条件为30℃/60%RH/196 h,接着高于183℃的IR回流焊达1.5 min。进行光学显微镜检查,为的是检查试验后的机械失效或退化。在JEDECⅢ级试验后,未发现显著分层现象或结构变化。

3.2 高温/高湿度试验

采用85℃/85%RH/720 h的高温/高湿度试验,来研究该封装的机械可靠性,发现该试验样品的90%以上保持机械完整性。

4 结束语

已确立了一种新的3D裸芯片堆叠封装,具有更简易的工艺步骤和更好的芯片对晶圆效率。采用机械芯片的3D存储芯片堆叠封装的原型,已成功地进行验证。3D裸芯片堆叠封装技术的制造工艺为:

(1)把晶圆切割成为芯片片段;

(2)采用聚合物层压的芯片侧墙绝缘;

(3)在初始I/O焊盘上的通路孔;

(4)从中心焊盘到侧墙绝缘层的I/O再分布;

(5)采用聚合物胶粘剂的芯片堆叠技术;

(6)侧墙金属化和图案形成;

(7)焊球粘附。

该新研发的封装设计的最独特特点是在I/O再分布前进行侧墙绝缘,这样取得如下优点:

(1)更好的芯片对晶圆的效率;

(2)在随后的制造步骤中,显著的工艺过程简化。

通过采用该新的3D设计,传统晶圆上的所有芯片可用于3D裸芯片堆叠封装制造,而不存在与侧墙I/O再分布相关的邻近芯片损失。再者,该设计能够简化下列工艺过程诸如I/O再分布、侧墙绝缘、侧墙互连和封装成形。

3-D裸芯片堆叠封装原型的机械完整性,满足IEDECⅢ级和85℃/85%试验要求。

[1]S.F.Al-sarawi,D.Abbott,and P.D.Franzon.A review of 3-D packaging technology.IEEE Trans.Comp.,Packag.,Manufact.Technol[J].Institute of Electrical&Electronics Engineers,Inc.,1998,(Feb):2-14.

[2]中国电子学会生产技术学分会丛书编委会组编.微电子封装技术[M].第1版.北京:中国科学技术大学出版社,2003,267-278.

[3]电子封装技术丛书编委会编.集成电路封装试验手册[M].第1版.北京:电子工业出版社,1998,99-108.