基于图像匹配算法的高性能专用集成电路设计方法

陈家豪

摘要

图像配准是图像解决策略的问题,是同一场景多图像研究的基础,是最近这些年来的最先进的图像解决本领之一,基于域改变的图像配准应用是最基本的傅里叶改变。这考虑了硬件实现的重要价值和现实的重要性。介绍了一种用于图像匹配算法的独特硬件集成电路(ASIC)。这种独特的ASIC电路易于构建,易于级联,也易于流动,适用于内置的实时图像匹配。

【关键词】图像匹配 专用集成电路 设计

1 引言

在过去的50年里,现代微电子技术取得了长足的发展,它一直在持续促进信息科学的发展,带来了人类生活的巨大改变,同时也为生命科学领域的信息化提供了技术层面的坚实基础和有力保障。随着科学技术的快速进步,这一作用变得十分的关键。提高图像匹配的实时性能大大增强它的应用价值。模板匹配法是解决图像匹配的主要方法之一。人类能够得到各种信息,一般都是从视觉,听觉,触觉等模式得到,但绝大部分是来自于视觉所接受的图像信息,视觉是人類重要的感知手段,而那个图像是视觉的基础。图像匹配是推算集中型的,其数据和推算繁琐性特别大,因此,在嵌入式应用中提高图像匹配的实时性有很大的难度,工程师必须要持续研究和建立新的技术。

2 图像匹配策略

DSP将参考图写入参考图存储器并在预初始化处理期间得到参考图的每个子图的均值和均方根。当执行图像匹配时,DSP首先找到实时图的均值和均方根,然后使用卷积2来找到卷积。最后,DSP找到彼此关值并将它们进行对比以找到对应于最大相互关值的子图坐标(u,v)。一般来讲,当卷积通过卷积完成时,系统的卷积适用于图像匹配算法,因此它拥有专业性,并且嵌入式系统的卷积大小远远小于图像像素的数量。于是,有必要将实时图和参考图子图划分为适当的分子图。分割模式与图像的大小和系统卷积的比例相关。假设36×36的实时图仅匹配系统中的一个ASIC,则实时图可以分为36个1×36分子图。通过这种方式,当组装时,DSP开始将实时图的第一行从实时图存储器写入ASIC实时图,然后不断读取基准图数据以获取分子的每个具体图的第一批。然后,DSP将实时图的第二行从实时图存储器写入人体卷积装置的实时图寄存器,然后再不断的读取参考图,第二批每个分子图卷积和第一批相关的分子图,卷积被添加。

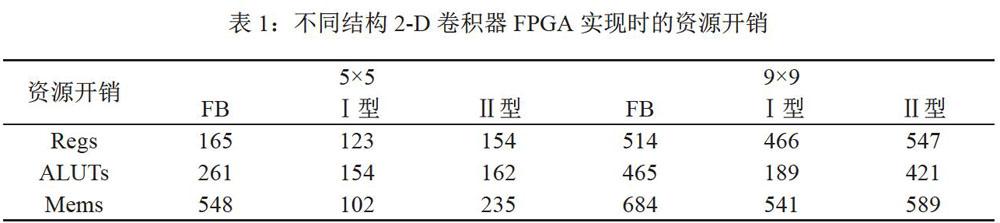

表1显示了FPGA完成的各种结构所消耗的资源,通过寄存器资源,组合逻辑,存储器大小和乘法器数量来衡量。

图1显示了模板卷积下的这些关系。可以看出,当W足够大时,吞吐率收敛到1,并且此时损耗的中间结果存储器容量相对推广。

3 ASIC结构设计

在规划完好的定制ASIC时,规划器定义芯片上全部晶体管的几何和工艺规则,最后将策划好的结果传递给ic制造商。中央控制器控制ASIC的不同模块的数据安排,计算过程和容错处理。通过这种方式,芯片可以实现最佳性能,即高面积效率,高速度和低功耗。然而,策划周期通常很长,并且芯片的价格很高昂。假设策划失败,通常会导致大量时间和成本的白费。ASIC自定义部分策划模式基于预先构建的安装门。芯片上只有接触孔,互连和过孔根据电路的效用特意设计和制造的。用户按照用户定义的效用根据特定模式进行匹配。用户的电子工程师可以选择器件资源,例如NAND门,触发器,缓冲器,RAM单元和阵列内的互连线,以形成自己的逻辑设计。在半定制方案中,有门阵列方案模式和标准单元方案模式,并且运用每个库单元。可编程不同的可编程ASIC,现场可编程初始阵列,低密度,逻辑/通用20引脚通用逻辑阵列。图2显示的是转换增益测试的模拟结果指数。

4 结论

总之,卷积器2图像匹配算法方便,易于定位,延迟小,易于并行流动,并且易于通过级联改善实时图像匹配。本文基于多通道与大模板并行匹配的特点,提议了基于NCC算法的多通道大模板匹配ASIC结构,实现了芯片的前端工艺策划。此外,在改进半导体工艺技术之后,当扩展规模时,卷积器2只需增加基本卷积单元的数量,于是策划的工作量很小并且上市的时间也很短。所以,它是一种理想的图像匹配专用ASIC,它在嵌入式图像匹配的实时体系中具有很高的实际应用价值。一种用于图像匹配最大彼此相关的特殊ASIC完成模式是一种轻松可行的模式,其拥有着非常优越的发展前景。能够完全建立出与C6000系列高性能DSP相当的紧凑,低成本,高速卷积,处理器。

参考文献

[1]张遂南,黄士坦.一种面向图像匹配算法的高性能专用集成电路设计[J].北京师范大学学报(自然科学版),2002,38(01):48-52.

[2]刘海鹰,彭思龙.基于非张量积小波的大范围图像匹配方法[J].模式识别与人工智能,1999(01):67-73.