双相机高速交替成像时序控制系统*

郝锐敏, 丛 聪, 张 斌, 赵冬娥

(中北大学 信息与通信工程学院, 山西 太原 030051)

研究战斗部破片的空间分布规律是评估破片毁伤性能的重要手段, 传统的测试方法大体分为接触式测试法与非接触式测试法[1]. 接触式测试法主要是靶板法, 该方法简单直观, 但是测试精度低、 可靠性差, 已经不适应当今的高精度测试要求. 非接触法例如光电管阵列测量靶、 4光幕靶、 声靶等也都存在各自的问题与局限性[2]. 近年来, 高速相机交替测量法已经成功应用于弹丸、 破片的空间坐标测试中, 此方法具有精度高、 实时性高等优点[3]. 而高速相机作为测量系统的核心, 其工作状态显得尤为重要, 在此提出一种可以精确控制双相机高速交替成像的脉宽可调、 时延可调的时序脉冲产生系统.

1 双相机工作原理

将两台相机放置于垂直于地面的平面, 调整相机位置, 使两台相机的视场交汇, 这样就形成了测试系统的靶面, 通过时序控制电路控制两台相机进行交替拍摄, 当目标通过靶面时, 两台相机就会连续对目标进行拍摄, 获得图像信息[4].

1.1 相机特性

设计中所用相机为DALSA公司的线阵相机Piranha4, 相机分辨率为4k, 像素尺寸为10.56 μm×10.56 μm, 具有高灵敏度、 低读出噪声、 高动态范围、 高行频的特点, 在TDI模式最高行频达100 kHz, 面阵模式最高行频可达200 kHz[5].

1.2 相机工作模式

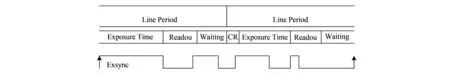

相机曝光模式由触发事件控制. 触发事件包括相机内部控制下的内触发模式, 外部同步信号控制曝光的外部触发, 计算机发送命令的软触发. 设计中通过外触发方式触发相机, 在该模式下, 外部触发信号控制行周期和曝光时间. 在时序控制信号的上升沿开始曝光, 下降沿时开始进行像素转移, 时序脉冲的高电平持续时间即为曝光时间, 脉宽最小为2 μs. 在像素读出期间, 触发信号的下降沿无效. 外触发时序图见图 1.

图 1 外触发时序图Fig.1 Sequence diagram of external triggering

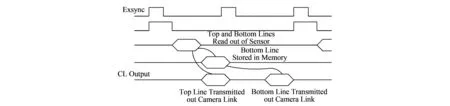

对于P4相机, 面阵模式下的数据率可以达到最大. 当相机处于面阵模式时, 相机芯片的两条线同时曝光. 在触发脉冲的第一个上升沿时, 两行线同时曝光并且数据从芯片中读出. 其中一行数据直接由CameraLink数据输出, 另一行数据暂时存储在相机缓冲区中. 下一个触发脉冲信号并不会触发芯片曝光, 而是用于让存储在缓存区中的数据由CameraLink口输出[6]. 面阵模式时序图见图 2.

图 2 面阵模式时序图Fig.2 Sequence diagram of area mode

2 FPGA设计

设计选取的FPGA芯片为Xilinx公司的XC6SLX9芯片, 芯片采用45 nm工艺节点, 显著降低了静态、 动态和I/O功耗, 具有专用的时钟布线, 优化的逻辑架构通过使用双寄存器6输入查找表(LUT)结构能够最大限度地降低所需的逻辑电平, 从而减少延迟并将系统吞吐量提升达25%之多[7].

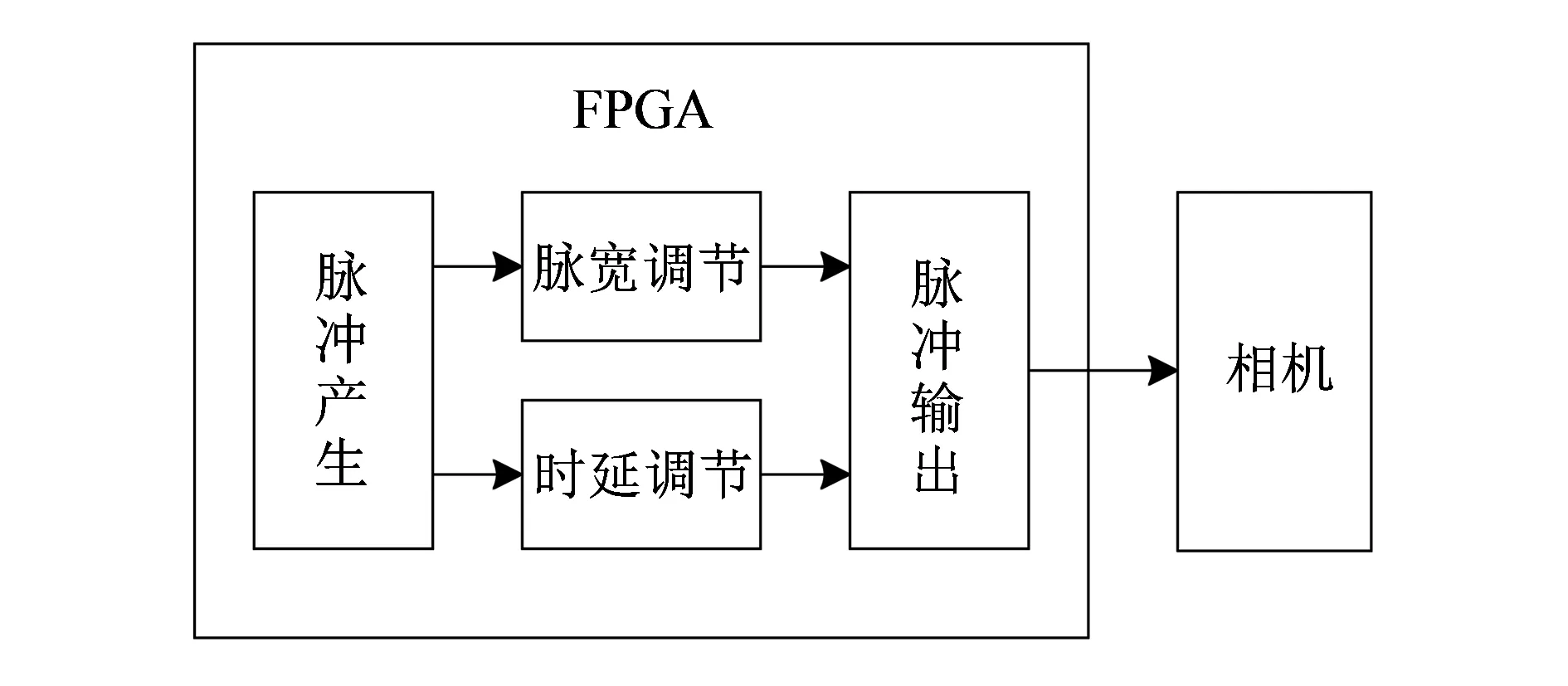

2.1 系统框图及FPGA信号功能表

时序脉冲产生系统总共由3部分组成, 分别是脉冲产生部分、 脉宽调节部分及时延调节部分. 系统总体组成框图如图 3 所示.

FPGA程序中用到的信号如表 1 所示.

图 3 系统组成框图Fig.3 Block diagram of system

2.2 时序设计

为了使相机工作在最高行频200 kHz下, 设计两路频率均为200 kHz的周期脉冲, 同时又要满足相机最小曝光时间2 μs, 设计脉宽范围为2~4 μs.

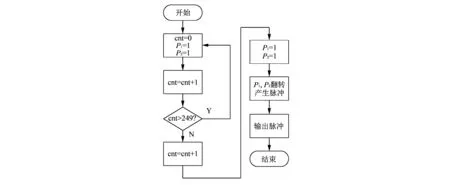

在FPGA内部定义两个计数器, 计数器按照时钟频率进行计数, 由于FPGA芯片的工作频率为外部晶振提供的50 MHz, 则计数器总共需要计250个周期才能产生200 kHz的脉冲, 计数器从0开始计数, 当计数值达到249之后, 计数器重新置0开始新一轮计数, 以此不断地产生200 kHz的脉冲, 每50个计数周期对应时间为1 μs, 令p1_out、 p2_out在0~99之间值为1, 100~249之间值为0, 则可以产生脉宽为2 μs周期为5 μs的两路脉冲, 同理, 可以实现脉宽为3 μs, 4 μs的脉冲[8-9]. 脉冲产生流程见图 4.

图 4 脉冲产生流程图Fig.4 Flow chart of pulse generation

2.3 时延设计

为了使相机实现先后交替的拍摄, 在两路脉冲之间设计了时延. 脉冲周期为5 μs, 所以两路脉冲之间的时延必须小于5 μs才能保证一台相机在完成一次曝光之后且在第二次曝光还没有开始之前另一台相机可以完成曝光.

在两路脉冲之间定义计数器, 对应时间从2~4 μs, 当时延计数器计数完成之后, 第二路脉冲的计数器开始计数, 这样, 第二路脉冲的产生较第一路脉冲就会有2~4 μs的时延[10].

2.4 按键设计

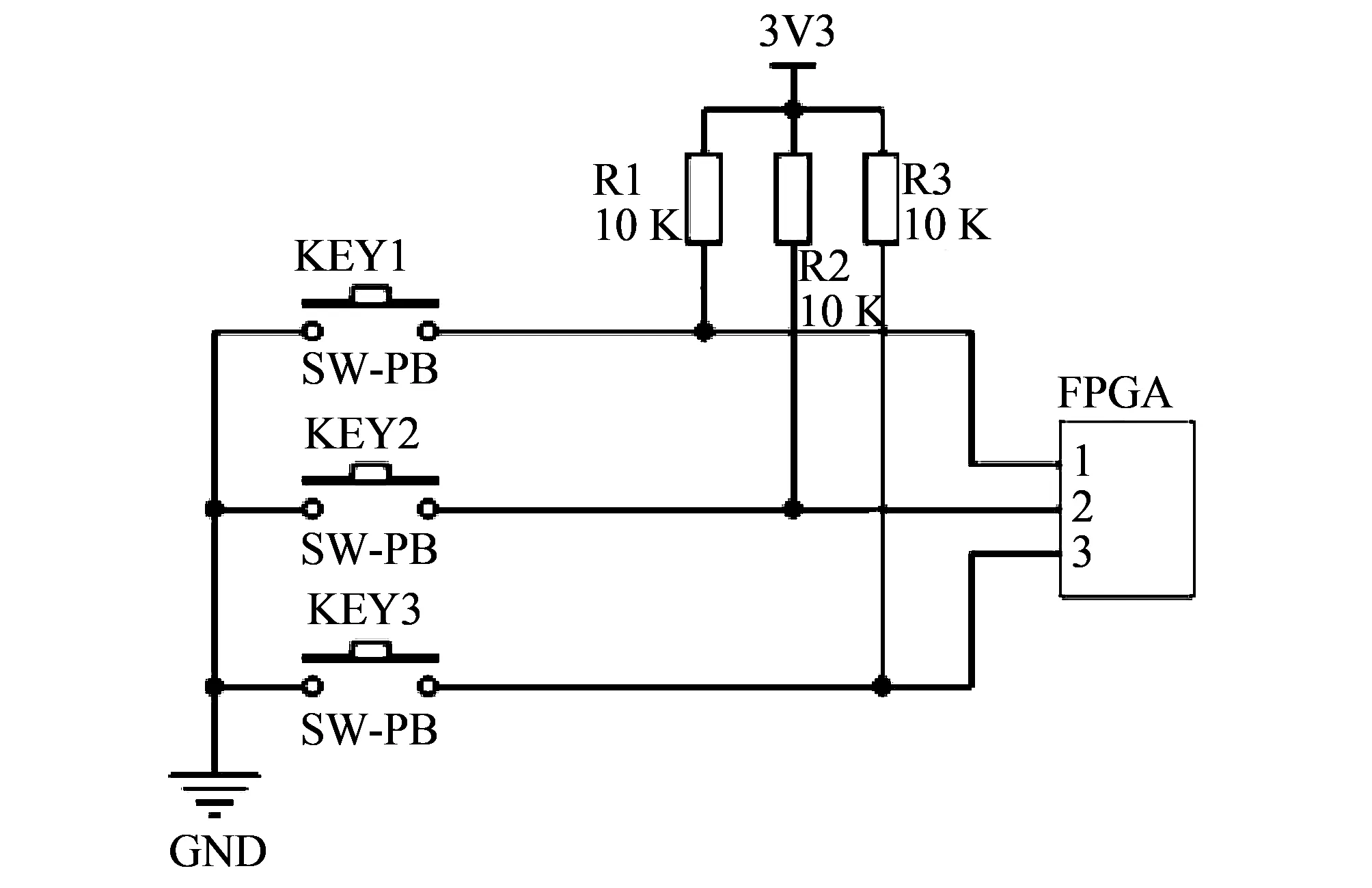

为了方便对输出脉冲参数的实时调节, 外加了一块按键电路, 通过按键电路可以对两路脉冲的脉宽及时延进行调节, 脉宽、 时延的调节范围均为2~4 μs, 保证两台相机随时都处于交替拍摄的状态.

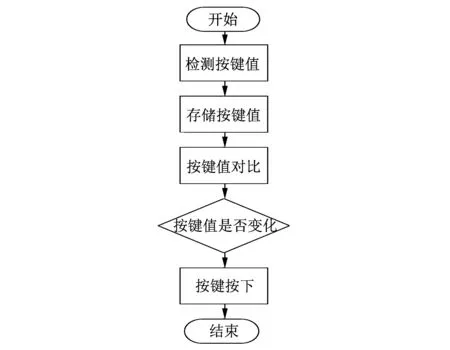

在FPGA程序中利用边沿检测法的原理对按键值进行检测. 通过按键在未按下时为高电平, 对应值为1; 按下之后为低电平, 对应值为0, 由此与FPGA程序相对应[11]. 物理按键存在按键抖动的现象, 且抖动时间一般在10~20 ms, 所以利用时钟的上升沿每隔20 ms对按键值进行一次检测, 将检测到的按键值存储到相应寄存器中, 并对前后两次存储的按键值进行比较, 若前后两次的按键值不同则说明按键存在抖动, 检测到的值并不是真实的按键值; 若前后两次的值均为0则表示按键确实被按下; 若前后两次的值均为1, 则表示按键没有被按下[12]. 在程序中, 按键值存储寄存器key[1], key[2]发生1到0的变化, 则按键1、 按键2被按下, 每次按键1、 按键2被按下时, 对应脉冲的脉宽都会以1 μs为单位递增, 直到达到其上限值5 μs, 脉宽会重新返回初始值; 同理, 按键3被按下时, 两路脉冲之间的时延以1 μs为单位递增, 达到上限值之后返回时延初始值. 按键电路见图 5. 按键设计流程见图 6.

图 5 按键电路图Fig.5 Diagram of key circuit

图 6 按键设计流程图Fig.6 Flow chart of key design

3 实验结果

3.1 软件仿真结果

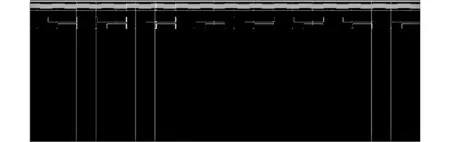

图 7 仿真波形图Fig.7 Simulation waveform

在ISE里完成程序编写并编译通过后, 编写测试文件, 调用Modelsim对程序进行仿真, 观察波形, 图 7 中第1行灰色部分为时钟信号, 由于时钟信号频率过高, 所以在图中并不能看到时钟的波形, 第2行与第3行分别为第1路脉冲与第2路脉冲的波形, 为了方便观察, 在Modelsim的波形界面添加两条分别对齐波形上升沿的时间光标, 通过光标显示第一条光标时刻为30 μs, 第二条时间光标的时刻为35 μs, 则波形的周期为5 μs, 频率为200 kHz, 再添加一条对齐第二个脉冲上升沿的光标, 此光标时刻为33 μs, 可知第二路脉冲比第一路脉冲延迟了3 μs, 验证了脉冲频率及两路脉冲交替关系的正确性. 仿真波形如图 7 所示.

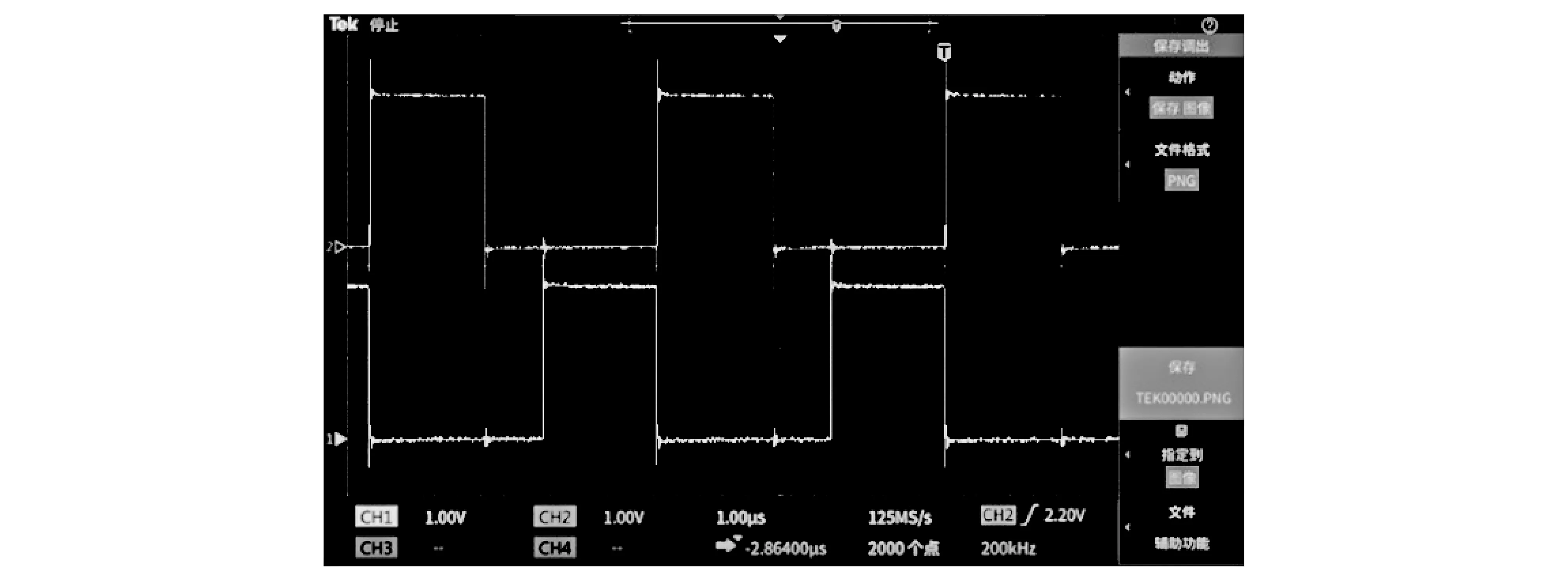

3.2 示波器显示结果

在ISE中编写管脚约束、 时序约束文件, 进行布局布线之后将程序通过JTAG下载到FPGA芯片中, 连接示波器, 由示波器显示可知两路脉冲为200 kHz, 初始脉宽为2 μs, 时延为3 μs, 验证了脉冲频率及交替的正确性. 示波器波形见图 8.

图 8 示波器显示波形图Fig.8 Waveform of oscilloscope displaying

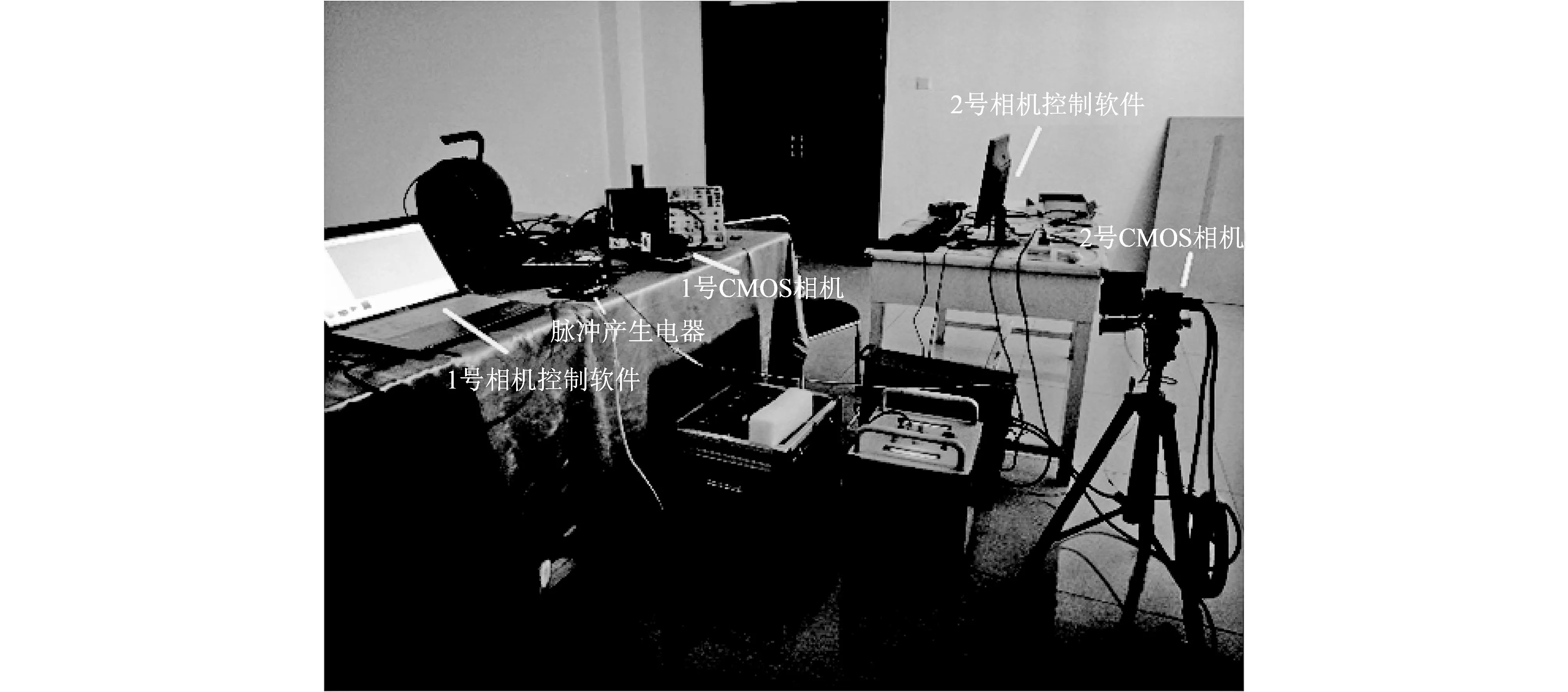

3.3 相机拍摄结果

通过时序控制电路控制两台相机进行拍摄, 1号脉冲的脉宽为2 μs, 2号脉冲的脉宽同样为2 μs, 两路脉冲之间时延为3 μs, 保证1号相机曝光完成之后, 2号相机再进行曝光, 如此交替地进行连续拍摄. 调整后的脉冲由示波器显示波形可知其正确性. 拍摄完成后, 通过两台相机的控制软件可知, 一号相机在3 s内拍摄了600 000帧图片, 每秒拍摄200 000帧, 计算可知其拍摄频率为200 kHz; 二号相机拍摄设定的240 000帧图像的速率为每秒200 000帧, 则2号相机的工作频率同样为200 kHz, 证明两台相机在200 kHz的工作频率下进行了连续交替的拍摄. 搭建的实验系统如图 9, 相机拍摄结果如图 10 与图 11.

图 9 实验系统图Fig.9 Diagram of experiment system

图 10 一号相机拍摄结果图Fig.10 Diagram of NO.1 camera shooting result

图 11 二号相机拍摄结果图Fig.11 Diagram of NO.2 camera shooting result

4 结 论

本文提出一种基于FPGA实现的脉冲参数可调节时序控制电路并对相机进行控制. 了解了相机曝光时间、 工作频率等关键性能参数, 分析了相机外触发模式及面阵模式的工作原理; 详细阐述了基于FPGA的脉冲产生、 时延可调、 脉宽可调及按键扫描的设计思路; 结合仿真及实际实验结果, 验证了该方法的可行性.

[1] 徐菲. 毁伤威力场测试系统软件关键技术研究[D]. 太原: 中北大学, 2013.

[2] 陈君, 苏健军, 刘吉, 等. 主动照明双相机交汇法破片空间坐标测试系统研究[J]. 科学技术与工程, 2017(7): 173-176, 187.

Chen Jun, Su Jianjun, Liu Ji, et al. Fragment the space coordinate testing system based on active lighting double camera intersection method[J]. Science Technology and Engineering, 2017(7): 173-176, 187. (in Chinese)

[3] Jiang Baotan, Pan Zhibin, Qiu Yuehong. Study on the key technologies of a high-speed CMOS camera[J]. Optik International Journal for Light and Electron Optics, 2017, 129: 100-107.

[4] Ignacio B, Javier B, Alfredo G, et al. Efficient smart CMOS camera based on FPGAs oriented to embedded image processing[J]. Sensors, 2011, 11(3): 2282-2303.

[5] Teledyne DALSA发布全新高速Piranha4相机系列[J]. 电子与电脑, 2011(11): 75.

Teledyne DALSA releases a new high-speed Piranha4 camera series[J]. Electronic and Computer, 2011(11): 75. (in Chinese)

[6] Chao Zhujun, Chen Liyong, Kui Jiaoying, et al. Image acquisition system design of camera based on FPGA[J]. Applied Mechanicsand Materials, 2015, 3590(668): 836-839.

[7] 邹虹, 纪龙蛰, 邢园丁, 等. 基于FPGA多模时间同步触发系统的研究与设计[J]. 测试技术学报, 2016, 30(2): 114-119.

Zhou Hong, Ji Long Zhe, Xing Yuan Ding, et al. Research and design of multi-mode time synchronization triggering system based on FPGA[J]. Journal of Test And Measurement Technology, 2016, 30(2): 114-119. (in Chinese)

[8] 黄磊, 李自田, 孟楠, 等. 高帧频CCD图像传感器驱动时序设计[J]. 电子器件, 2009(2): 262-264, 268.

Huang Lei, Li Zitian, Meng Nan, et al. Design for CCD image sensor schedule generator with high frame rate[J]. Chinese Journal of Electron Devices, 2009(2): 262-264, 268. (in Chinese)

[9] 李超, 刘树昌, 刘鹏, 等. 外触发方式下相机同步抓拍系统研究[J]. 测试技术学报, 2014, 28(4): 339-344.

Li Chao, Liu Shuchang, Liu Peng, et al. Research of camera synchronous capture system under exteral trigger mode[J]. Journal of Test and Measurement Technology, 2014, 28(4): 339-344. (in Chinese)

[10] 姬先举, 温志渝. 基于CPLD的光积分时间可调线阵CCD驱动电路设计[J]. 传感器技术学报, 2006(5): 1781-1784.

Ji Xianju, Wen Zhiyu. Design of linear CCD driving circuit with tunable integration time based on the CPLD[J]. Chinese Journal of Sensor and Actuators, 2006(5): 1781-1784. (in Chinese)

[11] 王晓磊. 数字电路解决按键抖动的问题[J]. 民营科技, 2011(8): 35.

Wang Xiaolei. The problem of solving key jitter of digital circuit[J]. Private Technology, 2011(8): 35. (in Chinese)

[12] 谷长龙, 李小英. 基于FPGA器件的消除按键抖动方法研究[J]. 吉林化工学院学报, 2006(3): 53-55.

Gu Changlong, Li Xiaoying. Methods of eliminating the jitter of keys based on FPGA devices[J]. Journal Of Jilin Institute of Chemical Technology, 2006(3): 53-55. (in Chinese)