基于FPGA的远程心电监护数据AES加密

岑小林+陈援峰+杨伟钧

摘要

本文简单回顾了加密技术的发展,提出远程心电监护数据的加密问题,探讨了在FPGA上实现监护数据的AES加密,重点讨论了S盒变换及密钥扩展两个模块。探讨了在有限资源的FPGA型号上怎样节约资源进行设计,提出为了节约芯片面积,进一步的研究应该以s盒的非查表方式实现为方向。

【关键词】AES S盒 FPGA ECG

远程心电监护系统的数据通过实时记录方式取得之后需要通过有线或无线网络上传数据到服务器。个人的心电数据反应个人身体健康状况,属于个人隐私应当进行保护。而目前通过心电数据采集端获得的数据一般没有经过任何信息隐藏处理,一旦泄露可能对个人造成不良影响,因此这些信息的安全性方面有待提高。

利用密钥对数据进行加密的算法基本可以分为对称密码、非对称密码和杂凑算法。对称密码一般使用相同的密钥,又可分两种类型:a、分组密码;b、序列密码。2002年美国国家标准与技术研究院为了取代被破解的DES算法发布的AES(高级加密标准)采用分组密码体制。

AES算法的密钥长度支持128比特、192比特、和256比特三种,其中分组长度为128比特的算法比较容易在硬件平台上实现。硬件电路实现方式一种是使用半定制的FPGA实现,另一种是使用全定制的ASIC实现。后者速度更快,能更好的满足心电监护的实时性要求,但是成本高昂。

AES-128算法每次将128bit的明文和128bit的密钥经过10轮迭代产生128bit密文。每一轮迭代又分为字节替换(Sub Bytes),行位移(Shift Rows),列混清(Mix-columns)以及轮密钥加(Add Round Key)这几个步骤。

1整体设计

AES加密核整体上按照如图1架构进行设计。

包含一个控制逻辑模块,密钥扩展模块,一个初始化序列模块,一个结束序列模块,一个轮变换模块。其中轮变换模块包含了10次迭代。一次128bit字节的加密可以在12个时钟周期内完成(10个周期用于10轮循环,1个时钟周期用于初始化密钥扩展,1个时钟周期用于输出阶段)。

前级输出经过压缩的ECG数据,同时给AES加密模块控制器一个触发信号,加密核接收到信号,会在ECG明文输入和密钥总线上分别采样128bit明文和密钥。通过加密核的运算,在12个时钟周期后,AES加密核会将完成管脚信号拉高,告诉外部加密完成,后级可以根据该信号的完成情况来读出密文数据使用。

AES算法FPGA实现中将最常用的S盒变换、列变换、密钥扩展模块分别放在单独的文件中实现,把行移位模块放在顶层实现代码中集合实现。加密核顶层包含密钥扩展模块以及S盒模块文件。同时还在顶层模块内实现控制逻辑,以及初始化序列、轮变换、结束序列。子密钥生成模块中调用了行异或(Rcon)模块和S盒模块,用于生成各个轮变换需要的子密钥。

2S-盒变换及其实现

字节变换也叫做S-盒变换,该变换是非线性变换,在有限域GF(28)下进行操作。完整的有限域的概念涉及到近代数学中群的概念,这里不试图阐述清楚复杂的数学概念,浅显地理解为一个集合及在其上定义的一些运算。有限域GF(28)只包含0到255这256个不同的数,可以由一个字节表示。在AES算法中需灵活变换数据的表示形式,比如二进制、十进制、十六进制及多项式表示法。比如10100011可以表示成如下多项式,如果是GF(2)域,则x=2。

通过文献[1]知,定义了相应的加法乘法运算来保证运算结果也处于GF(28)域内。一种浅显直接的S盒变换描述就是在有限域GF(28)下求逆,然后作仿射矩阵变换和与0×63的加法运。

所以第一步是求逆,求0到255这所有256个数的逆,这里的求逆要用到前面提到的多项式表达形式和多项式乘法运算。比如任意取一个数152∈GF(28),通过循环地与0到255中的数做多项式乘法,再与283做模运算,得到其逆为42(283是AES算法中的一个不可约多项式)。

第二步是将42与仿射变换矩阵相乘然后加上0×63,也可以用如下的公式计算得到相同的結果:

31、257都是常数,99即常数0×63。42经过计算得到70,此即152在S盒中的对应值。由此可以形成一个S盒数值表,很多文献中都列出了这个表,这里就不复赘述。

在FPGA中实现时,并不需要进行上述的运算,而是将己经计算出的表存入FPGA中,共计16x16=256个值。当进行S变换时,根据数值到表中的对应位置取值即可获得S盒变换的值。但是,查表的方法会消耗较多的FPGA芯片资源(主要是内存RAM资源),根据文献3的计算,采用256个8bit的ROM来存放S盒矩阵,考虑并行计算需要采用16组S盒变换同时进行,另考虑在密钥扩展的计算中,需要S盒变换4组,单轮需要内存为20×256×8bit,而一次加解密运算在AES-128算法中需要使用10轮变换,在反馈模式下需要10×20×256×8bit。

3密钥扩展及其实现

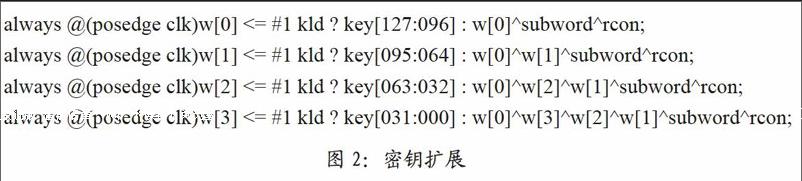

密钥扩展的功能是产生加解密运算每一轮计算过程中所需要的轮密钥。密钥按矩阵的行进行分组,添加40个新行来进行扩充。其中每四行组成128bit子密钥提交给相应的轮变换。其中后续新行的产生分两种情况,简单情况下如果行号不是4的倍数,只需将该行之前一行与行号减4后所在行做异或运算即可,如果行号是4的倍数则需做旋转、替换之后再异或,具体的扩展说明可以借用文献1当中的一副图加以说明,如图2所示。

此模块的核心代码如下所示:其中kid是用来控制是否为初始密钥的信号量,Key即为初始密钥。

4总结

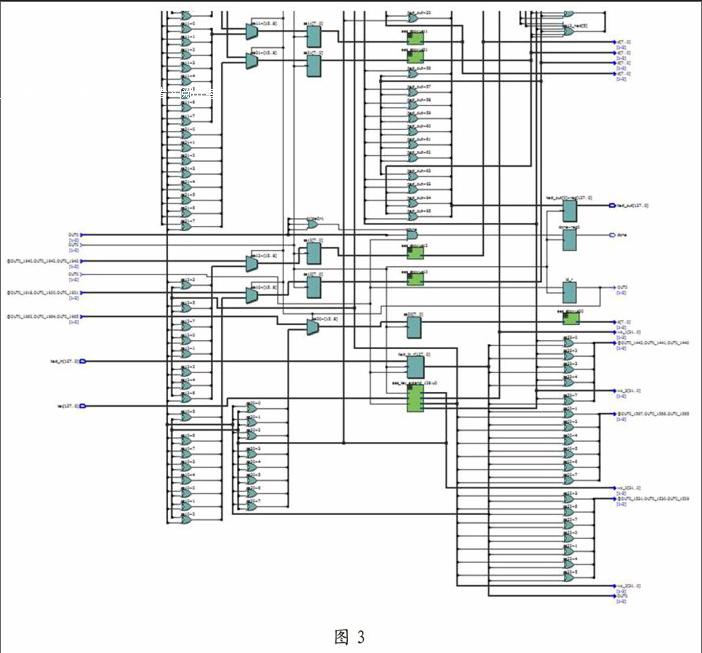

实验在QuartusⅡ15.0当中选择使用EP4CE30系列芯片。在与ECG处理模块综合后,可以避免引脚数不够的问题,但是LE单元则需要进一步改进算法才能切实减少使用量。经过综合之后得到的RTL视图如图3所示。

本文没有深入阐述AES算法的数学原理,简单介绍了其中S盒变换及密钥扩展两个环节,说明了一些FPGA中实现的技术问题和方法。AES算法作为一种目前广泛使用的可靠加密算法,嵌入在FPGA或ASIC中进行运用仍有一定的发展空间。今后可能的深入研究包括怎样使用高效的直接计算的方法实现S盒变换,怎样将AES算法与近年新开发的加密算法结合以增强加密系统的抗攻击能力等等。

参考文献

[1]Ma11ab Implementation of the Advanced Encryption Standard,Jorg J.Buchholz,http://buchholz.hs-bremen.de,2001.11.

[2]Simple AES(Rijndael)IP Core,http://opencores.org/project,aes_core,2013.

[3]杨帆.AES算法研究及FPGA实现[D].北京:北京工业大学,2014.endprint